### A CNN/MLP NEURAL PROCESSING ENGINE, POWERED BY NOVEL TEMPORAL-CARRY-DEFERRING MACS

by

Ali Mirzaeian A Dissertation Submitted to the Graduate Faculty of George Mason University In Partial fulfillment of The Requirements for the Degree of Doctor of Philosophy Computer Engineering

Committee:

Monson /d K

Date: \_\_\_\_\_

Dr. Avesta Sasan, Dissertation Director

Dr. Zhi Tian, Committee Member

Dr. Liang Zhao, Committee Member

Dr. Sai Manoj Pudukotai Dinakarrao, Committee Member

Dr. Monson Hayes, Department Chair

Dr. Kenneth S. Ball, Dean, The Volgenau School of Engineering

Summer 2021 George Mason University Fairfax, VA

## Neuromorphic Hardware Design for Executing Deep Neural Networks on Low Power and Limited Resource Infrastructures

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

By

Ali Mirzaeian Master of Science Iran University of Science and Technology (IUST), 2015 Bachelor of Science Isfahan University of Technology (IUT), 2012

Director: Dr. Avesta Sasan, Professor Department of Electrical and Computer Engineering (ECE)

> Summer 2021 George Mason University Fairfax, VA

$\begin{array}{c} \mbox{Copyright} \textcircled{O} \mbox{ 2021 by Ali Mirzaeian} \\ \mbox{ All Rights Reserved} \end{array}$

# Dedication

I dedicate this dissertation to my beloved family.

# Acknowledgments

I would like to thank Dr. Avesta Sasan who made this work possible by positive support and great understanding.

# Table of Contents

|     |        |         |                                                                                                 | Page |

|-----|--------|---------|-------------------------------------------------------------------------------------------------|------|

| Lis | t of T | ables   |                                                                                                 | vii  |

| Lis | t of F | igures  |                                                                                                 | viii |

| Ab  | stract |         |                                                                                                 | 0    |

| 1   | Intr   | oductio | m                                                                                               | 1    |

| 2   | TCI    | D-NPE:  | : A Re-configurable and Efficient Neural Processing Engine, Powered                             |      |

|     | by N   | ovel Te | emporal-Carry-Deferring MACs                                                                    | 3    |

|     | 2.1    | Introd  | uction                                                                                          | 3    |

|     | 2.2    | Relate  | ed Work                                                                                         | 4    |

|     | 2.3    | Our P   | roposed MLP Processing Engine                                                                   | 5    |

|     |        | 2.3.1   | Temporal Carry Deferring MAC (TCD-MAC)                                                          | 5    |

|     |        | 2.3.2   | TCD-NPE: Our Proposed MLP Neural Processing Engine                                              | 9    |

|     | 2.4    | Result  | .s                                                                                              | 19   |

|     |        | 2.4.1   | Evaluation and Comparison Framework                                                             | 19   |

|     |        | 2.4.2   | TCD-MAC PPA Assessment                                                                          | 20   |

|     |        | 2.4.3   | TCD-NPE Evaluation                                                                              | 21   |

|     | 2.5    | Conclu  | usion $\ldots$ | 25   |

| 3   | NES    | STA: H  | amming Weight Compression-Based Neural Processing Engine $\ldots$ .                             | 26   |

|     | 3.1    | Introd  | uction and Background                                                                           | 26   |

|     | 3.2    | NEST    | A: Proposed Processing Engine                                                                   | 29   |

|     |        | 3.2.1   | Motivation 1: Temporal Carry                                                                    | 29   |

|     |        | 3.2.2   | Motivation 2: Compression and Expansion                                                         | 30   |

|     |        | 3.2.3   | NESTA: Our Proposed Solution                                                                    | 32   |

|     |        | 3.2.4   | NESTA: Putting it all together                                                                  | 37   |

|     |        | 3.2.5   | Supported Data Flows                                                                            | 39   |

|     | 3.3    | Result  | <br>js                                                                                          | 42   |

|     |        | 3.3.1   | Evaluation and Comparison Framework                                                             |      |

|     |        | 3.3.2   | PPA efficiency: NESTA v.s. MAC9s                                                                |      |

|     |        | 3.3.3   | PPA efficiency: NESTA v.s. MACs                                                                 | 46   |

|     |        |         |                                                                                                 | -0   |

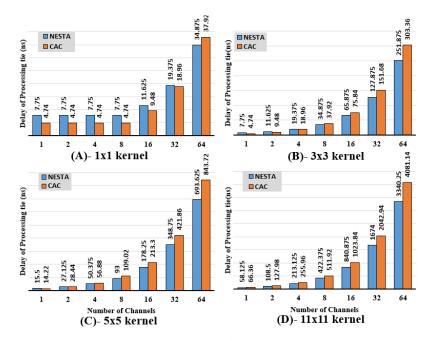

|     |         | 3.3.4  | NESTA for Efficient CNN Processing                                                                                                            | 48 |

|-----|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 3.4     | Conclu | usion                                                                                                                                         | 48 |

| 4   | TC      | D-MAC  | ++: An Enhanced Version of Temporal Carry Deferring MAC $\ldots$                                                                              | 49 |

|     | 4.1     | Introd | $uction \ldots \ldots$ | 49 |

|     |         | 4.1.1  | Temporal Carry Deferring MAC++ (TCD-MAC++)                                                                                                    | 51 |

|     |         | 4.1.2  | Shorter Critical Path                                                                                                                         | 52 |

|     |         | 4.1.3  | Early Free-Run Stopping (EFRS)                                                                                                                | 54 |

|     | 4.2     | Result | S                                                                                                                                             | 55 |

|     |         | 4.2.1  | TCD-MAC++ PPA Assessment                                                                                                                      | 56 |

|     |         | 4.2.2  | EFRS Evaluation                                                                                                                               | 59 |

|     | 4.3     | Conclu | usion                                                                                                                                         | 60 |

| 5   | Fut     | ure Wo | rks                                                                                                                                           | 61 |

|     | 5.1     | Introd | $uction \ldots \ldots$ | 61 |

|     | 5.2     | Future | e Work                                                                                                                                        | 61 |

| Bil | oliogra | aphy . |                                                                                                                                               | 64 |

# List of Tables

| Table |                                                                             | Page |

|-------|-----------------------------------------------------------------------------|------|

| 2.1   | PPA comparison between various MACs and TCD-MAC.                            | 20   |

| 2.2   | Percentage improvement in throughput and energy when using a TCD-MAC        |      |

|       | (as opposed to a conventional MAC) to process an stream of $1, 10, 100$ and |      |

|       | 1000 multiplication and addition operations                                 | 21   |

| 2.3   | TCD-NPE implementation details and PPA results. In this table, we have      |      |

|       | only reported the leakage power. The dynamic power is activity dependent.   |      |

|       | The breakdown of energy consumption for processing different benchmarks     |      |

|       | is reported in Fig. 2.10                                                    | 22   |

| 2.4   | MLP benchmarks used in this work [1].                                       | 24   |

| 3.1   | Depth and complexity of some of the existing and modern CNN solutions for   |      |

|       | object detection.                                                           | 27   |

| 3.2   | Comparing the efficiency of HWC-Adder(s) vs Adder tree constructed using    |      |

|       | Brent-Kung (BK) and Kogge-Stone (KS).                                       | 32   |

| 3.3   | PPA comparison between various MAC flavors and NESTA-V1 and NESTA           | . 47 |

| 3.4   | Percentage improvement in Throughput(left) & energy consumption(right)      |      |

|       | when using NESTA to process 1K of different convolution size                | 47   |

# List of Figures

| Figure |                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------|------|

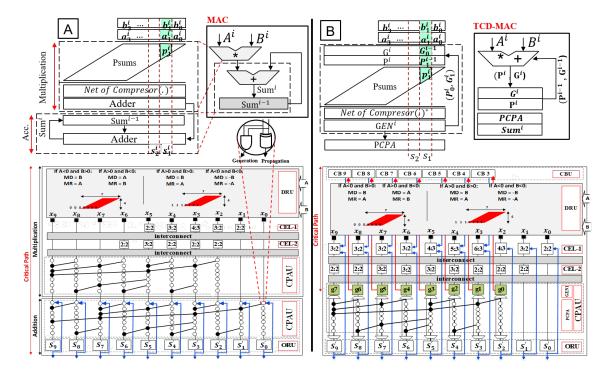

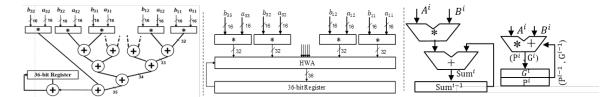

| 2.1    | Comparing the architecture of A) a typical MAC, versus B) a simplified 2-                  |      |

|        | input version of TCD-MAC. In all variables in form of $D_m^i$ , the subscript              |      |

|        | (m) captures the bit position values, and postscript $(i)$ capture the cycle               |      |

|        | (iteration). For example, $A^i, B^i$ are the input data in the $i^{th}$ iteration (corre-  |      |

|        | sponding to the $i^{th}$ cycle) of the multiply accumulate operation. The $b_m^i, a_m^i$ , |      |

|        | and $p_m^i$ are accordingly the $m^{th}$ significant bits of inputs A, B, and partial      |      |

|        | sum at the $i^{th}$ cycle (iteration). The division of CPA into GEN and PCPA is            |      |

|        | also shown in this figure. Note that the $PCPA$ is only executed at the last               |      |

|        | cycle                                                                                      | 6    |

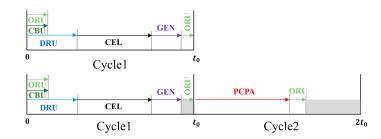

| 2.2    | TCD-MAC cycle time is computed by excluding the PCPA. In the last cy-                      |      |

|        | cle of computation, the TCD-MAC activates the PCPA to propagate the                        |      |

|        | unconsumed carry bits.                                                                     | 8    |

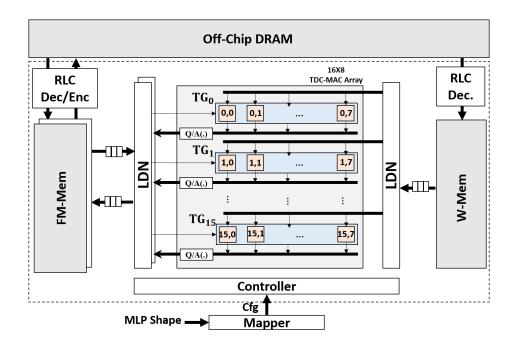

| 2.3    | TCD-NPE overall architecture. The Mapper algorithm is executed exter-                      |      |

|        | nally, and the sequence of events is loaded into the controller for governing              |      |

|        | the OS data and control flow                                                               | 10   |

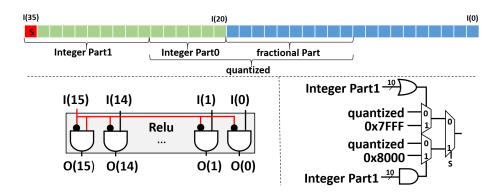

| 2.4    | The logic implementation of Quantization (Left) and Relu Activation (right)                |      |

|        | for signed fixed-point 16bit values                                                        | 11   |

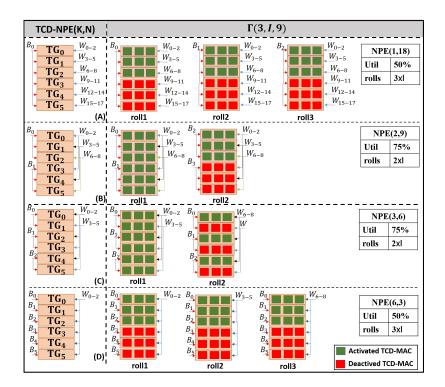

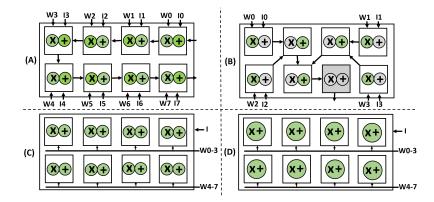

| 2.5    | Assuming a $6\times 3$ PE-array of TCD-MACs, the NPE(K, N) could be config-                |      |

|        | ured such that (K, N) $\in \{(1,18), (2,9), (3,6), (6,3)\}$ . This figure illustrate       |      |

|        | the number of rolls, and utilization when each of NPE(K,N) configurations                  |      |

|        | is used to run a $\Gamma(3,I,9)$ . model. Each roll is executed I times                    | 13   |

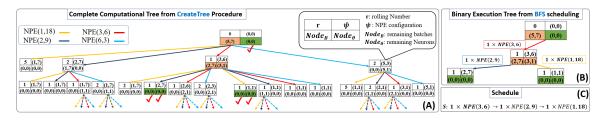

| 2.6    | An example execution of algorithm 1 when processing $\Gamma(5,I,7)$ model using            |      |

|        | a TCD-MAC with a $6\times 3$ PE-array. (A): the complete computational Tree                |      |

|        | from CreateTree procedure, (B): binary execution tree obtained from BFS                    |      |

|        | scheduling, (C): the sequence of scheduled events to compute the model based               |      |

|        | on binary execution tree                                                                   | 14   |

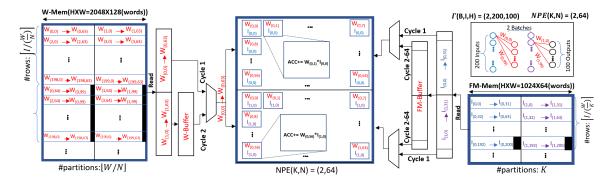

| 2.7  | The arrangement of data in W-mem and FM-mem when our proposed TCD-                         |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | NPE is used in NPE(K,N)=(2,64) configuration mode to process $B = 2$                       |    |

|      | batches of a hidden layer of an MLP model as defined by $\Gamma(B, I, H) =$                |    |

|      | (2, 200, 100)                                                                              | 16 |

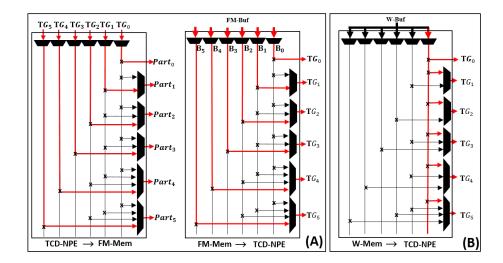

| 2.8  | An example of LDN for managing the connection between a (6 $\times$ 3)-PE-                 |    |

|      | array's NoC and memory. (A).left: LDN for writing from NoC data bus to                     |    |

|      | FM-mem. (A).right: LDN for reading from FM-mem to NoC bus. (B): LDN                        |    |

|      | for reading from W-mem into NoC filter bus. The FM-mem in this case, is                    |    |

|      | divided into 6 partitions, supporting the simultaneous process of 6 batches                |    |

| 2.9  | at a time                                                                                  | 19 |

|      | using conventional MACs to form a systolic array. (B): RNA data flow re-                   |    |

|      | sulted from unrolling the MLP model and mapping the computation tree to                    |    |

|      | conventional MACs (each used as either multiplier or adder) as described in                |    |

|      | [2]. (C) The OS data flow using conventional MAC. (D): The OS dataflow                     |    |

|      | using TCD-MAC                                                                              | 23 |

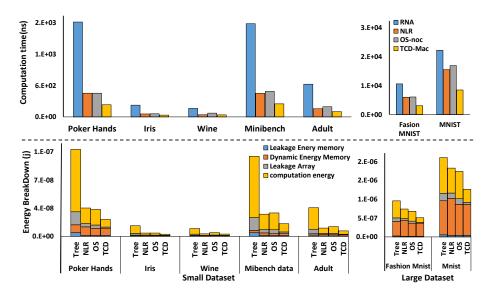

| 2.10 | Comparison of TCD-NPE with an NPE constructed using conventional MACs                      |    |

|      | that uses the OS, NLR, or RNA data flow. top): Execution time for various                  |    |

|      | MLP benchmarks. Bottom): Energy consumption for various MLP bench-                         |    |

| 3.1  | marks                                                                                      | 25 |

|      | the output <i>Ofmaps</i>                                                                   | 28 |

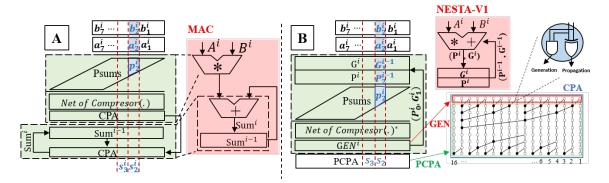

| 3.2  | comparing the architecture of A) a typical MAC, versus B) a simplified 2-                  |    |

|      | input version of NESTA. In all variables in the form of $D_m^i$ , the subscript            |    |

|      | (m) captures the bit position values, and postscript $(i)$ capture the cycle               |    |

|      | (iteration). For example, $A^i, B^i$ are the input data in the $i^{th}$ iteration (corre-  |    |

|      | sponding to the $i^{th}$ cycle) of the multiply accumulate operation. The $b_m^i, a_m^i$ , |    |

|      | and $p_m^i$ are accordingly the $m^{th}$ significant bits of inputs A, B, and partial      |    |

|      | sum at the $i^{th}$ cycle (iteration). The division of CPA into GEN and PCPA is            |    |

|      | also shown in this figure. Note that the $PCPA$ is only executed at the last               |    |

|      | cycle                                                                                      | 29 |

|      |                                                                                            |    |

| 3.3 | An Adder tree for 9 16-bit-width entries (left), Hamming Weight Adder (HW- $$ |

|-----|-------------------------------------------------------------------------------|

|     | Adder) of 9 16-bit-wide entries (right). In the HWC-Adder compressor hier-    |

|     | archy (CEL) the complete compressors are colored blue, while compressors      |

|     | with available capacity are white. For building the improved version of HWC-  |

|     | Adder (HWC-Adder*), 2 bits from each compressor in CEL-1 are differed to a    |

|     | compressor in the same bit position in CEL-2, increasing the number of com-   |

|     | plete compressors and reducing the critical path delay in CEL-1 as reported   |

|     | in table 3.2                                                                  |

- In NESTA carry bits that are generated in GEN section of the CPA do not 3.4propagate into the carry chain. Instead, they are captured by CB registers. In the next cycle, the carry bits (of the previous cycle that are stored in CB registers) are fed to the hamming weight compressors at that bit position, temporally deferring their impact to the next cycle. The compression unit, in each cycle consumes the bit values from 9 new input (W, I) pairs, the Carry bits of the previous cycle (stored in CB registers) and the partial sum stored in S registers. The consumption of bit values in S registers implement the accumulation function. In the last round of computation, instead of capturing the carry bits in CB registers, they are fed to the PCPA (Partial CPA) to propagate through the carry chain and generate the correct convolution 34results. NESTA cycle time is computed by excluding the execution time of PCPA. In 3.5the last cycle of computation of convolution, the NESTA activates the PCPA 38NESTA Row Stationary (RS) data flow for executing  $3 \times 3$  convolution across 3.6

- multiple channels (right) and 5×5 convolution across multiple channels (left).

A similar concept can be used to support all other convolutions sizes. . . . 39

3.7 A 9-input MAC, which is identified as (Multiplier Choice, Adder Choice).

31

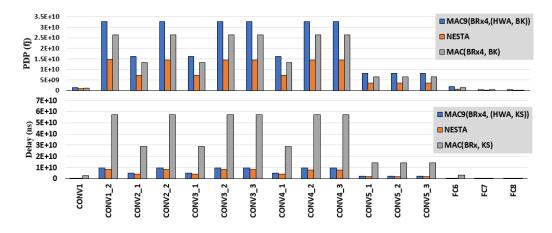

| 3.9  | Breakdown of delay and energy consumption of each layer of VGG $[3]$ when                                                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | processed by a single MAC, a single MAC9 or a single NESTA core. A linear                                                                  |    |

|      | increase in the number of cores linearly reduces the processing time                                                                       | 45 |

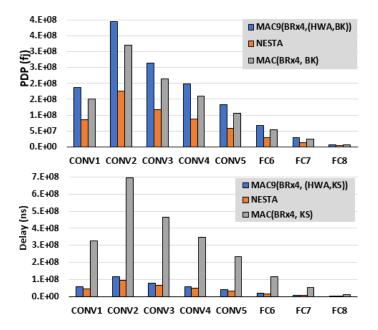

| 3.10 | Breakdown of delay and energy consumption of each layer of AlexNet [4]                                                                     |    |

|      | when processed by a Neural engine composed of MACs, MAC9s or NESTA                                                                         |    |

|      | cores                                                                                                                                      | 45 |

| 3.11 | Area, Delay, Power, and PDP comparison between NESTA and MAC9s con-                                                                        |    |

|      | structed using fast adders and multipliers. The star identifies the best $MAC9$                                                            |    |

|      | in each category.                                                                                                                          | 46 |

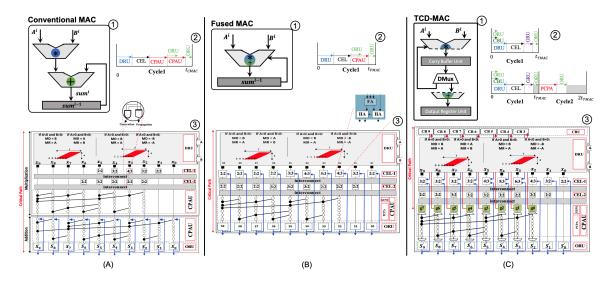

| 4.1  | Comparing of three available architecture for processing a stream of MAC                                                                   |    |

|      | operations with operands $A^i, B^i$ in the $i^{th}$ iteration (corresponding to the                                                        |    |

|      | $i^{th}$ cycle) of the multiply-accumulate operation. A-1) an abstract view of a                                                           |    |

|      | typical MAC, B-1) an abstract view of a Fused MAC, C-1) an abstract view                                                                   |    |

|      | of a TCD-MAC. A-2, B-2, C-2 are the activated components at each cycle of                                                                  |    |

|      | the mac architecture, and A-3, B-3, C-3 are the dataflows of each one of the                                                               |    |

|      | MAC architecture for processing operands $A^i, B^i, \ldots, \ldots, \ldots$                                                                | 50 |

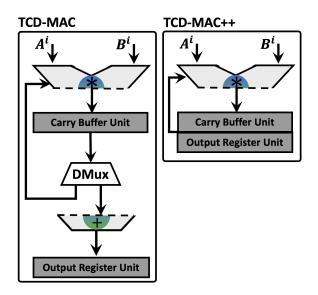

| 4.2  | An abstract view of the architectures TCD-MAC and TCD-MAC++ for                                                                            |    |

|      | performing MAC operation on a stream of operands $A^i$ and $B^i$                                                                           | 52 |

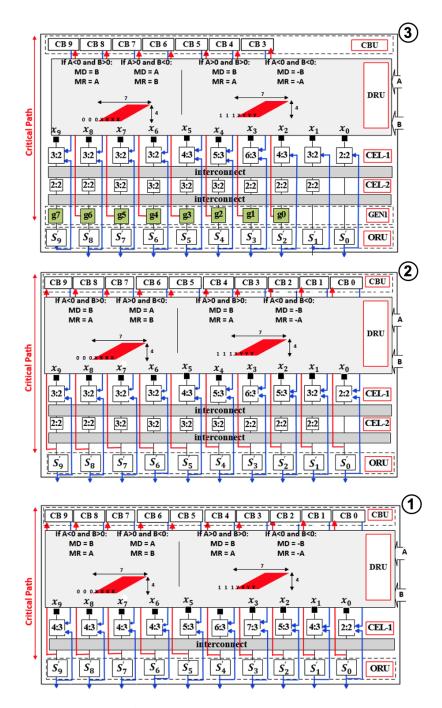

| 4.3  | Three versions of TCD-MAC++ for calculating mac operations with 4-bit                                                                      |    |

|      | width signed operands. 1) TCD-MAC++ $\alpha$ : deferring carry bits from the                                                               |    |

|      | first layer of expansion layer. 2) TCD-MAC++ $_{\beta}$ : deferring the carry bits                                                         |    |

|      | from the second layer of expansion layer 3) TCD-MAC++ $\gamma$ : deferring the                                                             |    |

|      | carry bits from the third layer of expansion layer (available mac operation                                                                |    |

|      | with a higher bit-width operands)                                                                                                          | 53 |

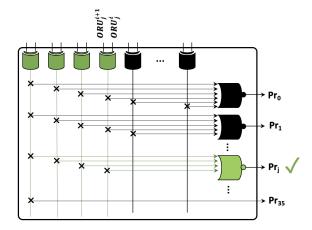

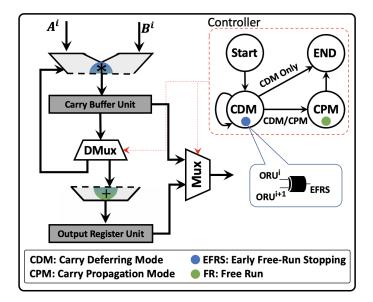

| 4.4  | The architecture of EFRS for terminating the operation based on the desired                                                                | 00 |

| 1.1  | precision $Pr_0$ to $Pr_{35}$ that are obtained from the difference between $ORU^i$                                                        |    |

|      |                                                                                                                                            | EE |

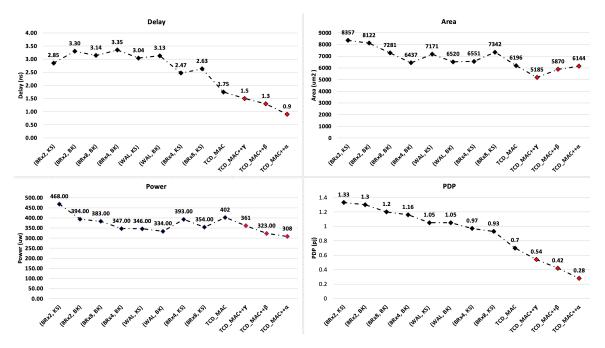

| 4.5  | and $ORU^{i+1}$ of two successive iterations i and i+1 of TCD-MAC++<br>PPA comparison between various MACs and TCD-MAC, and different ver- | 55 |

| 1.0  | sions of TCD-MAC++.                                                                                                                        | 56 |

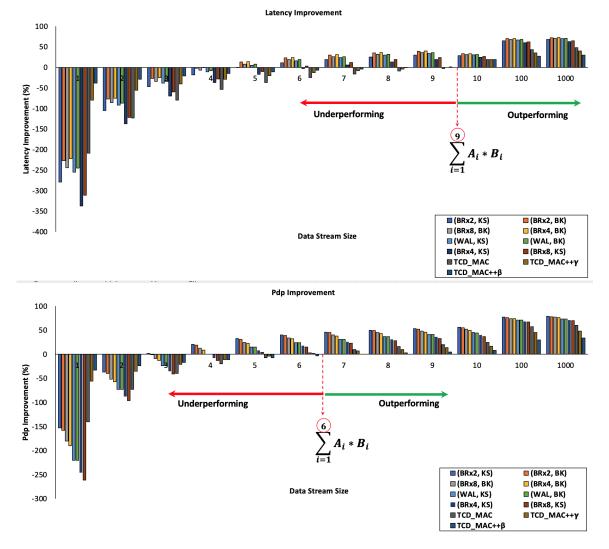

| 4.6  | Percentage improvement in throughput and energy when using a TCD-MAC++                                                                     | 50 |

| 2.0  | (as opposed to a conventional MAC) to process an input stream size ranging                                                                 |    |

|      | from 1 to 1000.                                                                                                                            | 58 |

|      | пош т ю тооо                                                                                                                               | 00 |

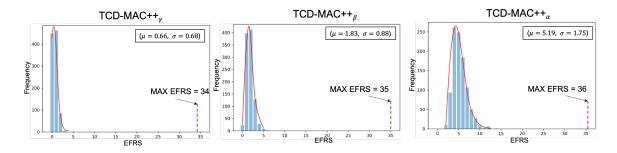

| 4.7 | The number of needed EFRS of a stream of 1k mac operations of a batch      |    |

|-----|----------------------------------------------------------------------------|----|

|     | of 1k operands which is performed by three versions of TCD-MAC++. Red      |    |

|     | dash-line shows the maximum number of needed free run in order to generate |    |

|     | the accurate results.                                                      | 59 |

| 5.1 | An abstract view of the architecture TCD-MAC/TCD-MAC++ for perform-        |    |

## Abstract

# NEUROMORPHIC HARDWARE DESIGN FOR EXECUTING DEEP NEURAL NET-WORKS ON LOW POWER AND LIMITED RESOURCE INFRASTRUCTURES

Ali Mirzaeian, PhD

George Mason University, 2021

Dissertation Director: Dr. Avesta Sasan

The applications of machine learning algorithms are innumerable and cover nearly every domain of modern technology. During this rapid growth of this area, more and more companies have expressed a desire to utilize machine learning techniques in smaller devices, such as cell phones or smart Internet of Things (IoT) instruments. However, as machine learning has so far required a power source with more capacity and higher efficiency than a conventional battery. Therefore, introducing neural network accelerators with low energy demands and low latency for executing machine learning techniques has drawn lots of attention in both the academia and industry.

In this work, we first propose the design of Temporal-Carry-deferring MAC (TCD-MAC) and illustrate how our proposed solution can gain significant energy and performance benefit when utilized to process a stream of input data. We then propose using the TCD-MAC to build a reconfigurable, high speed, and low power Neural Processing Engine (TCD-NPE). Furthermore, we expand the idea of TCD-MAC to present NESTA, which is a specialized Neural engine that reformats Convolutions into  $3 \times 3$  batches and uses a hierarchy of Hamming Weight Compressors to process each batch.

## Chapter 1: Introduction

In recent years, machine learning has provided a foundation for rapid technological advancement and massive economic growth. The global value of the machine learning market is estimated at over \$7 billion, and this figure is predicted to become much larger in the coming decade. Machine learning is one of the most exciting frontiers in computer engineering. By training computer algorithms to conduct tasks that normally require human involvement, engineers have saved countless industries both time and money.

Around the globe, machine learning is widely employed in industries like medicine and finance. To take medicine as an example, machine learning is being employed to personalize health care to suit specific patients and to diagnose illnesses. Machine learning has become more ubiquitous as engineers refine the available technology. However, the progress of machine learning and the expansion of its use in the medical industry, as well as many other industries, depends in large part on the progress of efficient computing technologies.

Machine learning is becoming a more and more computationally expensive operation. At the same time, more and more companies have expressed a desire to utilize machine learning techniques in smaller devices, such as cell phones or smart Internet of Things (IoT) instruments. The size restrictions of remote and wireless devices have presented a barrier to this initiative, however, as machine learning has so far required a power source with more capacity and higher efficiency than a conventional battery.

On the hardware platform side, the GPU solutions have rapidly evolved over the past decade and are considered a prominent mean of training and executing DNN models. Although GPU has been a real energizer for this research domain, its is not an ideal solution for efficient learning, and it is shown that development and deployment of hardware solutions dedicated to processing the learning models can significantly outperform GPU solutions. This has lead to the development of Tensor Processing Units (TPU) [5], Field Programmable Gate Array (FPGA) accelerator solutions [6], and many variants of dedicated ASIC solutions [7–10].

Today, there exist many different flavors of ASIC neural processing engines. The common theme between these architectures is the usage of a large number of simple Processing Elements (PEs) to exploit the inherent parallelism in DNN models. Compare to a regular CPU with a capable Arithmetical Logic Unit (ALU), the PE of these dedicated ASIC solutions is stripped down to a simple Multiplication and Accumulation (MAC) unit. However, many PEs are used to either form a specialized data flow [8], or tiled into a configurable NoC for parallel processing DNNs [10,12,13]. The observable trend in the evolution of these solutions starting from DianNao [7], to DaDianNao [8], to ShiDianNao [9], to Eyris [10] (to name a few) is the optimization of data flow to increase the re-use of information read from memory, and to reduce the data movement (in NOC and to/from memory).

Common between previously named ASIC solutions, is designing for data reuse at NOC level but ignoring the possible optimization of the PE's MAC unit. A conventional MAC operates on two input values at a time, computes the multiplication result, adds it to its previously accumulated sum, and output a new and *correct* accumulated sum. When working with streams of input data, this process takes place for every input pair taken from the stream. But in many applications, we are not interested in the correct value of intermediate partial sums, and we are only interested in the correct final result.

The first design question that we answer is if we can design a faster and more efficient MAC if we remove the requirement of generating a correct intermediate sum when working on a stream of input data. This question led us to the design of a novel building block to improve the speed of machine learning techniques. We called this basic block Temporal Carry Deferring MAC (TCD-MAC). Later on, we introduced TCD-MAC++ as an extended version of TCD-MAC. We employed these basic blocks for building a Multi-Layer Perceptron (MLP) processing engine and also a Convolutional Neural Network (CNN) engine.

# Chapter 2: TCD-NPE: A Re-configurable and Efficient Neural Processing Engine, Powered by Novel Temporal-Carry-Deferring MACs

## 2.1 Introduction

Deep neural networks (DNNs) has attracted a lot of attention over the past few years, and researchers have made tremendous progress in developing deeper and more accurate models for a wide range of learning-related applications [3, 4, 14–21]. The desire to bring these complex models to resource-constrained hardware platforms such as Embedded, Mobile and IoT devices has motivated many researchers to investigate various means of improving the DNN models' complexity and computing platform's efficiency [22, 23]. In terms of model efficiency, researchers have explored different techniques including quantization of weights and features [24, 25], formulating compressed and compact model architectures [25–31], increasing model sparsity and pruning [25, 32], binarization [24, 33], and other model-centered alternatives.

In this chapter, we propose the design of Temporally-deferring-Carry MAC (TCD-MAC), and use the TCD-MAC to build a reconfigurable, high speed, and low power MLP Neural Processing Engine (NPE). We illustrated that TCD-MAC can produce an approximate-yet-correctable result for intermediate operations, and could correct the output in the last state of stream operation to generate the correct output. We then build a Re-configurable and specialized MLP Processing Engine using a farm of TCD-MACs (used as PEs) supported by a reconfigurable global buffer (memory) and illustrate its superior performance and lower energy consumption when compared with the state of the art ASIC

NPU solutions. To remove the data flow dependency from the picture, we used our proposed NPE to process various Fully Connected Multi-Layer Perceptrons (MLP) to simplify and reduce the number of data flow possibilities and to focus our attention on the impact of PE in the efficiency of the resulting accelerator.

## 2.2 Related Work

The work in [10], categorizes the possible data flows into four major categories: 1) No Local Reuse (NLR) where neither the PE (MAC) output nor filter weight is stored in the PE. Examples of accelerator solutions using NLR data flow include [7, 8, 35]. 2) Output Stationary (OS) where the filter and weight values are input in each cycle, but the MAC output is locally stored. Examples of accelerator solutions using OS data flow include [9, 36–38]. 3) Weight Stationery (WS) where the filter values are locally stored, but the MAC result is passed on. Examples of accelerators using WS data flow include [39–41], and 4) Row Stationary (RS and its variant RS+) where some of the reusable MAC outputs and filter weights remain within a local group of PE to reduce data movement for computing the next round of computation. An example of accelerator using RS is [10].

The OS and NLR are generic data flow and could be applied to any DNN, while the WS and RS only apply to Convolutional Neural Networks (CNN) to promote the reuse of filter weights. Hence, the type of applicable data reuse (output and/or weight) depends on the model being processed. The Multi-Layer Perceptrons (MLP) is a sub-class of NNs that has extensively used for modeling complex and hard to develop functions [42]. An MLP has a feed-forward structure, and is comprised of three types of layers: (1) An input layer for feeding the information to the model, 2) one or more hidden layer(s) for extracting features, and (3) an output layer that produces the desired output which could be regression, classification, function estimation, etc. Unfortunately, when it comes to MLPs, or when processing Fully Connected (FC) layers, unlike CNNS, no filter weight could be reused. In these models the viable data flows are the OS and NLR. The only possible solution

for using the WS solution in processing MLPs is the case of multi-batch processing that may benefit from weight reuse. Another related work is the NPE proposed in [2]. This solution, denoted as RNA, is a special case of NLR, where data flow is controlled through NoC connectivity between different PEs; RNA breaks the MLP model into multi-layer loops that are successively mapped to the accelerator PEs, and uses the PEs as either a multiplier or an adder, dynamically forming a systolic array.

In the result section of this paper, We demonstrate that the OS solutions are in general more efficient than NLR solutions. We further illustrate that our proposed TCD-MAC, when used in the context of our proposed NPE, outperform state of the art accelerators that rely on (fastest and most efficient) conventional MAC solutions.

## 2.3 Our Proposed MLP Processing Engine

Before describing our proposed NPE solution, we first describe the concept of *temporal* carry and illustrate how this concept can be utilized to build a Temporal Carry deferring Multiplication and Accumulation (TCD-MAC) unit. Then, we describe, how an array of TCD-MAC are used to design a re-configurable and high-speed MLP processing engine, and how the sequence of operations in such NPE is scheduled to compute multiple batches of MLP models.

### 2.3.1 Temporal Carry Deferring MAC (TCD-MAC)

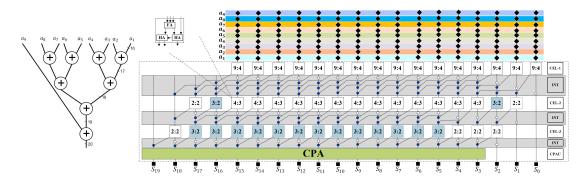

Suppose two vectors A and B each have N M-bit values, and the goal is to compute their dot product,  $\sum_{i=0}^{N-1} (A_i * B_i)$  (similar to what is done during the activation process of each neuron in a NN). This could be achieved using a single Multiply-Accumulate (MAC) unit, by working on 2 inputs at a time for N rounds. Fig. 2.1(A-top) shows the general view of a typical MAC architecture that is comprised of a multiplier and an adder (with 4-bit input width), while Fig. 2.1(A-bottom) provides a more detailed view of this architecture. The partial products (M partial product for M-bits) are first generated in Data Reshape Unit

(DRU). Then the hamming weight compressors (HWC) in the Compression and Expansion Layer (CEL) transform the addition of M partial products into a single addition of two larger binaries, the addition of which in an adder generates the multiplication result.

Figure 2.1: Comparing the architecture of A) a typical MAC, versus B) a simplified 2-input version of TCD-MAC. In all variables in form of  $D_m^i$ , the subscript (m) captures the bit position values, and postscript (i) capture the cycle (iteration). For example,  $A^i, B^i$  are the input data in the  $i^{th}$  iteration (corresponding to the  $i^{th}$  cycle) of the multiply accumulate operation. The  $b_m^i, a_m^i$ , and  $p_m^i$  are accordingly the  $m^{th}$  significant bits of inputs A, B, and partial sum at the  $i^{th}$  cycle (iteration). The division of CPA into GEN and PCPA is only executed at the last cycle.

The building block of the CEL unit are the HWC. A HWC, denoted by  $C_{HW}(m:n)$ , is a combinational logic that implements the Hamming Weight (HW) function for m inputbits (of the same bit-significance value) and generates an n-bit binary output. The output n of HWC is related to its input m by:  $n = \lceil log_2^m \rceil$ . For example "011010", "111000", and "000111" could be the input to a  $C_{HW}(6:3)$ , and all three inputs generate the same Hamming weight value represented by "011". A Completed HWC function  $CC_{HW}(m:n)$  is defined as a  $C_{HW}$  function, in which m is  $2^n - 1$  (e.g., CC(3:2) or CC(7:3)). Each HWC takes a column of m input bits (of the same significance value) and generates its n-bit hamming weight. In the CEL unit, the output n-bits of each HWC is fed (according to its bit significance values) as an input to the proper  $C_{HW}(s)$  in the next-layer CEL. This process is repeated until each column contains no more than 2-bits, which is a proper input size for a simple adder. In Fig. 2.1 it is assumed that a Carry Propagation Adder Unit (CPAU) is used. The result is then added to the previously accumulated value in the output register in the second adder to generate a new accumulated sum. Note that in conventional MAC, the carry (propagation) bits in the CPAUs are spatially propagated through the carry chain which constitutes the critical timing path for both adder and multiplier.

Fig.2.1.B shows our proposed TCD-MAC. In this solution, only a single CPAU is used. Furthermore, the CPAU is broken into two distinct segments 1) The GENeration (GEN) and Partial CPA (PCPA). The Gen is the first layer of CPA logic that produces the Generate  $(G_i^c)$  and Propagate  $(P_i^c)$  signals for each bit position i at cycle c. The TCD-MAC relies on the assumption that we only need to correctly compute the final result of multiplication and accumulation over an array of inputs (e.g.  $\sum_{i=0}^{N-1} (A_i * B_i)$ ), while relaxing the requirement for generating correct intermediate sums. This relaxed specification is applicable when a MAC is used to compute a Neuron value in a DNN. Benefiting from this relaxed requirement, the TCD-MAC skips the computation of PCPA, and injects (defers) the  $G_i^c$  and  $P_i^c$  generated in cycle c, to the CEL unit in cycle c+1. Using this approach, the propagation of carry-bit in the long carry chain (in PCPA) is skipped, and without loss of accuracy, the impact of the carry bit is injected to the correct bit position in the next cycle of computation. We refer to this process as temporal (in time) carry propagation. The Temporally carried  $G_i^c$  is stored in a new set of registers denoted as Carry Buffer Unit (CBU), while the  $P_i^c$  in each cycle is stored in the output register Unit (ORU). Note that CBU bits can be injected to any of the  $C_{HW}(m:n)$  in any of the CEL layers in the same bit position. However, it is desired to inject the CB bits to a  $C_{HW}(m:n)$  that is incomplete to avoid an increase in the size and critical path delay of the CEL.

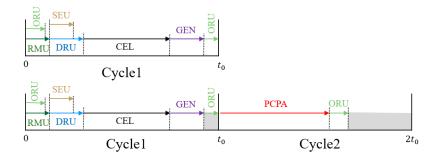

Figure 2.2: TCD-MAC cycle time is computed by excluding the PCPA. In the last cycle of computation, the TCD-MAC activates the PCPA to propagate the unconsumed carry bits.

Assuming that a TCD-MAC works on an array of N input pairs, the temporal carry injection is done N-1 times. In the last round, however, the PCPA should be executed. As illustrated in Fig. 2.2, in this approach, the cycle time of the TCD-MAC could be reduced to that excluding the PCPA, allowing the computation over PCPA to take place in an extra cycle. The one extra cycle allows the unconsumed carry bits to be propagated in PCPA carry chain, forcing the TCD-MAC to generate the correct output. Using this technique we shortened the cycle time of TCD-MAC for a large number of cycles. The saving obtained from shorter cycles over a large number of cycles significantly outweighs the penalty of one extra cycle.

To support signed inputs, in TCD-MAC we pre-process the input data. For a partial product  $p = a \times b$ , if one value (a or b) is negative, it is used as the multiplier. With this arrangement, we treat the generated partial sums as positive values and later correct this assumption by adding the two's complement of the multiplicand during the last step of generating the partial sum. Following example clarify this concept: let's suppose that a is a positive and b is a negative b-bit binary. The multiplication  $b \times a$  can be reformulated as:

$$b \times a = (-2^7 + \sum_{i=0}^{6} x_i 2^i) \times a = -2^7 a + (\sum_{i=0}^{6} x_i 2^i) \times a$$

(2.1)

The term  $-2^7 a$  is the two's complement of multiplicand which is lef-shifted by 7 bits, and the term  $(\sum_{i=0}^{6} x_i 2^i) \times a$  is only accumulating shifted version of the multiplicand.

### 2.3.2 TCD-NPE: Our Proposed MLP Neural Processing Engine

TCD-NPE is a configurable neural processing engine which is composed of a 2-D array of TCD-MACs. The TCD-MAC array is connected to a global buffer using a configurable Network on Chip (NOC) that supports various forms of data flow as described in section 4.1. However, for simplicity, we limit our discussion to supporting OS and NLR data flows for executing MLPs. This choice is made to help us focus on the performance and energy impact of utilizing TCD-MACs in designing an efficient NPE without complicating the discussion with the support of many different data flows.

Figure 2.3 captures the overall TCD-NPE architecture. It is composed of 1) Processing Element (PE) array which is a tiled array of TCD-MACs, 2) Local Distribution Networks (LDN) that manages the PE-array connectivity to memories, 3) Two global buffers, one for storing the filter weights and one for storing the feature maps, and 4) The Mapper-andcontroller unit which translates the MLP model into a supported data and control flow. The functionality and design of each of these units are described next:

Figure 2.3: TCD-NPE overall architecture. The Mapper algorithm is executed externally, and the sequence of events is loaded into the controller for governing the OS data and control flow.

### **PE** Array

The PE-array is the computational engine of our proposed TCD-NPE. Each PE in this tiled array is a TCD-MAC. Each TCD-MAC could be operated in two modes: 1) Carry Deferring Mode (CDM), or 2) Carry Propagation Mode (CPM). According to the discussion in section 2.3.1, when working with an input stream of size N, the TCD-MAC is operated in the CDM model for N cycles (computing approximate sum), and in the CPM mode in the last cycle to generate the correct output. This is in line with OS data flow as described in section 2.2. Note that the TCD-MAC in this PE-array could be operated in CPM mode in every cycle allowing the same PE-array architecture to also support the NLR. After computing the raw neuron value (prior to activation), the TCD-MAC writes the computed sum into the NOC bus. The Neuron value is then passed to the quantization and activation unit before being written back to the global buffer. Fig. 3.5 captures the logic implementation for quantization (to 16 bits) and Relu[4] activation in this unit.

Figure 2.4: The logic implementation of Quantization (Left) and Relu Activation (right) for signed fixedpoint 16bit values

Consider two layers of an MLP where the input layer contains M feature-values (neurons) and the second layer contains N Neurons. To compute the value of N Neurons, we need to utilize N TCD-MACs (each for M+1 cycles). If the number of available TCD-MACS is smaller than N, the computation of the neurons in the second layer should be unrolled to multiple rolls (rounds). If the number of available TCD-MACs is larger than neurons in the second layer (for small models), we can simultaneously process multiple batches (of the model) to increase the NPE utilization. Note that the size of the input layer (M) will not affect the number of needed TCD-MACs, but dictates how many cycles (M+1) are needed for the computation of each neuron.

When mapping a batch of MLP to the PE-array, we should decide how the computation is unrolled and how many batches (K), and how many output neurons (N) should be mapped to the PE-array in each roll. The optimal choice would result in the least number of rolls and the maximum utilization of the NPE. To illustrate the trade-offs in choosing the value of (K, N) let us consider a PE-array of size 18, which is arranged in 6 rows and 3 columns of TCD-MACs (similar to that in Fig. 2.3). We refer to each row of TCD-MACs as a TCD-MAC Group (TG). In our implementation, to reduce NOC complexity, the TG groups work on computing neurons in the same batch, while different TG groups could be assigned to work on the same or different batches. The architecture in Fig. 2.3 has 6 TG groups. Let us use NPE(K, N) to denote the choice of using the PE-array to compute N neuron values in K batches where  $N \times K = 18$ . In our example PE-array the following selections of K and N are supported:  $(K, N) \in (1, 18), (2, 9), (3, 6), (6, 3)$ . The (9, 2) and (18, 1) configuration are not supported as the value of N in this configurations is smaller than TG size = 3.

Fig. 2.5. left shows an abstract view of TCD-NPE and describe how the weights and input features (from one or more batches) are fed to the TCD-NPE for different choices of K and N. As an example 2.5. (left). A shows that input features from one batch are broadcasted between all TGs, while the weights are unicasted to each TCD-MAC. Let us represent the input scenario of processing B batches of U neurons in a hidden or output layer of an MLP model with I input features using  $\Gamma(B, I, U)$ . Fig. 2.5.(right) shows the NPE status when a  $\Gamma(3, I, 9)$  model (3 batches of a hidden layer with 9 neurons in a hidden layer each fed from I input neurons) is executed using each of 4 different NPE(K, N) choices. For example Fig. 2.5. (right).top shows that using configuration NPE(1,18), we process one batch with 18 neurons at a time. In this example, when using this configuration, the NPE is underutilized (50%) as there exist only 9 neurons in each batch. Following a similar argument, the NPE(6,3) arrangement also have 50% utilization. However the arrangement NPE(2,9), and NPE(3,6) reach 75% utilization (100% for the roll, and 50% for the second roll), hence either NPE(2,9) or NPE(3,6) arrangement is optimal for the  $\Gamma(3, I, 9)$  problem as they produce the least number of rolls. Note that the value of I in  $\Gamma(3, I, 9)$  denotes the number of input features which dictate the number of cycles that the NPE(K,N) should be executed.

Figure 2.5: Assuming a  $6 \times 3$  PE-array of TCD-MACs, the NPE(K, N) could be configured such that (K, N)  $\in \{(1,18), (2,9), (3,6), (6,3)\}$ . This figure illustrate the number of rolls, and utilization when each of NPE(K,N) configurations is used to run a  $\Gamma(3,I,9)$ . model. Each roll is executed I times.

### Mapping Unit

An MLP has one or more hidden layers and could be presented using  $Model(I - H_1 - H_2 - ... - H_N - O)$ , in which I is the number of input features,  $H_i$  is the number of Neurons in the hidden layer i, and O is the number of output layer neurons. The role of the mapping unit is to find the best unrolling scenario for mapping the sequence of problems  $\Gamma(B, I, H_1)$ ,  $\Gamma(B, H_1, H_2)$ , ...,  $\Gamma(B, H_{N-1}, H_N)$ , and  $\Gamma(B, H_N, O)$  into minimum number of NPE(K,N) computational rounds.

Algorithm 1 describes the mapper function for unrolling a multi-batch multi-layer MLP problem. In this Algorithm, B is the batch size that could fit in the NPE's feature-memory (if larger, we can unroll the B into N × B\* computation round, where B\* is the number of batches that fit in the memory). M[L] is the MLP layer size information, where M[i] is the number of nodes in layer i (with i = 0 being Input, and i = N + 1 being Output, and all others are hidden layers). The algorithm schedules a sequence of NPE(K, N) events to compute each MLP layer across all batches.

**Algorithm 1** Schedule NPE(K,N) rolls (events) to execute *B* batches of  $M(L) = MLP(I, H_1, ..., H_N, O)$ .

```

procedure PRACTICALCFGFINDER(Model M[L], BatchSize B)

for (l = 1; size(M); l + +) do

Tree_{head} = CreateTree(B, M[l])

Exec_{Tree} \leftarrow Shallowest binary tree (least rolls) from Tree_{head}

Schedule \leftarrow Schedule computational events by using BFS

on Exec_{Tree} to report NPE(K,N) and r at each node.

return Schedule

procedure CREATETREE(B, \Theta)

C[i] \leftarrow \text{find each } (K_i, N_i) | K_i, N_i \in \mathbb{N}, \& K_i < B

& size(NPE) = K_i \times N_i

for (i = 0; i < size(C); i + +) do

M_B = min(B, C[i][1]).

\triangleright C[i][1] = K_i

M_{\Theta} = min(\Theta, C[i][2]).

\triangleright C[i][2] = N_i

\psi = (M_B, M_\Theta)

\triangleright \psi: NPE's (K,N) configuration

r = \lfloor B/M_B \rfloor \times \lfloor \Theta/M_\Theta \rfloor

\triangleright r: \# \text{ of rolls with } \operatorname{NPE}(M_B, M_{\Theta})

if (B\%M_B) != 0 then

Node_B \leftarrow CreateTree(B\% M_B, \Theta)

if (K\% M_{\Theta}) ! = 0 then

Node_{\Theta} \leftarrow CreateTree(B - B\%M_B, K\%M_{\Theta})

Node \leftarrow createNode(r, \psi, Node_B, Node_\Theta)

{\rm return}\ {\bf Node}

```

Figure 2.6: An example execution of algorithm 1 when processing  $\Gamma(5, I, 7)$  model using a TCD-MAC with a  $6 \times 3$  PE-array. (A): the complete computational Tree from CreateTree procedure, (B): binary execution tree obtained from BFS scheduling, (C): the sequence of scheduled events to compute the model based on binary execution tree.

To schedule the sequence of events, the Alg. 1 first generates the expanded computational tree of the NPE using *CreateTree* procedure. This procedure first finds all possible ways that NPE could be segmented for processing N neurons of K batches, where  $K \leq B$ and stores them into configuration database C. Then for each of configurations of NPE(K, N), it derives how many rounds (r) of NPE(K, N) computations could be executed. Then it computes a) the number of remaining batches (with no computation) and b) the number of missing neurons in partially computed batches. It, then, creates a tree-node, with 4 major fields 1) the load-configuration  $\Psi(K_i^*, N_i^*)$  that is used to partially compute the model using the selected NPE $(K_i, N_i)$  such that  $(K_i^* \leq K_i) \& (N_i^* \leq N_i), 2)$  the number of rounds (rolls) r taken with computational configuration  $\Psi$  to reach that node, 3) a pointer to a new problem  $Node_B$  that specifies the number of remaining batches (with no computation), and 4) a pointer to a new problem  $Node_{\Theta}$  for partially computed batches. Then the CreateTreeprocedure is recursively called on each of the  $Node_B$  and  $Node_{\Theta}$  until the batches left, and partial computation left in a (leaf) node is zero. At this point, the procedure returns. After computing the computational tree, the mapper extracts the best execution tree by finding a binary tree with the least number of rolls (where all leaf nodes have zero computation left). The number of rolls is computed by summing up the r field of all computational nodes. Finally, the mapper uses a Breath First Search (BFS) on the Execution Tree  $(Exec_{Tree}$ and report the sequence of  $r \times NPE(K, N)$  for processing the entire binary execution tree. The reported sequence is the optimal execution schedule. Fig. 2.6 provides an example for executing 5 batches of a hidden MLP layer with 7 neurons. As illustrated the computationtree (Fig. 2.6.A) is first generated, and then the optimal binary execution tree (Fig. 2.6.B) resulting in the minimum number of rolls is extracted. Fig. 2.6.C captures the result of scheduling step where BFS search schedule the sequence of  $r \times NPE(K, N)$  events.

### Controller

The controller is an FSM that receives the "Schedule" from Mapper and generated the appropriate control signals to control the proper OS data flow for executing the scheduled sequence of events.

Figure 2.7: The arrangement of data in W-mem and FM-mem when our proposed TCD-NPE is used in NPE(K,N)=(2,64) configuration mode to process B = 2 batches of a hidden layer of an MLP model as defined by  $\Gamma(B, I, H) = (2, 200, 100)$ .

### Memory Architecture

The NPE global memory is divided into feature-map memory (FM-Mem), and Filter Weight memory (W-Mem). The FM-Mem consist of two memories with ping-pong style of access, where the input features are read from one memory, and output neurons for the next NN layer, are written to the other memory. When working with multiple batches (B), the input features from the largest number of fitting batches (B<sup>\*</sup>) is read into feature memory. For simplicity, we have assumed that the feature map is large enough to hold the features (neurons) in the largest layer of at least one MLP (usually the input) layer. Note that the NPE still can be used if this assumption is violated, however, now some of the computed neuron values have to be transferred back and forth between main memory (DRAM) and the FM-Mem for lack of space. The filter memory is a single memory that is filled with the filter weights for the layer of interest. The transfer of data from main memory (DRAM) to the W-Mem and FM-Mem is regulated using Run Length Coding (RLC) compression to reduce data transfer size and energy.

The data arrangement of features and weights inside the FM-Mem and W-Mem is shown in Fig. 2.7. The data storage philosophy is to sequentially store the data (weight and input features) needed by NPE (according to its configuration) in consecutive cycles in a single row. This data reshaping solution allows us to reduce the number of memory accesses by reading one row at a time into a buffer, and then consuming the data in the buffer in the next few cycles. We explain this data arrangement concept using the example shown in Fig. 2.7.

Fig. 2.7 shows the arrangement of data when we use our proposed TCD-NPE in NPE(K,N)=(2,64) configuration to process B=2 batches of a hidden layer of an MLP model as defined by  $\Gamma(B, I, H) = (2, 200, 100)$ . Note that the PE array size, in this case is  $16 \times 8$  which is divided into two  $8 \times 8$  arrays for processing each of 2 batches. The W-Mem, shown in left, is filled by storing the first N=64 weights of each outgoing edge from input Neurons (features) to each of the neurons in the hidden layer. Considering that the width of W-Mem is 256 bytes, and each weight is 2 bytes, the width of W-Mem  $(W_{W-mem})$  is 128 words. Hence, we can store 64 weights of the outgoing edge from each 2 input neurons in one row. The memory-write process is repeated for  $\left[\left(I/(W_{W-mem}/N)\right)\right] = 100$  rows, and then the next N = 64 weights of outgoing edges from each input neuron are written (in this case we only have 36 weights left, as there exist a total of 100 outgoing edges from each input neuron, 64 of which is previously stored) in the next  $\left[\left(I/(W_{W-mem}/N)\right)\right] = 100$ rows. At processing time, by using the NPE(2,64) configuration, the TCD-NPE consumes N = 64 weights in each cycle. Hence, with one read from W-Mem, it receives the weights needed for  $W_{W-mem}/N = 128/64 = 2$  cycles, reducing the number of memory accesses by half.

The FM memory, on the other hand, is divided into B = 2 segments. Assuming that the width of FM memory is  $W_{FM-mem} = 64$  words, each segment can store  $W_{FM-mem}/B = 64/2 = 32$  input features. The memory, as shown in Fig. 2.7, is filled by writing the input

features of each batch into subsequent rows of each virtually segmented memory. Note that both FM-Mem and W-Mem should be word writable to support writing to a section of a row without changing the value of other memory bits in the same row. The input features from each batch is written to the  $\lceil (I/(W_{FM-mem}/B)) \rceil = \lceil (200/(64/2)) = 7 \rceil$  rows. At processing time, using the NPE(2,64) configuration, the TCD-NPE in one access (Reading one row) will receive  $W_F/B$  input features from B different batches and store them in a buffer. In each subsequent cycle, it consumes one input from each batch, hence, the arrangement of data and sequential read of data into a buffer will reduce the number of memory accesses by a factor of  $W_{FM-mem}/B = 64/2 = 32$ .

#### Local Distribution Network (LDN)

The Local Distribution Networks (LDN) interface the read/write buffers and the Network on Chip (NOC). They manage the desired multi- or uni-casting scenarios required for distributing the filter values and feature values across TGs. Figure 2.8 illustrate an example of LDNs in an NPE constructed using  $6 \times 3$  array of TCD-MACs. As illustrated in this example, the LDNs are used for 1) reading/writing from/to buffers of FM-mem while supporting the desired multi-/uni-casting configuration (generated by controller) to support the selected NPE(K, N) configuration (Fig.2.8.A) and 2) reading from W-mem buffer and multi-/uni-casting the result into TGs (Fig.2.8.B). Note that the LDN in Fig, 2.8 is specific to NPE of size  $6 \times 3$ . For other array sizes, a similar LDN should be constructed.

Figure 2.8: An example of LDN for managing the connection between a  $(6 \times 3)$ -PE-array's NoC and memory. (A).left: LDN for writing from NoC data bus to FM-mem. (A).right: LDN for reading from FM-mem to NoC bus. (B): LDN for reading from W-mem into NoC filter bus. The FM-mem in this case, is divided into 6 partitions, supporting the simultaneous process of 6 batches at a time.

## 2.4 Results

In this section, we first evaluate the Power, Performance, and Area (PPA) gain of using TCD-MAC, and then evaluate the impact of using the TCD-MAC in our proposed TCD-NPE. The TCD-MAC and all MACs evaluated in this section operate on signed 16-bit fixed-point inputs.

### 2.4.1 Evaluation and Comparison Framework

The PPA metrics are extracted from the post-layout simulation of each design. Each MAC is designed in VHDL, synthesized using Synopsis Design Compiler [43] using 32nm standard cell libraries, and is subjected to physical design (targeting max frequency) by using the Synopsys reference flow in IC Compiler [44]. The area and delay metrics are reported using Synopsys Primetime [45]. The reported power is the averaged power across 20K cycles of simulation with random input data that is fed to Prime timePX [45] in FSDB format. The general structure of MACs used for comparison is captured in Fig. 2.1. We have

| MAC Type   | $Area(\mu m^2)$ | $\mathbf{Power}(\mu w)$ | Delay(ns) | $\mathbf{PDP}(pJ)$ |

|------------|-----------------|-------------------------|-----------|--------------------|

| (BRx2, KS) | 8357            | 467                     | 2.85      | 13.31              |

| (BRx2, BK) | 8122            | 394                     | 3.3       | 13                 |

| (BRx8, BK) | 7281            | 383                     | 3.14      | 12.03              |

| (BRx4, BK) | 6437            | 347                     | 3.35      | 11.62              |

| (WAL, KS)  | 7171            | 346                     | 3.04      | 10.52              |

| (WAL, BK)  | 6520            | 334                     | 3.13      | 10.45              |

| (BRx4, KS) | 6551            | 393                     | 2.47      | 9.71               |

| (BRx8, KS) | 7342            | 354                     | 2.63      | 9.31               |

| TCD-MAC    | 5004            | 320                     | 1.57      | 5.02               |

Table 2.1: PPA comparison between various MACs and TCD-MAC.

compared our solution to a wide array of MACs. In these MACs, for multiplication, we used Booth-Radix-N (BRx2, BRx4, BRx8) and Wallace implementations. For addition we have used Brent-Kung (BK) and Kogge-Stone (KS) adders. Each MAC is identified by the tuple (Multiplier choice, Adder choice).

### 2.4.2 TCD-MAC PPA Assessment

Table 2.1 captures the PPA comparison of the TCD-MAC against a popular set of conventional MAC configurations. As reported, the TCD-MAC has a smaller overall area, power and delay compare to all reported MACs. Using TCD-MAC provide 23% to 40% reduction in area, 4% to 31% improvement in power, and an impressive 46% to 62% improvement in PDP when compared to other reported conventional MACs.

Note that this improvement comes with the limitation that the TCD-MAC takes one extra cycle to generate the correct output when working on a stream of data. However, the power and delay saving of TCD-MAC significantly outweigh the delay and power for one extra computational cycle. To illustrate this, the throughput and energy improvement of using a TCD-MAC for processing different sizes of input streams (1, 10, 100, 1000) is compared against selected conventional MACs and is reported in Table 4.6. As illustrated, when using the TCD-MAC for processing an array of inputs, the power and delay savings quickly outweigh the delay and power of the added cycle as input stream size increases.

| Mac Type   | Th | Throughput improvement(%) |     |      | Energy Improvement(% |    |     | vement(%) |  |

|------------|----|---------------------------|-----|------|----------------------|----|-----|-----------|--|

| Mac Type   | 1  | 10                        | 100 | 1000 | 1                    | 10 | 100 | 1000      |  |

| (BRX2, KS) | 25 | 59                        | 62  | 63   | -10                  | 40 | 45  | 45        |  |

| (BRX2, BK) | 23 | 58                        | 62  | 62   | 5                    | 48 | 52  | 53        |  |

| (BRX8, BK) | 17 | 55                        | 58  | 59   | 0                    | 45 | 50  | 50        |  |

| (BRX4, BK) | 14 | 53                        | 57  | 57   | 7                    | 49 | 53  | 54        |  |

| (WAL, KS)  | 5  | 48                        | 52  | 53   | -3                   | 44 | 48  | 49        |  |

| (WAL, BK)  | 4  | 48                        | 52  | 52   | 0                    | 45 | 50  | 50        |  |

| (BRX4, KS) | -3 | 44                        | 48  | 49   | -27                  | 31 | 36  | 37        |  |

| (BRX8, KS) | -7 | 41                        | 46  | 47   | -19                  | 35 | 40  | 41        |  |

Table 2.2: Percentage improvement in throughput and energy when using a TCD-MAC (as opposed to a conventional MAC) to process an stream of 1, 10, 100 and 1000 multiplication and addition operations.

### 2.4.3 TCD-NPE Evaluation

In this section, we describe the result of our TCD-NPE implementation as described in section 2.3.2. Table 2.3-top summarizes the characteristics of TCD-NPE implemented, the result of which is reported and discussed in this section. For physical implementation, we have divided the TCD-NPE into two voltage domains, one for memories, and one for the PE array. This allows us to scale down the voltage of memories as they had considerably shorter cycle time compared to that of PE elements. This choice also reduced the energy consumption of memories and highlighted the saving resulted from the choice of MAC in the PE-array. Note that the scaling of the memory voltage could be even more aggressive than what implemented in our solution; In several prior work [46–50], it was shown that it is possible to significantly reduce the read/write/retention power consumption of a memory unit by aggressively scaling it supplied voltage while deploying architectural fault tolerance techniques and solutions to mitigate the increase in the memory write/retention failure

rate. On top of that, learning solutions are also approximate in nature, and inherently less sensitive to small disturbance to their input features. This inherent resiliency could be used to deploy fault tolerant techniques to only protect against bit errors in most significant bits of input feature map, resulting in reduced complexity of deployed fault tolerance scheme.

Table 2.3-bottom captures the overall PPA of the implemented TCD-NPE extracted from our post layout simulation results which are reported for a Typical Process, at 85C° temperature, when the PE-array and memory elements voltages are set according to Table 2.3.

Table 2.3: TCD-NPE implementation details and PPA results. In this table, we have only reported the leakage power. The dynamic power is activity dependent. The breakdown of energy consumption for processing different benchmarks is reported in Fig. 2.10

| Feature                    | Detail                    | Feature            | Detail             |

|----------------------------|---------------------------|--------------------|--------------------|

| PE-array                   | $16 \times 8$             | Processing Element | TCD-MAC            |

| Input Data Format          | Signed 16-bit fixed-point | Data Flow          | OS                 |

| W-mem size                 | 512 KByte                 | Activation Units   | Relu               |

| FM-mem Size                | $2 \times 64$ KByte       | PE-array voltage   | $0.95\mathrm{V}$   |

| Mapper                     |                           | Mem voltage        | 0.70V              |

| Area                       | $3.54 \text{ mm}^2$       | Max Frequency      | 636 MHz            |

| PE-array Area              | $0.724 \text{ mm}^2$      | Memory Area        | $2.5 \text{ mm}^2$ |

| <b>Overall Leak.</b> Power | $75.5 \mathrm{mW}$        | Memory Leak. Power | $51.7 \mathrm{mW}$ |

| PE-array Leak. Power       | 6.4 mW                    | Others Leak. Power | $17 \mathrm{mW}$   |

To compare the effectiveness of TCD-NPE, we compared its performance with a similar NPE which is composed of conventional MACS. According to the discussion in section 2.2, we limit our evaluation to the processing of MLP models. Hence, the only viable data flows are OS and NLR. The TCD-MAC only supports OS, however, by replacing a TCD-MAC with a conventional MAC, we can also compare our solution against OS and NLR. We compare 4 possible data flows that are illustrated in Fig. 2.9. In this Fig. The case (A) is NLR data flow (supported only by conventional MAC) for computing the Neuron values

by forming a systolic array withing the PE-array. The case (B) An NLR data flow variant according to [2] when the computation tree is unrolled and mapped to the PEs, forcing the PE to either act as an adder or multiplier. The case (C) is the OS data flow realized by using conventional MAC. And, finally, the case (D) is the OS data flow implemented using TCD-NPE.

Figure 2.9: Four possible data flow for processing an MLP model. (A): NLR data flow using conventional MACs to form a systolic array. (B): RNA data flow resulted from unrolling the MLP model and mapping the computation tree to conventional MACs (each used as either multiplier or adder) as described in [2]. (C) The OS data flow using conventional MAC. (D): The OS dataflow using TCD-MAC.

For OS dataflows, we have used the algorithm 1 to schedule the sequence of computational rounds. We have compared the efficiency of each of four data flows (described in Fig. 2.9) on a selection of popular MLP benchmarks characteristic of which is described in Table. 2.4.

| Applications          | Dataset       | Topology           |

|-----------------------|---------------|--------------------|

| Digit Recognition     | MNIST         | 784:700:10         |

| Census Data Analysis  | Adult         | 14:48:2            |

| FFT                   | Mibench data  | 8:140:2            |

| Data Analysis         | Wine          | 13:10:3            |

| object Classification | Iris          | 4:10:5:3           |

| Classification        | poker Hands   | 10:85:50:10        |

| Classification        | Fashion MNIST | 728:256:128:100:10 |

Table 2.4: MLP benchmarks used in this work [1].

As illustrated in Fig. 2.10.left, the execution time of the TCD-NPE is almost half of an NPE that uses a conventional MAC in either OS or NLR data flow, and significantly smaller than the RNA data flow (an NLR variant) that was proposed in [2]. Fig. 2.4.right captures the energy consumption of the TCD-NPE and compares that with a similar NPE constructed using conventional MACs. For each benchmark, the energy consumption is broken into 1) computation energy of PE-array, 2) the leakage of the PE-array, 3) the leakage of the memory, and 4) the dynamic energy of memory (and buffer combined). Note that the voltage of the memory is scaled to a lower voltage, as described in table 2.3. This choice was made as the cycle time of the PE's was significantly shorter than the memory cycle times. The scaling of the memory voltage increased its associated cycle time to one cycle, however, significantly reduced its dynamic and leakage power, making the PE-array energy consumption the largest energy consumer. In addition, note that by sequentially shaping the data in the memories, and usage of buffers, we significantly reduced the number of required memory accesses, resulting in a significant reduction in the dynamic power consumption of the memories. As illustrated, the TCD-NPE not only produces the fastest solution but also produces the least energy-consuming solutions across all NPE configurations, all data flows and all simulated benchmarks.

Figure 2.10: Comparison of TCD-NPE with an NPE constructed using conventional MACs that uses the OS, NLR, or RNA data flow. top): Execution time for various MLP benchmarks. Bottom): Energy consumption for various MLP benchmarks.

## 2.5 Conclusion

In this chapter, we introduced the concept of temporal carry bits and used the concept to design a novel MAC for efficient stream processing (TCD-MAC). We further proposed the design of a Neural Processing Engine (TCD-NPE) that is architected using an array of TCD-MACs as its processing element. We, further, proposed a novel scheduler that schedules the sequence of events to process an MLP model in the least number of computational rounds in the proposed TCD-NPE. We reported that the TCD-NPE significantly outperform similar neural processing solutions that are constructed using conventional MACs in terms of both energy consumption and execution time (performance).

# Chapter 3: NESTA: Hamming Weight Compression-Based Neural Processing Engine

## 3.1 Introduction and Background

Deep learning models that deploy Convolutional Neural Networks (CNN) for feature extraction have become increasingly popular in recent years [51]. The popularity of these learning solutions stems from their ability to achieve unprecedented accuracy, surpassing that of human's ability, for various tasks such as object and scene recognition [3,4,27,28,31,52–55], object detection, and object localization[56,57]. This, as illustrated in Table 3.1, is made possible by using deep and complex neural networks expressed using specialized frameworks such as Caffe [58], PyTorch [59] and Tensorflow [5], and trained and executed in acceptable time by Graphical Processing Units (GPU).

Although innovation in parallel computing has enabled us to train and execute such complex models, the applicability of such models remains limited due to their computational and storage requirements. These state of the art CNNs require up to hundreds of megabytes for a model and partial result storage and 30k-600k operations per input pixel [10]. The high computational complexity of these models, in turn, poses energy (power) and throughput (delay) challenges to the underlying hardware. Typically, in such learning solutions the majority (over 90%) of computational complexity is for processing the convolution (CONV) layers [60].

The generality of a processing engine significantly affects the throughput and energy efficiency of neural processing hardware[39][9]. The more general the hardware, the less efficient (in terms of delay and power) the computation becomes. The least attractive solutions are generated by running CNNs on general-purpose CPUs. Utilizing more specialized hardware such as GPUs and FPGAs provide a significant improvement in the efficiency of computation, while most efficient computing, with an order(s) of magnitude improvement in performance and power consumption, is reported when specialized ASIC accelerators such as Eyeriss[10], Diannao[7], Dadiannao[8], or Shidiannao[37] are deployed. The major difference in the performance of ASIC accelerator solutions, previously proposed in [7–10, 37, 39, 63–66], is on the type of data flow implemented for maximizing data reuse (weight, partial sum, and activation value) and minimizing memory access. This is when the neural Processing Elements (PE), that implement the multiply-accumulate (MAC) function, remain non-optimized in these accelerator solutions.

Table 3.1: Depth and complexity of some of the existing and modern CNN solutions for object detection.

|                            | AlexNet[4]       | VGG[3] | GoogLeNet[52]   | Resnet[53]      |

|----------------------------|------------------|--------|-----------------|-----------------|

| Top5 Accuracy              | 80.2%            | 89.6%  | 89.9%           | 96.3%           |

| layers                     | 8                | 19     | 22              | 152             |

| FLOPS                      | $729 \mathrm{M}$ | 19.6G  | $1.5\mathrm{G}$ | 11.3G           |

| FLOPS in $3 \times 3$ CONV | 118M             | 19.5G  | 1.18G           | $6.7\mathrm{G}$ |

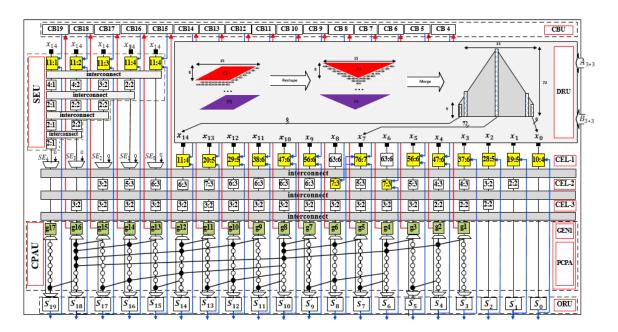

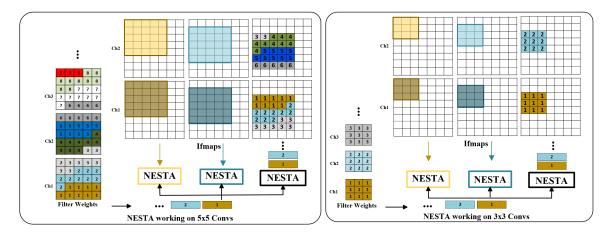

We claim that the architecture of PEs in an ASIC DNN accelerator could significantly improve when the computational model, data locality, and data reuse concepts are used to architect a DNN/CNN specific PE. We propose NESTA as a PE that is designed based on these principles. To reduce data movement, and minimize the generation of partial sums, NESTA consumes 9 values of the convolution at a time (equal to the size of a  $3 \times 3$  convolution) until all filter-image pairs of a convolution across all channels are consumed. To significantly speed up the computation and reduce energy consumption, NESTA does not use adders or multipliers. Instead, it converts the convolution into a sequence of N compression and one final addition. The add operation transforms the compressed and accumulated result into a correct partial sum.

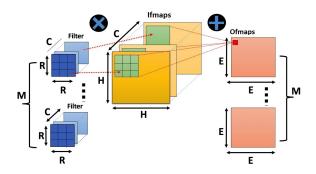

Figure 3.1: Computing one CONV layer using input Ifmap/image and filters to produce the output (Ofmaps)

Figure 3.2: comparing the architecture of A) a typical MAC, versus B) a simplified 2-input version of NESTA. In all variables in the form of  $D_m^i$ , the subscript (m) captures the bit position values, and postscript (i) capture the cycle (iteration). For example,  $A^i, B^i$  are the input data in the  $i^{th}$  iteration (corresponding to the  $i^{th}$  cycle) of the multiply accumulate operation. The  $b_m^i, a_m^i$ , and  $p_m^i$  are accordingly the  $m^{th}$  significant bits of inputs A, B, and partial sum at the  $i^{th}$  cycle (iteration). The division of CPA into GEN and PCPA is also shown in this figure. Note that the *PCPA* is only executed at the last cycle.

## **3.2** NESTA: Proposed Processing Engine

Before describing our proposed solution, we first explain the concept of *temporal carry* in a miniaturized solution in section 3.2.1, then we explain the concept of *compression and expansion* in section 3.2.2. Finally, in section 3.2.3, we use these concepts to construct and describe our proposed solution.

## **3.2.1** Motivation 1: Temporal Carry

Suppose two vectors A and B each have N 8-bit values, and the goal is to compute their dot product,  $\sum_{i=0}^{N-1} (A_i * B_i)$  (similar to what is done during the activation process of each neuron in a NN). This could be accomplished using a single Multiply-Accumulate (MAC) unit and working on 2 inputs at a time for N rounds. Fig. 3.2(A-right) shows the General view of a typical MAC architecture that comprised of two parts multiplication and addition. We have assumed that a Carry Propagation Adder (CPA) is used as adder unit for reducing the MAC delay. More detailed view of this architecture, 3.2(A-left), reveals that for generating the final result, the CPA will be executed 2N times, N times for producing the results of N multiplications and N times for accumulating the result of multiplications. These CPAs are located at the critical path of this architecture so eliminating them lead to a performance gain. Fig. 3.2(A-right) captures how CPA has been broken into GEN (which is highlighted in red), and PCPA (Partial CPA).