# METAL CONTACTS ON LOW-DIMENSIONAL MATERIALS

by

Hui Yuan A Dissertation Submitted to the **Graduate Faculty** of George Mason University in Partial Fulfillment of The Requirements for the Degree of Doctor of Philosophy

Electrical and Computer Engineering

| Committee: |                                                           |

|------------|-----------------------------------------------------------|

|            | _ Dr. Qiliang Li, Dissertation Director                   |

|            | _ Dr. Rao V. Mulpuri, Committee Member                    |

|            | Dr. Dimitrios E. Ioannou, Committee Member                |

|            | _ Dr. Erhai Zhao, Committee Member                        |

|            | _ Dr. Guangjun Cheng, Committee Member                    |

|            | _ Dr. Curt A. Richter, Committee Member                   |

|            | _ Dr. Monson H. Hayes, Department Chair                   |

|            | Dr. Kenneth S. Ball, Dean, Volgenau School of Engineering |

| Date:      | Fall Semester 2014 George Mason University Fairfax, VA    |

## Metal Contacts on Low-Dimensional Materials

A Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

by

Hui Yuan

Bachelor of Engineering, Electronic Science and Technology, Wuhan University, 2006

Master of Science, Condensed Matter Physics, Wuhan University, 2009

Director: Qiliang Li, Professor Department of Electrical and Computer Engineering

> Fall Semester 2014 George Mason University Fairfax, VA

Copyright 2014 Hui Yuan All Rights Reserved

## **ACKNOWLEDGEMENTS**

I would like to thank my friends and colleagues who have helped me to make this happen. My advisor, Prof. Qiliang Li, guided me in my research. My supervisor, Dr. Curt A. Richter, in National Institute of Standards and Technology, Gaithersburg, MD, helped me on many technical issues in my research. Dr. Guangjun Cheng taught me the research and analysis of the experiment data on  $MoS_2$  materials. Also, I very much appreciate Professors Dimitrios E. Ioannou, Erhai Zhao, and Rao V. Mulpuri for their advice and help. Finally, my earnest thanks go to my parents who have supported me for all time.

# **TABLE OF CONTENTS**

|                                                                                                  | Page |

|--------------------------------------------------------------------------------------------------|------|

| List of Figures                                                                                  |      |

| Abstract                                                                                         | ix   |

| Chapter 1: Background and Introduction                                                           | 1    |

| 1.1 Emerging Applications of Low-Dimensional Materials in MOSFETs                                | 1    |

| 1.2 Challenges in Metal Contacts on Low-Dimensional Materials                                    | 3    |

| 1.2.1 CMOS Scaling and SiNW Contact Characterization                                             | 4    |

| 1.2.2 Interface Impacts in MoS <sub>2</sub> Metal Contacts                                       | 5    |

| 1.2.3 Current Crowding in Metal Contacts on MoS <sub>2</sub>                                     | 9    |

| 1.3 Overview of Dissetation                                                                      | 10   |

| Chapter 2: Contact Characterization on Ambipolar SiNW FETs Based on Gate-ass<br>Kelvin Structure |      |

| 2.1 Introduction                                                                                 | 12   |

| 2.2 Contact Resistance Dependence on Electron Transport Direction in Ambipo SiNW FET             |      |

| 2.2.1 Device Structure and Fabrication                                                           | 14   |

| 2.2.2 Results and Discussion                                                                     | 17   |

| 2.2.3 Conclusion                                                                                 | 23   |

| 2.3 Inverter on a Single SiNW                                                                    | 23   |

| Chapter 3: Role of Interface Morphology on Metal Contacts to MoS <sub>2</sub>                    | 28   |

| 3.1 Introduction                                                                                 | 28   |

| 3.2 Experimental Methods                                                                         | 30   |

| 3.2.1 Sample Preparation:                                                                        | 30   |

| 3.2.2 Characterizations:                                                                         | 33   |

| 3.3 Results and Discussion                                                                       | 34   |

| 3.3.1 Electrical Characterization of MoS <sub>2</sub> transistors                                | 34   |

| 3.3.2 Surface Morphology of Metal Thin Films on MoS <sub>2</sub>                                 | 38   |

| 3.3.3 Raman Spectroscopy of MoS <sub>2</sub> Covered with Metal                 | 42          |

|---------------------------------------------------------------------------------|-------------|

| 3.4 Conclusion                                                                  | 48          |

| Chapter 4: Gate Effects and Current Crowding in Metal/MoS <sub>2</sub> Contacts | 49          |

| 4.1 Introduction                                                                | 49          |

| 4.2 Experimental                                                                | 51          |

| 4.3 Results and Discussion                                                      | 54          |

| Chapter 5: Summary and Prospectiv Future Plan                                   | 63          |

| 5.1 Summary of the Dissertation                                                 | 63          |

| 5.2 Prospective Future Plan                                                     | 64          |

| Appendix A: Polarization of Bi2Te3 Thin Film in a Floating-Gate Capacitor St    | ructure. 66 |

| A.1 Introduction                                                                | 66          |

| A.2. Experimental                                                               | 68          |

| A.3 Results and discussion                                                      | 70          |

| A.4 Conclusion                                                                  | 78          |

| References                                                                      | 79          |

|                                                                                 |             |

# LIST OF FIGURES

| Figure Page                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------|

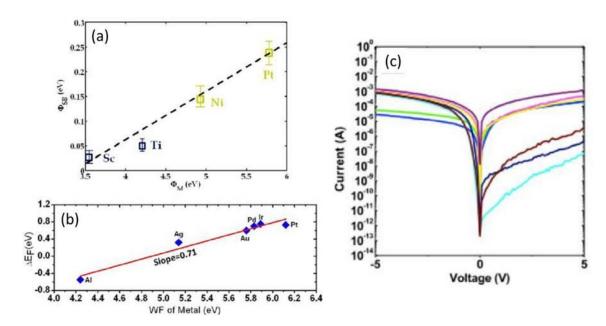

| Figure 1.1 Complications in metal contacts on MoS <sub>2</sub> . (a) Schottky barrier height changes                 |

| in experiment where metals with different Fermi levels are used. The Fermi level                                     |

| is pinned to the edge of conduction band. (b) MoS <sub>2</sub> Fermi level changes after                             |

| different metal contacts are applied in theoretical simulations. (c) I-V                                             |

| characteristics measured at different locations on a single piece of MoS2with the                                    |

| tungsten probe directly contacting the MoS <sub>2</sub>                                                              |

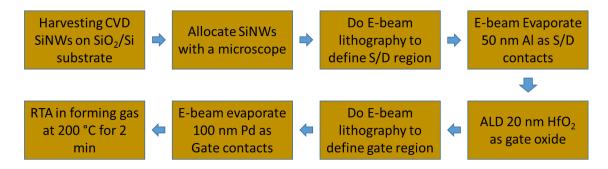

| Figure 2.1 Fabrication process of SiNW transistors                                                                   |

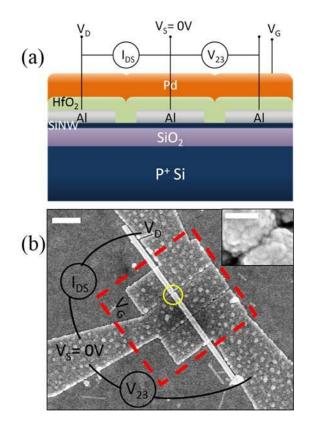

| Figure 2.2 Device structure and measurement set-up. (a) Schematic of device structure                                |

| and measurement set-up. (b) Scanning electron microscopic image of the SiNW                                          |

| gate assisted Kelvin test structure. Yellow circle shows the SiNW FET (channel                                       |

| length: 50 nm). The inset in (b) shows the magnified image of the yellow circled                                     |

| region. Scale bars in (b) and inset are 1 µm and 100 nm long, respectively 15                                        |

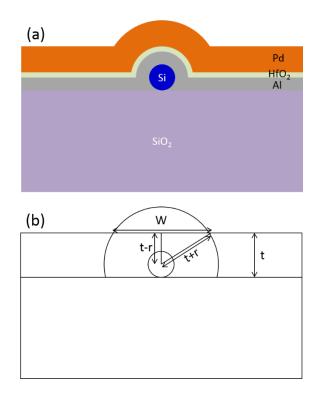

| Figure 2.3 Scheme of the cross section off the SiNW under S/D contacts                                               |

| contact characteristics selected by negative $V_{GS}$ . Electron contact characteristics                             |

| selected by positive V <sub>GS</sub> : (c) electrons flow from Al to the SiNW channel; (d)                           |

| electrons flow from the SiNW channel to Al                                                                           |

| Figure 2. 5 Diffusion of Al in silicon: (a) Al concentration before annealing at 300°C for                           |

| 30 minutes in O <sub>2</sub> . (b) Al concentration after annealing at 300°C for 30 minutes in                       |

| O <sub>2</sub>                                                                                                       |

| Figure 2.6 Band diagram from channel center to the contact at different conditions: (a)                              |

| Equilibrium state. (b) $V_{DS} < 0$ and $V_{DS} < 0$ : hole flow from Al to SiNW. (c) $V_{GS} > 0$                   |

| 0 and $V_{DS} > 0$ : electrons flow from Al to SiNW (d) $V_{GS} > 0$ and $V_{DS} < 0$ :                              |

| electrons flow from SiNW to Al. 22                                                                                   |

| Figure 2. 7 SEM image and measure set-up of the inverter                                                             |

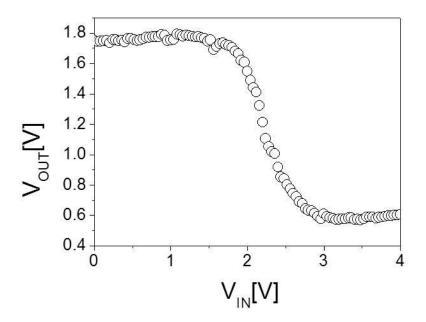

| Figure 2.8 Voltage transfer characteristics of single nanowire CMOS inverter under $V_{DD}$                          |

| = 2 V and $V_{IN} = 0 \sim 4 V_{IN}$ 26                                                                              |

| Figure 3.1 MoS <sub>2</sub> flake on SiO <sub>2</sub> /Si substrate. (a) AFM image of a MoS <sub>2</sub> flake which |

| includes monolayer, trilayer and multiple layer regions. (b) Optical image of the                                    |

| same flake. (c) Raman spectra of different thickness MoS <sub>2</sub> which is collected                             |

| from the different positions on the same flake of MoS <sub>2</sub>                                                   |

| Figure 3. 2 MoS <sub>2</sub> transistor diagram and Drain current density of single-layer MoS <sub>2</sub>           |

| transistors: (a) MoS <sub>2</sub> transistor diagram Drain current density of single-layer                           |

| MoS <sub>2</sub> transistors versus (b) $V_G$ - $V_{th}$ with Ag or Ti contacts, and (c, d) drain voltage            |

| $(V_{DS})$ with (c) Ag or (d) Ti contacts                                                                            |

| Figure 3.3 Drain current density of few-layer MoS <sub>2</sub> transistors versus (a) V <sub>G</sub> -V <sub>th</sub> with Ag                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| or Ti contacts, and (b, c) drain voltage (V <sub>D</sub> ) with (b) Ag or (c) Ti contacts 37                                                           |

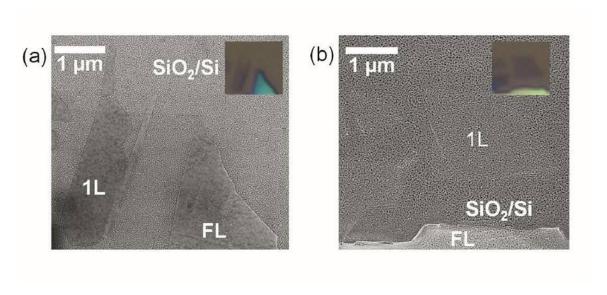

| Figure 3.4 SEM images of MoS <sub>2</sub> on SiO <sub>2</sub> /Si substrate after (a) Au / Ag deposition and (b)                                       |

| Au/Ti deposition. The insets show corresponding optical image of pristine MoS <sub>2</sub>                                                             |

| before metal deposition. The locations of monolayer MoS <sub>2</sub> (1L) and few-layer                                                                |

| MoS <sub>2</sub> (FL) are identified after metal deposition                                                                                            |

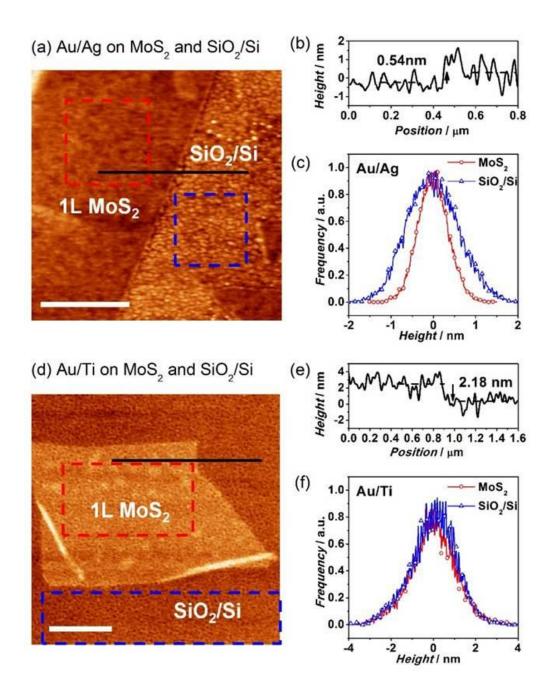

| Figure 3.5 AFM and roughness analysis of metal on MoS <sub>2</sub> and SiO <sub>2</sub> /Si substrate: (a)                                             |

| Topography of Au/Ag on MoS <sub>2</sub> and SiO <sub>2</sub> /Si. (b) A topographic line profile of the                                                |

| height along the slide line indicated in figure (a). (c) Normalized histograms of                                                                      |

| height distribution of areas indicated by the square in figure (a). (d) Topography                                                                     |

| of Au/Ti on MoS <sub>2</sub> and SiO <sub>2</sub> /Si. (e) A topographic line profile of the height along                                              |

| the slide line indicated in figure (d). (f) Normalized histograms of height                                                                            |

| distribution of areas indicated by the square in figure (c). Scale bars are 500nm                                                                      |

| long for image (a) and (d).                                                                                                                            |

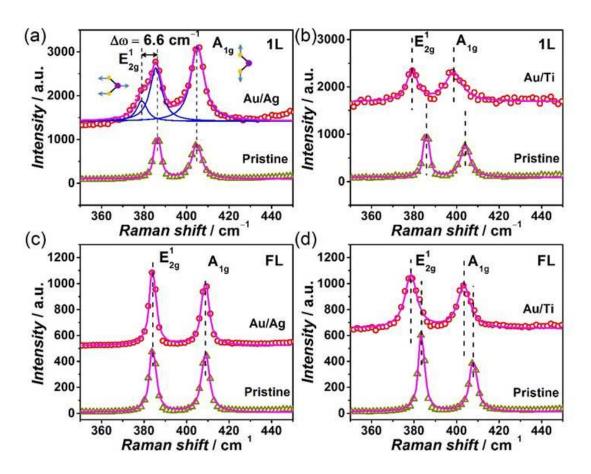

| Figure 3.6 Comparison of Raman spectra before and after (a) Au/Ag or (b) Au/Ti                                                                         |

| deposition on monolayer (1L) MoS <sub>2</sub> and before and after (c) Au/Ag or (d)Au/Ti                                                               |

| deposition on few-layer (FL) MoS <sub>2</sub> . The scatters are real data and solid lines are                                                         |

| fitted Lorentz peaks                                                                                                                                   |

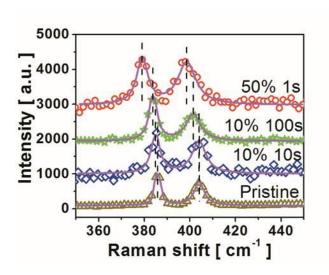

| Figure 3. 7 Raman spectra on Au/Ti covered MoS <sub>2</sub> with different power and signal                                                            |

| collection time. Scatters are experimental data and solid lines are fitted curves 47                                                                   |

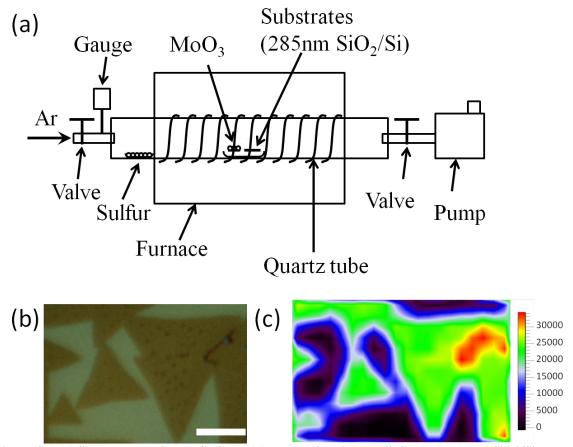

| Figure 4. 1 (a) System set-up for MoS <sub>2</sub> CVD. (b) Image of typical MoS <sub>2</sub> flakes grown on                                          |

| SiO2/Si substrate. The scale bar is 5 μm. (c) Device schematic                                                                                         |

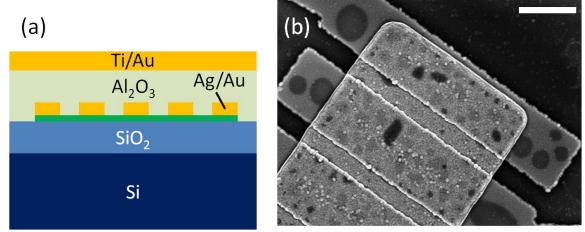

| Figure 4.2 Device structure: (a) Schematics of MoS <sub>2</sub> FETs (b) SEM image of a MoS <sub>2</sub>                                               |

| transistor. Scale bar in this image is 1 µm                                                                                                            |

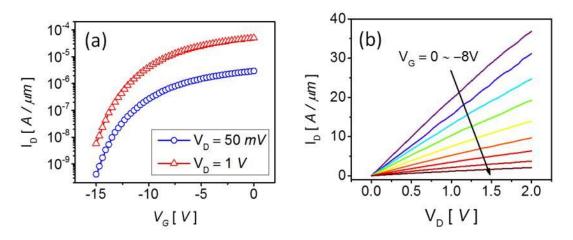

| Figure 4.3 I-V characterization of a representative $MoS_2$ FET: (a) $I_D$ - $V_G$ , and (b) $I_D$ - $V_D$                                             |

| characteristic                                                                                                                                         |

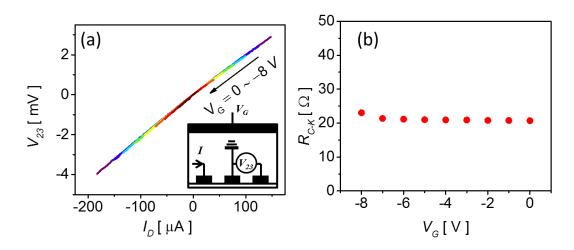

| Figure 4.4 Gate assisted Kelvin test: (a) $V_{23}$ - $I_D$ measured at different $V_G$ , inset is the                                                  |

| illustration of the measurement set-up; (b) $R_{C-K}$ extracted from the linear fitting of                                                             |

| $V_{23}$ and $I_D$ at different $V_G$                                                                                                                  |

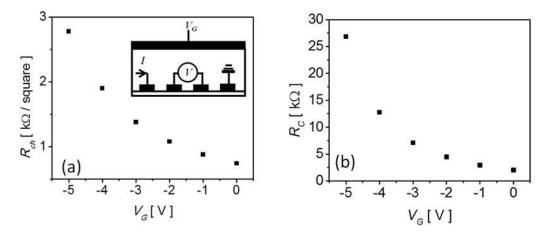

| Figure 4.5 Gate assisted 4-probe measurement. (a) Channel sheet resistance at different                                                                |

| $V_G$ , inset is the measurement set-up for gate assisted 4-probe measurement. (b)                                                                     |

| Contact resistance ( $R_C$ ) extracted from 4-probe measurement                                                                                        |

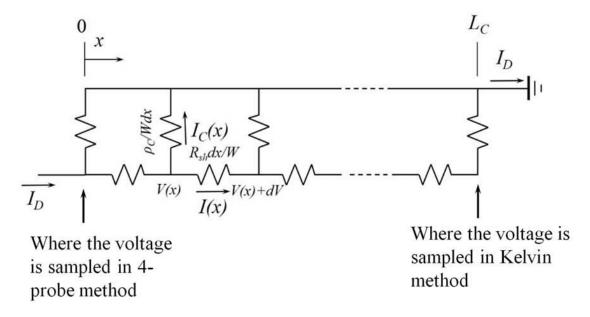

| Figure 4.6 TLM model for contact resistance. The positions where the voltage is sampled                                                                |

| in Kelvin method and 4-probe measurement are pointed                                                                                                   |

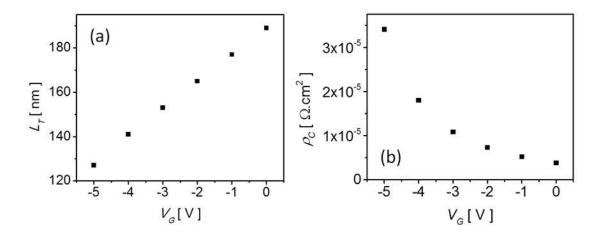

| Figure 4.7 (a) Current transfer length and (b) Contact resistivity at different $V_G$                                                                  |

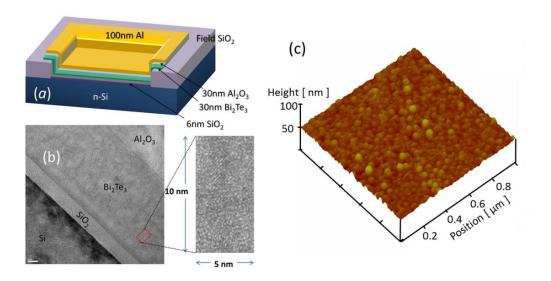

| Figure A.1 (a) Schematic of the capacitor with Al/Al <sub>2</sub> O <sub>3</sub> /Bi <sub>2</sub> Te <sub>3</sub> /SiO <sub>2</sub> /Si structure. (b) |

| High-resolution transmission electron microscopy (HRTEM) image of the                                                                                  |

| capacitor cross-section. The scale bar is 5 nm in the image. The rectangular                                                                           |

| HRTEM image ( $10\text{nm} \times 5\text{nm}$ ) on the right is an amplification of the Bi <sub>2</sub> Te <sub>3</sub> film                           |

| within the red rectangle on the left image, showing the polycrystalline structure in                                                                   |

| the film. (c) AFM image of Bi <sub>2</sub> Te <sub>3</sub> film grown on SiO <sub>2</sub> with OH-hydroxyl groups                                      |

| by ALD                                                                                                                                                 |

| Figure A.2 (a) Capacitance-Voltage (C-V) characteristics of the Bi <sub>2</sub> Te <sub>3</sub> capacitor                                              |

| structure at 1 MHz with different voltage sweep ranges. The area of the capacitor                                                                      |

|        | is 100 $\mu$ m $\times$ 100 $\mu$ m. (b) The polarization difference changes versus the applied             |

|--------|-------------------------------------------------------------------------------------------------------------|

|        | voltage. (c) Illustration of the charge separation and polarization of Bi <sub>2</sub> Te <sub>3</sub> when |

|        | an external field is applied                                                                                |

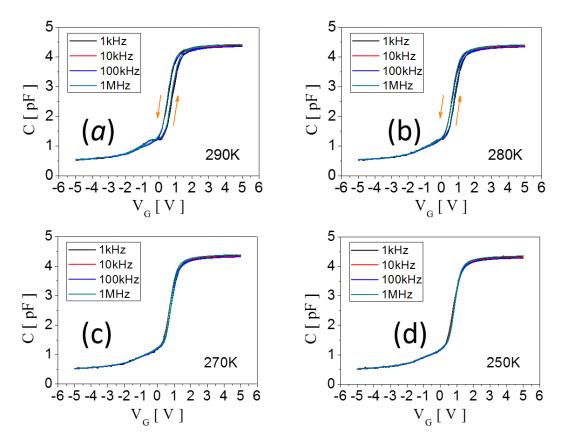

| Figure | A.3 C-V characteristics the Bi <sub>2</sub> Te <sub>3</sub> capacitor structure at different frequencies (1 |

|        | kHz to 1 MHz) at different temperatures: (a) 290K, (b) 280K, (c) 270K and (d)                               |

|        | 250K. The hysteresis shift decreases as the temperature decreases                                           |

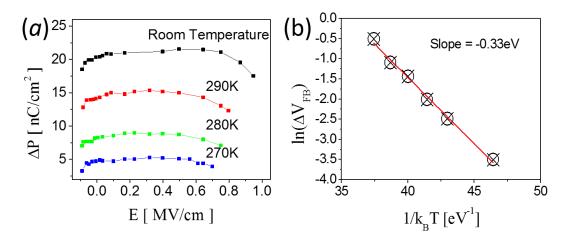

| Figure | A.4 (a) Polarization difference at vs. applied voltage different temperatures. (b)                          |

|        | Memory window vs. temperature. The memory window is shrunk as the                                           |

|        | temperature decreases, indicating that the remnant polarization becomes smaller                             |

|        | at lower temperature. The memory window is fitted as an exponential function of                             |

|        | 1/k <sub>B</sub> T (k <sub>B</sub> T is the thermal activation energy), agreeing well with both the linear- |

|        | and log-scale experimental data. The activation energy is 0.33eV according to the                           |

|        | fitting77                                                                                                   |

|        |                                                                                                             |

**ABSTRACT**

METAL CONTACTS ON LOW-DIMENSIONAL MATERIALS

Hui Yuan, Ph. D.

George Mason University, 2014

Dissertation Director: Dr. Qiliang Li

As the scaling of the microelectronics is reaching nano regime, low-dimensional materials have been of increasing interest for future electronics applications. The lowdimensional materials, such as Si nanowires (SiNWs), carbon nanotubes (CNTs), graphene and transition metal dichalcogenides (TMDs), not only provide small body for further-scaled devices but also bring about new intrinsic properties for application in future optoelectronics, spintronics and so on. However, the small dimensions add significant difficulty for reducing contact resistance in the nanoelectronic devices. This dissertation presents a study of the metal contacts on low-dimensional materials. The focus of this work is on SiNWs and monolayer or few-layer MoS<sub>2</sub>.

First, the metal contact on SiNW field effect transistors (FETs) was studied with a gate assisted Kelvin structure. In this work, I fabricated ambipolar SiNW FETs with Al contacts. The ambipolar characteristics and the gate assisted Kelvin structure enabled the measurement of the contact properties of both electron and hole flows at the same contact. In this work I found that the contact performance is affected by the carrier type that flows in the channel as well as the current direction. In addition, an inverter was designed and realized on a single SiNW leveraged by the ambipolar FET characteristics.

Then, I have studied metal contacts on MoS<sub>2</sub>, which is one of typical two-dimensional semiconductors. In the first part of this work, Ag and Ti contacts on exfoliated MoS<sub>2</sub> monolayers and few-layers are fabricated, characterized and analyzed. Based on the current-voltage (I-V) measurement, surface morphology and Raman spectroscopic measurement, I found that interface morphology plays an important role on the contact performance in MoS<sub>2</sub> FETs. In the second part of this work, gate-assisted contact measurement was carried out on chemical vapor deposited low-dimensional MoS<sub>2</sub> layers. The contact resistance and current crowding have been measured and analyzed at different gate bias. All these findings contribute to the understanding of metal contact on MoS<sub>2</sub>.

SiNWs and  $MoS_2$  are well-representative examples of emerging low-dimensional materials. The gate assisted contact measurement and metrology can also be applied to understand the metal contacts on other emerging low-dimensional materials.

#### CHAPTER 1: BACKGROUND AND INTRODUCTION

## 1.1 Emerging Applications of Low-Dimensional Materials in MOSFETs

As the dimensional scaling of the microelectronics is reaching the fundamental physical and economic limits, more and more low-dimensional materials have been studied for future applications. The representative materials include (but not limited to) semiconductor nanowires (NWs) [1-3], carbon nanotubes (CNTs) [4, 5], graphene [6-8] and transition metal dichalcogenides (TMDs) [9-11]. They not only provide a small body for further down-scaled device, but also bring about new physical properties to be integrated into future optoelectronics, spintronics and so on. The nanowires, such as Si nanowires (SiNWs), can be used in electronic devices for the application of 3-dimensional (3D) device morphology like FinFET [12] in current device technology. Others like III-V compound nanowires have been studied for future photonics applications. The small body with unique properties provides an excellent platform for down-scaling the devices to overcome the physical limit of the conventional 3-dimensional materials.

The surface roughness of ultra-thin body Si on insulator (UTSOI) becomes very large when the thickness approaches to 5 nm. Besides, the quantum confinement significantly enlarges the bandgap of Si when its thickness decreased to 5 nm and below. These situations limit UTSOI applications in further scaled electronics. Fortunately, 2-

dimensional (2D) semiconductors, such as TMDs [13-15] and black phosphorus, [16-18] have an intrinsic thin body with robust crystal structure. Their thickness is normally atomically thin (just couple of atom layers). But they still boast semiconducting properties with a scalable bandgap. In addition, the ultra-thin body and high mechanic strength of 2D materials are advantageous for the flexible and stretchable electronic devices. [19, 20] Also, in recent years, these devices gained much attention for medical applications.

Furthermore, the low-dimensional nature brings about attractive materials properties. For example, CNTs can be conductor or semiconductor according to their charity. [4] The semiconducting CNTs have a high carrier mobility which is attractive for high-frequency applications. [21] Like CNTs, graphene also has a high mobility because carriers in graphene are the massless Dirac fermions. [22] It has also attracted intensive attention for high-frequency applications [8]. Graphene radio frequency (RF) devices with cutoff frequency ( $f_T$ ) of 300 GHz have also been demonstrated. [23] The long spin coherence time exhibited by graphene makes it also an interesting material to be used in spintronics and quantum computing. [24-26]

Unlike the bulk TMDs which are indirect bandgap semiconductor, the monolayer TMDs are usually direct bandgap semiconductor. [27, 28] As a result, they are preferred for both electronics and optoelectronic devices. More recently, researchers demonstrated significant valley polarization in graphene [29, 30] and MoS<sub>2</sub>. [31, 32] This physical property might bring about a new concept of valleytronics into devices.

# 1.2 Challenges in Metal Contacts on Low-Dimensional Materials

Though low-dimensional materials have above-mentioned advantages and prospective for future applications, the small dimensions place significant obstacles on achieving low contact resistance in the electronic devices. As stated in International Technology Roadmap for Semiconductors, 2013 Edition, contact resistance has a large impact on device performance as devices are scaled to smaller dimensions. [33] Theoretically, the contact resistance is determined by the energy alignment between the metal work function and the semiconductor bandgap. However, metal/semiconductor interface usually forms Schottky barrier. Its barrier height cannot be effectively tuned by the metal Fermi level because of Fermi level pinning. [34] In the past, the contact resistance can be reduced with heavily doped semiconductor. In this way, the width of the Schottky barrier at the metal semiconductor interface is greatly reduced so that the tunneling through the barrier is highly enhanced. However, this is not possible in many nanoscale devices as the doping is difficult to control at that small dimensions. In addition, the alloy formed at the contact between metal contacts and semiconductor would consume considerable channel thickness in a nanoscale multigate FET, (e.g., FinFET). Furthermore, for nanomaterial based devices such as carbon nanotube, graphene, or other 2D materials, reducing the barrier height is the only option since the material is extremely thin. Ideally, in order to obtain ultra-low-resistance contacts the metal work function should be aligned with the semiconductor Fermi level. However, Fermi level pinning often has a strong effect on the interface of metal/semiconductor contact. [35-38] Thus, metal Fermi level should not be the only consideration for low

contact resistance. Other factors of the contact interface should also be considered to achieve low contact resistance.

#### 1.2.1 CMOS Scaling and SiNW Contact Characterization

As the dimensional scaling of conventional metal-oxide-semiconductor field effect transistors (MOSFETs) is approaching the fundamental limits, several device structures have been explored to further extend the functionality of complementary metal-oxide-semiconductor (CMOS) technology. [39] Among them, the most attractive devices are nanowire / nanotube field effect transistors (FETs), FinFETs and junction-less FETs.[12, 40-42] For thin, nanoscale sidewall contacts, the contact resistance can be very large and behave differently than in planar devices. The contact mechanism in onedimensional (1D) electronic system [4, 43] and method to minimize contact resistance in Si nanowire transistors [44, 45] have been previously reported. However, proper contact characterization metrology is still an important and urgent issue in nanoelectronics. [41] For a nanoscale channel with low or even intrinsic doping, the resistance of the channel (e.g., ungated current < 1 fA) is too large for conventional measurements. The conventional transfer length method (TLM) [46] and Kelvin test structure [47] are no longer suitable. Also, the conventional cross-bridge Kelvin test structure cannot be fabricated on a one dimensional nanowire. In addition, the resistance of the nanoscale source/drain (S/D) contacts is quite different to the contact measured in the absence of gate electric field, which if present will affect the current crowding at the contact. [48] Furthermore, the extremely small device dimensions will introduce poor doping

uniformity, and the S/D asymmetry can be formed under sufficient bias. The conventional metrologies, such as TLM and 4-probe methods, cannot efficiently and precisely extract the contact resistance of a single contact. [49]

To meet these challenges, we designed a gate-assisted Kelvin test structure based on Si nanowire (SiNW) FETs to study the properties of nanoscale S/D contacts. With the SiNW FET based Kelvin test structure, we can select and measure the contact resistance (R<sub>C</sub>) of a single contact. Also, we can investigate the contact characteristics for pure electron or hole flow at the same contact, and study the effect of carrier flow direction on the contact properties. We selected Si nanowires as a test platform, but the metrology can be applied to other nanoscale devices, such as nanotube FETs and FinFETs.

# 1.2.2 Interface Impacts in MoS<sub>2</sub> Metal Contacts

Recently, layered materials, such as MoS<sub>2</sub> and WSe<sub>2</sub>, have attracted intensive attention for electronic and optoelectronic applications. [10, 11, 50-52] Monolayer and few-layer MoS<sub>2</sub> can be treated as 2-dimensional (2D) semiconductor. Their bandgap ranges from 1.2 eV to 1.8 eV depending on the number of layers. [14, 15, 27] In particular, monolayer MoS<sub>2</sub> has a direct bandgap of 1.8 eV, very attractive for applications in optoelectronics. [27, 53, 54] In addition, the 2D MoS<sub>2</sub> is attractive for flexible electronic applications because of its intrinsic ultrathin body and robust lattice structure. [19, 20, 55] In the consideration of short channel effects in metal-oxide-semiconductor field effect transistors (MOSFETs), the 2D intrinsic ultrathin body represents the ultimately small scale. [56] Moreover, its inert surface has no dangling

bonds, which is advantageous for forming the channel-gate dielectric interface in MOSFETs. Monolayer MoS<sub>2</sub> MOSFET was the first demonstrated 2D TMD semiconductor MOSFET. [9] Such transistors have exhibited a high ON/OFF ratio of 10<sup>8</sup> and decent subthreshold slope of 74 mV/dec which are competent with state of art CMOS technology. [9]

Significant amount of work has been done to understand the transport mechanism in MoS<sub>2</sub> transistors and to improve their performance for future applications. [57-61] The Source/Drain (S/D) contacts are very important factors for device performance. Several contact structures have been used and studied to achieve a good Ohmic contact on MoS<sub>2</sub>. [37, 38, 55, 62-64] It was expected that a metal with lower work function leads to a lower Schottky barrier for electron transport and results in a good n-type contact. [37]

However, the properties of metal contacts on MoS<sub>2</sub> is complicated and often suffers from Fermi level pinning which results in a Schottky barrier not fully tuned by the metal Fermi level. As shown in Fig. 1.1(a), the experimental results from S. Das et al. show that the barrier height between the MoS<sub>2</sub> channel and the metal contact is only weakly influenced by the metal work function and that an n-type barrier is formed between MoS<sub>2</sub> and a high work function metal such as Pt. [37] The theoretical work by C. Gong et al. confirms that partial Fermi level pinning in metal-MoS<sub>2</sub> contacts makes the Fermi levels in all studied metal-MoS<sub>2</sub> complexes except Pt are situated above the midgap of MoS<sub>2</sub>, as shown in Fig. 1.1(b) [38] Additionally, S. McDonnell et al. demonstrated that intrinsic defects in MoS<sub>2</sub> dominated the metal-MoS<sub>2</sub> contact resistance and provide a low Schottky barrier independent of metal contact work function (Fig.

1.1(c)). [62] All above-mentioned results show that metal work function is not a good indicator for forming an Ohmic contact with MoS<sub>2</sub>.

Figure 1.1 Complications in metal contacts on  $MoS_2$ . (a) Schottky barrier height changes in experiment where metals with different Fermi levels are used. The Fermi level is pinned to the edge of conduction band. (b)  $MoS_2$  Fermi level changes after different metal contacts are applied in theoretical simulations. (c) I-V characteristics measured at different locations on a single piece of MoS2 with the tungsten probe directly contacting the  $MoS_2$

Previous studies on metal contacts to graphene or carbon nanotube indicated that the morphology of metal contacts and the interaction between these carbon-based materials and metal play important roles in contact resistance. [64, 65] Although it is well recognized that metal wettability plays an role in metal-MoS<sub>2</sub> contacts, [37] to our best knowledge, there is no work showing the direct evidence on how the metal contact

morphology affects the metal- $MoS_2$  contacts. In this work, for the first time, we have shown how the metal- $MoS_2$  interface influences the  $MoS_2$  FET performance.

Ag was chosen because it has been reported to form a good contact on WSe<sub>2</sub>, [66] which is a similar material to MoS<sub>2</sub>. Previous work also shows that Ag has excellent wettability on bulk MoS<sub>2</sub>. [67] We compare the results from Ag contacts with those from Ti contacts, which are commonly-used metal contacts on MoS<sub>2</sub> in the literature. [9, 37, 54, 68-71] Our results show that, despite of the similar work function around 4.3 eV for both metals,[72] monolayer and few-layer MoS<sub>2</sub> transistors with Ag contacts show significantly better electrical characteristics with more than 60-time higher ON-state current density and steeper subthreshold slopes.

The surface morphology of the metal films was then investigated. 5 nm thin layer of contact metal (Ag or Ti) capped with a 5 nm Au protection layer was deposited on top of MoS<sub>2</sub>. Scanning electron microscopy (SEM) shows that Au/Ag formed a smoother and denser film on MoS<sub>2</sub>. The surface roughness analysis was carried out by atomic force microscopy (AFM). The metal-MoS<sub>2</sub> interface was then investigated by Raman spectroscopy. The Raman spectra reveal that the contacting interface is between MoS<sub>2</sub> and Ag or Ti. The better wettability between Ag and MoS<sub>2</sub> is essential to form smoother and denser Au/Ag contacts on MoS<sub>2</sub>, resulting in a better device performance. The strain effect introduced by Ag and heating effect introduced by Ti to monolayer MoS<sub>2</sub> are also revealed by the Raman spectroscopy.

### 1.2.3 Current Crowding in Metal Contacts on MoS<sub>2</sub>

The current distribution under the metal contacts is an important property of the metal contacts. Some results show that the current would penetrate into the contact on a distance as large as several hundred of nanometers. [70, 73] However, their results are based on back-gated devices in which the channel current was not effectively tuned by the gate, and the Fermi level of MoS<sub>2</sub> under the contacts will be coupled to the back gate voltage. Here, we will present our work on the current crowding effect in metal-MoS<sub>2</sub> contacts which are affected significantly by a top gate. Our previous work shows that gate-assisted test structure is a good approach to test the contacts in low-dimensional electronic system. [74] We will extend the method to MoS<sub>2</sub> and do a cross comparison between Kelvin test structure and 4-probe method.

We fabricated Ag contacted bilayer  $MoS_2$  transistors with 30 nm  $Al_2O_3$  top gate on 300 nm  $SiO_2/Si$  substrate. The dimensions of our transistors are: 0.5  $\mu$ m channel length, 4  $\mu$ m channel width and 1  $\mu$ m contact length. Ag was chosen because it has been reported to form a good contact on  $WSe_2$ , [66] which is a similar material to  $MoS_2$ . And our previous work shows Ag forms smooth and solid film on  $MoS_2$  which makes the carrier transport efficiently across the contacts. Our devices show good n-type current-voltage (I-V) characteristics. Then gate assisted Kelvin structure and 4-probe method was used to analyze the contacts. The contact resistance extracted from the both methods is significantly different due to the difference in position where the voltage is sampled in each method. By comparing the contact resistance extracted from two methods, we found the current transfer length ( $L_T$ ) of Ag-contact  $MoS_2$  transistors is from 137 nm to 206 nm

(increased with the increasing gate voltage). The channel sheet resistance is measured by 4-probe method. It is much larger than the contact resistance which indicates that the MoS<sub>2</sub> transistors are channel dominant. The contact resistivity is then extracted from our data. It can be effectively tuned by the gate as well. Our result indicates that the gate affects the current crowding in the contacts, so as the contact resistivity.

#### 1.3 Overview of Dissertation

In this dissertation, I will first present my work on the characterization of metal contacts on SiNW field effect transistors (FETs). In this work, metal contacts on SiNW FETs were studied with a gate assisted Kelvin structure. The SiNW devices were fabricated from chemical vapor deposited (CVD) SiNWs with conventional lithographic approaches. Al was used to form source/drain (S/D) contacts to SiNW transistors. The transistors exhibit ambipolar characteristics. The application of gate assisted Kelvin structure enabled the measurement of the contact characteristics of both electron- and hole-flow at the same contact. In this work, we found that the contact performance is affected by the carrier type that transport in the channel and also by the current transport direction. Also, based on the ambipolar characteristics of the transistors, an inverter was fabricated on a single SiNW.

Then, I will present an analysis of metal contacts on MoS<sub>2</sub>, which is a 2D semiconductor. This work is divided into two parts. In the first part of this work, Ag and Ti contacts on exfoliated MoS<sub>2</sub> films are compared. Based on the current-voltage (I-V) measurement, surface morphology and Raman spectroscope, I found interface

morphology plays an important role on the contact performance in MoS<sub>2</sub> FETs. In the second part of this work, gated assisted contact measurement was carried out on CVD MoS<sub>2</sub> transistors. The contact resistance and current crowding were measured and analyzed under different gate bias. Our results show that the gate voltage influences both contact resistivity and transfer length of the contacts. This indicates that contact resistance changes with gate voltage. This work also indicates that in our MoS<sub>2</sub>, the contacts play an important role in device performance. All these findings contribute to understanding the metal contact mechanism on MoS<sub>2</sub> as well as the MoS<sub>2</sub> transistor performance.

Finally, a brief summary of my work on the metal contacts is drawn and future plan of this work is laid out. It should be pointed out that although SiNWs and MoS<sub>2</sub> are good examples for low-dimensional materials, the gate assisted contact measurement can be applied on other emerging low-dimensional materials. The contact characterization metrology discussed in this thesis is very useful to many other applications such as in light emitting diode (LED) and photovoltaic devices where contacts are important.

# CHAPTER 2: CONTACT CHARACTERIZATION ON AMBIPOLAR SINW FETS BASED ON GATE-ASSISTED KELVIN STRUCTURE

#### 2.1 Introduction

In this work, a gate assisted Kelvin test structure based on Si nanowire field effect transistors has been designed and fabricated for the characterization of the transistor source/drain contacts. Because the Si nanowire field effect transistors exhibit ambipolar characteristics with electron current slightly lower than the hole current, we can select the type of carriers (electrons or holes) flowing through the same contacts and adjust the current by the applied gate voltage. With this method, we are able to measure the characteristics of the same contact with either pure electron or hole flow. In addition, we found that the nanowire contacts behave very differently depending on the current flow directions. This indicates that the source and drain contact resistance can be dramatically different. Such a gate assisted Kelvin Test structure will lead to future metrology and applications in nanoelectronics.

Then, an inverter based on ambipolar Si nanowire FETs was integrated on to a single SiNW. The inverter is consisted of two identical nanowire FETs on a single Si nanowire. The engaged FETs showed asymmetric ambipolar characteristics under positive and negative gate bias. A CMOS-like inverter can be realized on the single

nanowire, where one of the devices behaves as an nMOSFET and the other behaves as a pMOSFET.

# 2.2 Contact Resistance Dependence on Electron Transport Direction in Ambipolar SiNW FET

In this work, a gate assisted Kelvin test structure based on Si nanowire (SiNW) FETs has been designed and fabricated to study the properties of nanoscale S/D contacts. Although a Kelvin test structure based on planar MOSFETs has been previously reported,[75] the three-dimensional nanoscale contact presents an exciting challenge. With this SiNW FET based Kelvin test structure, we can select and measure the contact resistance (R<sub>C</sub>) of a single contact. We can also investigate the contact characteristics for pure electron or hole flow, and study the effect of carrier flow direction influencing on the contact behavior. We selected Si nanowires as a test platform, but the metrology can be applied to other nanoscale devices, such as nanotube FETs and FinFETs.

#### 2.2.1 Device Structure and Fabrication

The fabrication process can be summarized in Fig. 2.1.

Figure 2.1 Fabrication process of SiNW transistors.

For the device reported here, the SiNWs were grown from Au catalyst by low pressure chemical vapor deposition (LPCVD) with SiH<sub>4</sub> as precursor. The SiNWs were grown at  $450 \, ^{\circ}$ C for 2 hours with SiH<sub>4</sub> partial pressure of 500 mTorr. The resulting nanowires are in <111> orientation with an average diameter of the nanowires is 50 nm.

Then, the nanowires were harvested into methanol and dispersed on a Si substrate with 300 nm thermal SiO<sub>2</sub>. The nanowires were oxidized at 750 °C to grow  $\approx$  2nm SiO<sub>2</sub>, followed by e-beam lithography and metal formation. The S/D contact metal is Al of 1 µm width and 50 nm thickness. The gate/dielectric stack consists of 100 nm Pd on 20 nm HfO<sub>2</sub>, deposited by atomic layer deposition (ALD) at 300 °C. The samples were then annealed at 200 °C in forming gas for 2 minutes to improve the interface and metal

contacts. In the test structure, there are three identical contacts on a single SiNW, separated by two short channels (50 nm long) sharing a common gate.

Figure 2.2 Device structure and measurement set-up. (a) Schematic of device structure and measurement set-up. (b) Scanning electron microscopic image of the SiNW gate assisted Kelvin test structure. Yellow circle shows the SiNW FET (channel length: 50 nm). The inset in (b) shows the magnified image of the yellow circled region. Scale bars in (b) and inset are 1  $\mu$ m and 100 nm long, respectively.

As shown in Fig. 2.2, the gated Kelvin test structure consists of two SiNW FETs, sharing a common source, on a single nanowire. The resulting device scanning electron

microscopic (SEM) images and test setup is shown in Fig. 2.2. Even after the gate dielectric and contact formation, the position of the SiNW is still clear.

Figure 2.3 Scheme of the cross section off the SiNW under S/D contacts.

However, the dimension, especially diameter of the nanowire is obscured by the top layers. The width of the brighter pattern (202 nm in width) measured under SEM should be larger than the real diameter of the nanowire. As illustrated in Fig. 2.3(a), the measured width (W) is the width of the protrude region where the Si nanowire is covered by layers of Al, HfO<sub>2</sub> and Pd, totally 170 nm ( $\approx$  50nm Al + 20nm HfO<sub>2</sub> + 100nm Pd). The width (W) in SiNW SEM image is not the SiNW diameter. The radius (r) can be

calculated following the schematic shown in Fig. 2.3(b), where t is the total thickness of the covering layers (170 nm).

The correlation between W and the radius of the Si nanowire can be estimated as:

$$\left(\frac{w}{2}\right)^2 + (t-r)^2 = (t+r)^2,$$

(1.1)

$$r = W^2 / 16t. (1.2)$$

Therefore, the radius (r) and diameter of the Si nanowire are 15 nm and 30 nm, respectively. We drew this schematic of the cross section based on the cross section transmission electron microscopy (TEM) image of our previous devices. [76] The value of estimated diameter is quite consistent with our previous experiment where we used the same conditions to grow Si nanowires. [76]

#### 2.2.2 Results and Discussion

The non-local voltage,  $V_{23}$  (Fig. 2.1) between the middle (2, the source: S) and one of the side contacts (3) is measured while a current ( $I_{DS}$ ) is forced between the middle (2) and the other side contact (1, the drain: D), and thus the resistance of the middle contact is given by  $R_C = V_{23}/I_{DS}$ .

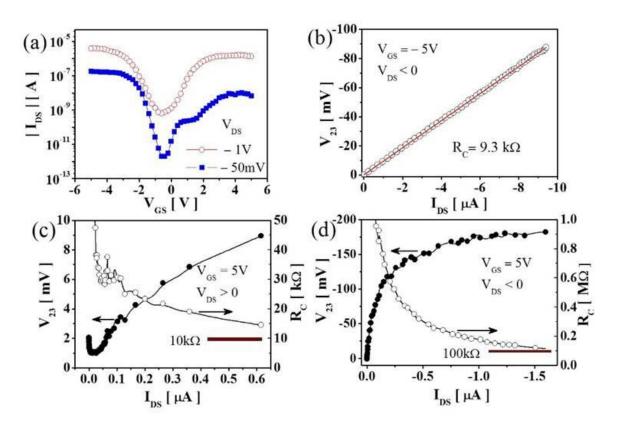

Fig. 2.4 shows the electrical measurements obtained with the above gate assisted Kelvin test structure. Fig. 2.4 (a) shows the drain current ( $I_{DS}$ ) vs. gate voltage ( $V_{GS}$ ) of the SiNW FETs at two source-to-drain voltage ( $V_{DS}$ ) values. The SiNW FETs exhibit short-channel FET behavior with ambipolar characteristics. The electron current (positive  $V_{GS}$ ) is lower than the hole current (negative  $V_{GS}$ ). We did not intentionally dope the

SiNWs, therefore, the ambipolar behavior arises from the S/D contact properties. We believe the SiNW surface at the S/D contacts was doped p-type by Al diffusion during ALD of gate dielectric and these S/D junctions favor hole over electron flow (just one dopant atom in such a small nanowire body would be significant). [77]

Figure 2. 4 Electric characterization: (a) Ambipolar  $I_{DS}$  vs.  $V_{GS}$  characteristics. (b) Hole contact characteristics selected by negative  $V_{GS}$ . Electron contact characteristics selected by positive  $V_{GS}$ : (c) electrons flow from Al to the SiNW channel; (d) electrons flow from the SiNW channel to Al.

To verify this, the electrical characteristics of the contacts are measured with the help of the gate assisted Kelvin test structure. Fig. 2.4(b) shows  $V_{23}$  versus  $I_{DS}$  at  $V_{GS} = -5.0$

V (hole current) is linear, indicating the contact is Ohmic. The slope of the line shows R<sub>C</sub>  $\approx 9.3 \text{ k}\Omega$ . For a Si nanowire of 30 nm in diameter and the contact of 1  $\mu$ m in length, the specific contact resistivity for holes is thus  $\rho_C \approx 8.8 \times 10^{-6}~\Omega$ •cm². This specific contact resistivity is estimated by  $\rho_C = R_C A$ , where A is the contact area. (A is estimated to be  $\pi$ Dl, where D is the diameter of the nanowire and 1 is the length of the contact.) [78] Fig. 2.4 also shows the contact resistance R<sub>C</sub> for electron conduction from the SiNW to Al (Fig. 2.4(c)) and from Al to the SiNW (Fig. 2.4(d)), respectively. As expected for this contact, the resistance for electron flow (e-flow) is larger than that for hole flow (h-flow) and exhibits diode-like current-voltage behavior. It is interesting to see that R<sub>C</sub> depends on the e-flow direction. The R<sub>C</sub> value for e-flow from Al to SiNW decreases with increasing I<sub>DS</sub> and approaches the hole R<sub>C</sub> at large I<sub>DS</sub>. But the R<sub>C</sub> value for e-flow from SiNW to Al is >10 times larger than the hole contact resistance. Such difference due to carrier flow direction is not seen in the h-flow contact resistance in these devices. The value of contact resistance and contact resistivity extracted by this gate assisted Kelvin structure can be much smaller than the value extracted by TLM method. [79] However, the distinct behavior of the contact responding to h- and e-flow is clearly seen. Especially for e-flow, the contact characteristics exhibit a diode-like pattern. The contact behaves significantly different depending on different carrier transport direction. It should be noted that the R<sub>C</sub> dependence on e-flow direction indicates the asymmetry in source and drain contacts. The contact we tested is source contact for the e-flow from Al to SiNW, while it is drain contact for the e-flow from SiNW to Al. According to our I<sub>DS</sub>-V<sub>GS</sub> characteristics, under a sufficient drain voltage  $|V_{DS}| = 1$  V, for the e-flow, the voltage

drop is  $\approx 2\%$  or  $\approx 30\%$  on this contact when it acts as source or drain contact respectively. Hence, from our results,  $R_C$  of drain contact is much higher (> 10 times) than that of source even if both contacts have identical physical characteristics. The conventional contact resistance characterization methods, such as TLM and 4-point measurement, cannot separate electron and hole flows or tell the difference between carrier flow directions.

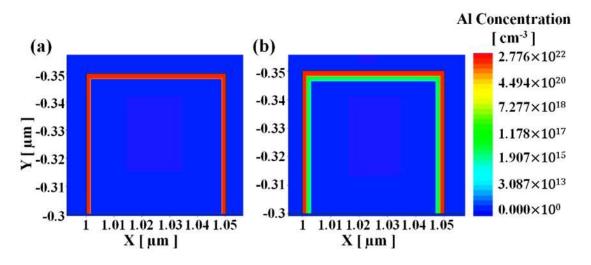

The different contact behavior between h-flow and e-flow can be understood by the effects introduced by Al diffusion in Si. SiNW under the contact was doped into p-type because of the Al diffusion during the fabrication process. So that an Ohmic contact is expected for h-flow and a diode-like performance expected for the e-flow. To evaluate Al diffusion, we simulated Al diffusion in Si by using TCAD Sentaurus. Fig. 2.5 compares the Al concentration in the device before and after annealing. We generate a square Si nanowire with a high concentration of Al on the surface (Fig. 2.5(a)). The diameter of the Si nanowire is 50 nm. Our result shows after annealing the nanowire at 300  $^{\circ}$ C in  $O_2$  ambient for 30 minutes sufficient Al diffused from surface into the Si (Fig. 2.5(b)). Like boron diffusion,  $O_2$  enhancement of the Al diffusion is essential for the diffusion to happen at this low temperature. [80, 81] As  $O_2$  plasma instead of  $H_2O$  was used as oxidant in ALD, it is reasonable to believe Al diffusion happened in our SiNW FET S/D contact.

Figure 2. 5 Diffusion of Al in silicon: (a) Al concentration before annealing at 300°C for 30 minutes in O<sub>2</sub>. (b) Al concentration after annealing at 300°C for 30 minutes in O<sub>2</sub>.

Based on the doping concentration obtained from the diffusion simulation, the SiNW band diagram on the source contact adjacent under various bias conditions is generated by Sentaurus (see Fig. 2.6). The band bending is effectively tuned by  $V_{GS}$ . At negative  $V_{GS}$ , holes transport through the channel. It is clear an Ohmic contact is formed between channel and the source (Fig. 2.6(b)). At positive  $V_{GS} = 5.0$  V, when  $V_{DS} = 1$  V, electrons flow from Al contact to the SiNW channel (Fig. 2.6(c)), and vice versa for  $V_{DS} = -1$ V (Fig. 4d). The electrons going down the hill (Fig. 2.6(c)) will experience less resistance than the electrons climbing up the barrier hill to reach the Al contact (Fig. 2.6(d)). We believe that the  $R_C$  for electrons flow from Al to SiNW at large  $I_{DS}$  and the hole  $R_C$  represents the net contact resistance excluding the effect of junction below the contact. This result proves that the gate assisted Kelvin test structure based on nanoscale FETs can measure not only the  $R_C$  of high resistance materials, but also the net  $R_C$  for both

Ohmic and diode-like contacts because it can separate and select the electron and hole flow.

Figure 2.6 Band diagram from channel center to the contact at different conditions: (a) Equilibrium state. (b)  $V_{DS} < 0$  and  $V_{DS} < 0$ : hole flow from Al to SiNW. (c)  $V_{GS} > 0$  and  $V_{DS} > 0$ : electrons flow from Al to SiNW (d)  $V_{GS} > 0$  and  $V_{DS} < 0$ : electrons flow from SiNW to Al.

#### 2.2.3 Conclusion

In summary, we have designed and fabricated the gate assisted Kelvin test structure based on SiNW FETs. This test structure can efficiently detect the properties of electron and hole flows at the same nanoscale contacts. It has been found that the electron and hole flow resistances are very different; and the non-Ohmic contact resistance has a strong dependence on current direction. Also, the asymmetry between the source and drain contacts in a nanoscale FET can be determined by the gate assisted structure. Such an interesting gate assisted Kelvin test structure will lead to expand characterization metrology and may have important applications in nanoelectronics.

# 2.3 Inverter on a Single SiNW

As the scaling of Complementary Metal-Oxide-Semiconductor Field Effect Transistor (CMOS FET) continues, the challenge of short-channel effects (SCE) and exponentially increasing cost has almost become an impossible task for conventional bulk-Si based CMOS technology. [82] Several novel channel materials such as III-V compounds and graphene, and device structures including multi-gate and FinFETs were investigated to achieve better device performance like extended high frequency respond or lower subthreshold slope. Among these candidates, Si nanowire (SiNW) is the most attractive channel materials for future CMOS FET due to its intrinsic semiconductor properties, small dimension and fully CMOS compatibility. We have been engaged in the research of bottom-up Si nanowire FETs with gate-all-around (GAA) structure for high performance.

channel even when channel length down to below 10 nm. [82] The SiNW based electronics built on a bottom-up self-assembly will have the advantage of low cost and high density.

However, the difficulties in controlling the doping level of SiNW make it too complicated to make traditional FETs with n-p-n or p-n-p doping structure. [2, 3] SiNWs with Schottky contacts (also indicated as Schottky barrier FETs) were demonstrated that they can work as enhancement-mode FETs. [43] In this case, the drain current level depends on the contact metal work function. The different conduction mechanisms for accumulation- and inversion-mode operation make it possible to make FETs with ideal ambipolar characteristics, so that an inverter can be integrated onto just one single nanowire with two identical MOSFETs one of which works as pMOS and the other as nMOS. In this work, we have designed a single-nanowire CMOS inverter based on ambipolar SiNW FETs with 50 nm channel length which we used in gate assisted Kelvin contact characterization.

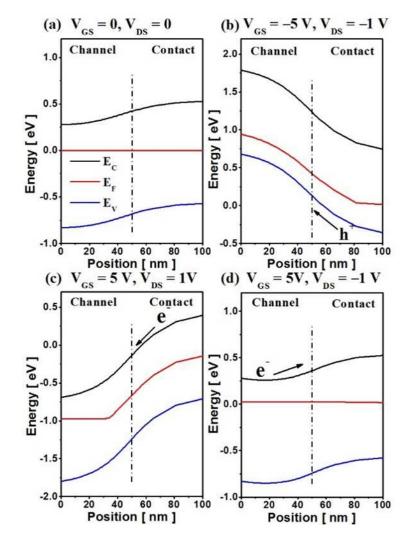

Figure 2. 7 SEM image and measure set-up of the inverter

The fabrication process and device structure are the same as previous SiNW FETs we used in contact characterization. The measurement set-up is illustrated in SEM image Fig. 2.7. The ambipolar I-V characteristics of the transistors inspired the possibility of fabricating CMOS logic gates using these SiNW FETs. A CMOS inverter based on two identical ambipolar SiNW FETs with 50-nm channel length built on one single nanowire (see Fig. 2.4). We measured the device with voltage supply (V<sub>DD</sub>) of 2 V, and swept the input voltage from 0 to 4V (Fig. 2.8). The voltage transfer curve is slightly asymmetry in

this input range, but has small noise margin. The transfer happens mostly from 1V to 3V. So if we bias the input voltage to around 2V, we can get a symmetric output in a 2V input range from (2-1) V to (2+1) V.

Figure 2.8 Voltage transfer characteristics of single nanowire CMOS inverter under  $V_{DD}$  = 2 V and  $V_{IN}$  = 0~4 V.

The inverter works properly with slightly asymmetric behaviors and a small noise margin in voltage transfer. These issues can be resolved by engineering the threshold voltages and decreasing off-state current. In addition, the inverter has a very simple and yet very efficient structure. Various logic gates based on ambipolar SiNW FETs can be fabricated in two lithographic steps. Due to the scalability of nanowires and the

advantage of bottom-up process, this approach can lead to low-cost, high-density nanoelectronics circuitry.

## CHAPTER 3: ROLE OF INTERFACE MORPHOLOGY ON METAL CONTACTS TO MoS<sub>2</sub>

#### 3.1 Introduction

Recently, MoS<sub>2</sub> has attracted a lot of attention for electronic and optoelectronic applications. [10, 11, 50-52] Layered MoS<sub>2</sub> is a 2-dimensional (2D) semiconductor which has a bandgap ranging from 1.2 eV to 1.8 eV depending on its thickness. [14, 15, 27] In particular, monolayer MoS<sub>2</sub> with a direct bandgap of 1.8 eV shows promising applications in optoelectronics. [27, 53, 54] 2D MoS<sub>2</sub> is also attractive for flexible electronic applications because of its intrinsic ultrathin body, and robust lattice structure.[19, 20, 55] Considering short channel effects in metal-oxide-semiconductor field effect transistors (MOSFETs), this intrinsic ultrathin body also represents the ultimate in scaling. [56] Moreover, its inert surface has no dangling bonds, which is advantageous for forming the channel-gate dielectric interface in MOSFETs. Monolayer MoS<sub>2</sub> MOSFET was the first demonstrated 2D TMD semiconductor MOSFET. [9] Such transistors have exhibited a high ON/OFF ratio of 10<sup>8</sup> and decent subthreshold slopes of 74 mV/dec which is compatible with current state of art CMOS technology.

Various work has been done to understand the transport mechanism in  $MoS_2$  transistors and to improve their performance for future applications. [57-61] The Source/Drain (S/D) contacts are very important factors for device performance. A variety

of contacts have been used and studied to achieve a good Ohmic contact on MoS<sub>2</sub>. [37, 38, 55, 62-64] It was originally expected that a low work function metal may lead to a lower Schottky barrier for electron transport and result in a good n-type contact. [37] However, the experimental results from S. Das et al. show that the barrier height between the MoS<sub>2</sub> channel and the metal contact is only weakly influenced by the metal work function and that an n-type barrier even forms between MoS<sub>2</sub> and high-work function metal such as Pt. [37] The theoretical work by C. Gong et al. confirms that partial Fermi level pinning in metal-MoS<sub>2</sub> contacts makes the Fermi levels in all studied metal-MoS<sub>2</sub> complexes except Pt are situated above the midgap of MoS<sub>2</sub>. [38] Additionally, S. McDonnell et al. demonstrate that intrinsic defects in MoS<sub>2</sub> dominate the metal-MoS<sub>2</sub> contact resistance and provide a low Schottky barrier independent of metal contact work function. [62] All these complications show that metal work function is not a good indicator for forming an Ohmic contact with MoS<sub>2</sub>.

Previous studies on metal contacts to graphene or carbon nanotube demonstrate that the morphology of metal contacts and the interaction between these carbon materials and metal contacts play important roles in contact resistance. [64, 65] Although it is well believed that metal wettability plays an important role in metal-MoS<sub>2</sub> contacts, [37] to our best knowledge, there is no work showing the direct evidence on how the metal contact morphology affects the metal-MoS<sub>2</sub> contacts. In this work, for the first time, we have shown how the metal-MoS<sub>2</sub> interface influences the MoS<sub>2</sub> FET performance.

Ag was chosen because it has been reported to form a good contact on WSe<sub>2</sub>, [66] which is a similar material to MoS<sub>2</sub>. Previous work also shows that Ag has excellent

wettability on bulk MoS<sub>2</sub>. [67] We compare the results from Ag contacts with those from Ti contacts, which are commonly-used metal contacts with MoS<sub>2</sub> in the literature. [9, 37, 54, 68-71] Our results show that, despite of the similar work function around 4.3 eV for both metals, [72] mono- and few-layer MoS<sub>2</sub> transistors with Ag contacts show significantly better electrical characteristics with more than 60-time higher ON-state current density and steeper subthreshold slopes.

The surface morphology of the metal films was then investigated by depositing 5 nm thin layer of contact metal (Ag or Ti) capped with a 5 nm Au protection layer on top of MoS<sub>2</sub>. Scanning electron microscopy (SEM) shows that smoother and denser Au/Ag film is formed on top of MoS<sub>2</sub>. The surface roughness analysis was carried out by atomic force microscopy (AFM). The metal-MoS<sub>2</sub> interface was then investigated by Raman spectroscopy and the Raman spectra reveal that the contacting interface is between MoS<sub>2</sub> and Ag or Ti. The better wettability between Ag and MoS<sub>2</sub> is essential to form smoother and denser Au/Ag contacts on MoS<sub>2</sub>, resulting in a better device performance. The strain effect introduced by Ag and heating effect introduced by Ti to monolayer MoS<sub>2</sub> are also revealed by the Raman spectroscopy.

## 3.2 Experimental Methods

#### 3.2.1 Sample Preparation:

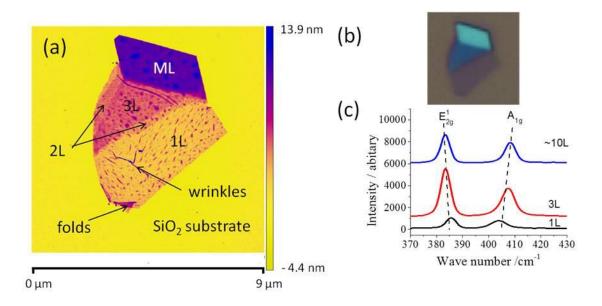

The sample preparation starts with exfoliating bulk  $MoS_2$  (SPI<sup>®</sup> small crystals) into mono- and few-layer films on  $280 \text{nm SiO}_2$  / Si. The  $MoS_2$  film thickness was confirmed by the color, Raman spectroscopy and AFM. (Figure 3.1) As seen in Figure

3.1(c), the distance between the two characteristic Raman peaks increases as the thickness of MoS<sub>2</sub> increases. This trend has been published repeatedly and widely accepted as a method the determine MoS<sub>2</sub> film thickness when it is only a few layers thick.[84] This thickness is also compared to AFM results to set a reference to identify MoS<sub>2</sub> thickness.

Figure 3.1  $MoS_2$  flake on  $SiO_2/Si$  substrate. (a) AFM image of a  $MoS_2$  flake which includes monolayer, trilayer and multiple layer regions. (b) Optical image of the same flake. (c) Raman spectra of different thickness  $MoS_2$  which is collected from the different positions on the same flake of  $MoS_2$ .

Then the back-gated mono- and few-layer  $MoS_2$  transistors were fabricated for electric measurement. The detailed fabrication process is as following.

1. The MoS<sub>2</sub> flake positions are identified with pre-designed alignment marks by an optical microscope.

- 2. Pattern the source/drain contacts with electron-beam lithography. 495 PMMA A4 resist was used as resist. The resist was coated by spinning it onto the substrate at rotation speed of 3000 rpm for 45 sec. Then the substrate was heated on a hot plate at 180 °C for 2 min. The accelerate voltage of the e-beam was 20 kV in the e-beam lithography system. And the exposure dose was 160 µAs/cm².

- 30. Metal deposition to form S/D contacts by e-beam evaporation. We deposited 30 nm Au / 30 nm Ag (contact layer) for Ag contacted MoS<sub>2</sub> FETs and 30nm Au / 30nm Ti for Ti contacted ones as the contact metals. The system pressure was kept at  $\approx 1 \times 10^{-6} \text{Torr}$  during the metal deposition. The first 5nm of metal which directly contacted to MoS<sub>2</sub> was deposited at a lower rate of  $\approx 0.2 \text{Å}$  / sec to improve the interface roughness, and rest of metal was deposited at a higher rate of  $\approx 1 \text{Å}$  / sec.

- 4. Lift off the metal by soak the sample into acetone over night at room temperature. The sample was rinsed with IPA and DI water after the acetone bath. The resulting devices have a channel length of 1  $\mu$ m and contact width of 1  $\mu$ m as well.

We also prepared samples for the interface characteristics. To do so much thinner metal film was e-beam evaporated on to exfoliated  $MoS_2$ . Samples for SEM, AFM and Raman spectroscopy are prepared in the same way except no e-beam lithography and lift off step and the thickness of metal deposited is thinner. 5nm Au / 5nm Ag and 5nm Au / 5nm Ti was deposited by e-beam evaporation. The top 5 nm Au is used as a capping layer

which protects the bottom contact layer from oxidizing. The e-beam evaporation conditions used are the same with device fabrication except that the deposition rate was kept at  $\approx 0.2 \text{Å}$  / sec for the whole metal deposition process to mimic the device fabrication.

#### 3.2.2 Characterizations:

The electric properties of  $MoS_2$  FETs were tested in a vacuum probe-station. The system was kept at  $\approx 1 \times 10^{-6}$  Torr during the measurement. A semiconductor parameter analyzer (HP 4156C) was used to carry out the electric measurement. The SEM is done with Zeiss Ultra-60 Field Emission SEM. An accelerate voltage of 5kV was used to capture the images. AFM images are taken with Dimension system controlled by Nanoscope V (Bruker, Santa Barbara, CA). All AFM experiments are performed with SCANANASYST-AIR tip (Bruker, Santa Barbara, CA) with a radius of 10nm. AFM data are analyzed with WSxM software.[85] Raman spectra were acquired under ambient conditions with a micro-Raman spectrometer (Renishaw InVia Raman system) equipped with a 514.5nm (2.41 eV) wavelength excitation laser and an 1800 lines/mm grating while operating in 180 °backscattering geometry. A 50X objective was used to focus the excitation laser to an approximately  $1\mu m$  spot onto the sample. The 100% laser power is 4.8mW. We typically used 50% power to collect the signal for 1 second to compare the Raman spectra before and after metal deposition.

#### 3.3 Results and Discussion

#### 3.3.1 Electrical Characterization of MoS<sub>2</sub> transistors

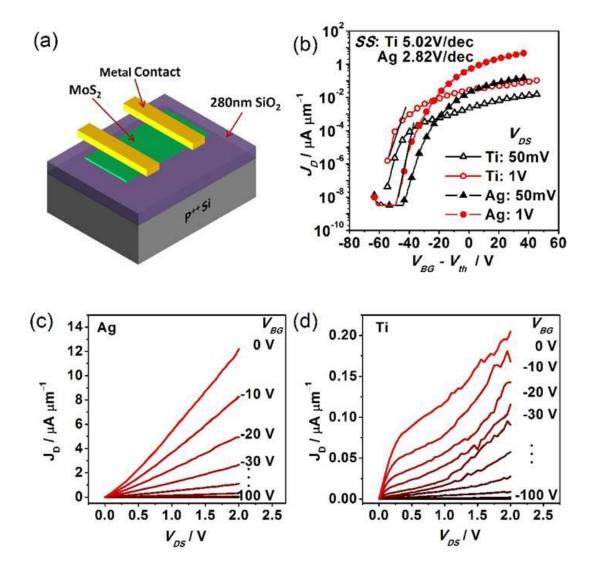

Our devices were fabricated with exfoliated  $MoS_2$  on 280 nm  $SiO_2/Si$  substrate. We deposited 30 nm Au/30 nm Ag for Ag contacted  $MoS_2$  FETs and 30 nm Au/30 nm Ti for Ti contacted ones by e-beam evaporation. The resulting devices have a channel length of 1 $\mu$ m and a contact width of 1 $\mu$ m as well (**Figure 3.2**(a)).

Figure 3.2(b-d) shows the electric characteristics of monolayer  $MoS_2$  transistors. We normalized the drain current (I<sub>D</sub>) to the current density per 1 µm channel width (J<sub>D</sub>) to compare the electrical characteristics of transistors with different channel width. Figure 3.2(b) compares the characteristics of  $J_D$  versus back gate voltage ( $V_{BG}$ ) ( $J_{D}$ - $V_{BG}$ characteristics) in monolayer MoS<sub>2</sub> transistors with Ag and Ti contacts. The devices were tested with V<sub>BG</sub> varying from -100 V to 0 V and drain to source voltage (V<sub>DS</sub>) equals to 50 mV or 1 V. All our devices show n-type MOSFET behaviours. The threshold voltage of the devices was extracted from the linear fitting of the ON-current versus V<sub>BG</sub> with  $V_{DS} = 50$  mV. The device threshold voltages are equal to -36.6 V and -45.4 V for Ag and Ti contacts, respectively. These results are reasonable since Ag and Ti have similar work functions. The devices with Ti contacts show a typical ON-current density, which is comparable to other back gated MoS<sub>2</sub> transistors without high-k dielectric passivation. [68-70] Most importantly, the devices with Ag contacts exhibit almost two orders of magnitude larger on-state current density than those with Ti contacts. We extracted subthreshold slope (SS) of the devices, which is given by:

$$SS = \frac{dV_{BG}}{d(\lg(I_D))}\Big|_{V_{DS}} \tag{1}$$

Figure 3. 2 MoS<sub>2</sub> transistor diagram and Drain current density of single-layer MoS<sub>2</sub> transistors: (a) MoS<sub>2</sub> transistor diagram Drain current density of single-layer MoS<sub>2</sub> transistors versus (b)  $V_G$ - $V_{th}$  with Ag or Ti contacts, and (c, d) drain voltage ( $V_{DS}$ ) with (c) Ag or (d) Ti contacts.

SS was extracted from  $J_D$ - $V_{BG}$  characterization at  $V_{DS} = 1$  V. For devices with Ag contacts, the SS is 2.82 V/dec, and with Ti contacts, it is 5.02 V/dec. The large SS is partially due to the large thickness (280 nm) of back gate oxide. Similar SS value was also reported in the back-gated  $MoS_2$  FETs in previous publications. [68, 70] The lower SS of devices with Ag contacts indicates the improved contact quality. It is clear that the device performance is significantly affected by the contacts. Better contacts bring about better electrostatics so that devices with Ag contacts show a lower subthreshold slope.

Figure 3.2(c) and (d) compare  $J_D$ - $V_{DS}$  (source-drain voltage) characteristics of monolayer  $MoS_2$  FETs with Ag and Ti contacts, respectively. The drain current was measured with  $V_{DS}$  varying from 0 to 2 V with  $V_{BG}$  varying from 0 to -100 V with a -10 V step. In Figure 3.2(c), the super-linear relationship between ON-state  $J_D$  and  $V_{DS}$  near zero in monolayer  $MoS_2$  FETs with Ag contacts indicates the Schottky barrier transistor behaviour. In figure 3.2(d), the ON-state current density of  $MoS_2$  FETs with Ti contacts is consistent with previous publications, [68, 70] and significantly smaller than the ones with Ag contacts. The linear dependence of  $J_D$  on  $V_{DS}$  could be a result of thermally assisted tunnelling, and may not necessarily indicate an Ohmic contact. [37] The current density of monolayer  $MoS_2$  FET with Ag contacts is 60 times larger at  $V_{BG} = 0$  V and  $V_{DS} = 2$  V than that with Ti contacts. This larger magnitude of ON-current density reflects the higher carrier injection efficiency.

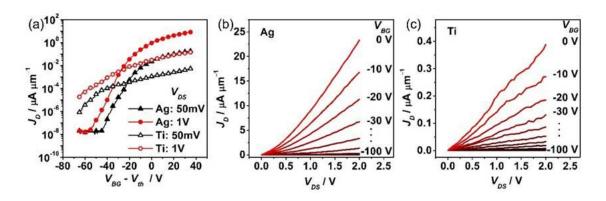

**Figure 3.3** shows electrical properties of few-layer (2 to 3 layers)  $MoS_2$  FETs. The drain current in these few-layer  $MoS_2$  FETs was measured under the same bias conditions as the monolayer devices. In Figure 3.3(a),  $J_D$ - $V_{BG}$  characteristics of few-layer

MoS<sub>2</sub> FET with Ag and Ti contacts were compared. All the devices show n-type MOSFET behaviour. The threshold voltage is -35.0 V for devices with Ag and Ti contacts. The subthreshold slope of transistors with Ag contacts is 5.42 V/dec. The devices with Ti contacts also show typical performance reported in previous publications. [68-70] The few-layer MoS<sub>2</sub> transistors with Ti contacts cannot be turned off completely even at  $V_{BG} = -100$  V. Therefore, the subthreshold slope cannot be precisely extracted. Nonetheless, the comparison between these two devices does show improved current density and subthreshold slope with the Ag contacts.

Figure 3.3 Drain current density of few-layer  $MoS_2$  transistors versus (a)  $V_G$ - $V_{th}$  with Ag or Ti contacts, and (b, c) drain voltage  $(V_D)$  with (b) Ag or (c) Ti contacts.

Figure 3.3(b) and (c) show  $J_D$ - $V_{DS}$  characteristics of few-layer  $MoS_2$  FETs with Ag and Ti contacts, respectively. Similar to monolayer  $MoS_2$  FETs, a 60-time ON-state current enhancement is also shown in few-layer  $MoS_2$  FETs with  $V_{BG} = 0$  V and  $V_{DS} = 2$  V.

As the contacting metal, Ag or Ti, is thick enough, the barrier height between MoS<sub>2</sub> and metal is dominated by the interaction between MoS<sub>2</sub> and the direct contact metal layer. Here, Ag and Ti have very similar work functions (4.26 eV for Ag and 4.33 eV for Ti). [72] Interestingly, theoretical simulations have shown that Ti is a better contact with WSe<sub>2</sub> than Ag, [66, 71] experimental results show that the devices with Ag contacts perform much better than those with Ti. [66] To gain a better understanding, we performed the surface and interface characterization on our metal contacts.

### 3.3.2 Surface Morphology of Metal Thin Films on MoS<sub>2</sub>

To understand the performance difference, we deposited 5 nm Ag or 5 nm Ti on top of exfoliated  $MoS_2$  followed by the deposition of 5 nm Au as protection layer. The conditions used are the same with device fabrication except that the deposition rate was kept at  $\approx 0.2$  Å/sec for the whole metal deposition process to mimic the device fabrication.

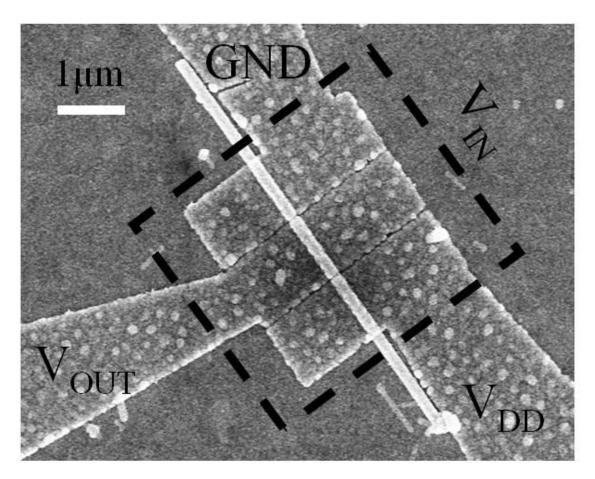

Then, SEM was carried out to characterize their surface morphology. From SEM images (**Figure 3.4**), the morphology of Au/Ag or Au/Ti films on MoS<sub>2</sub> is found to be significantly different. Figure 3.3(a) shows that the Au/Ag morphology on MoS<sub>2</sub> and on SiO<sub>2</sub>/Si substrate is so distinct that MoS<sub>2</sub> area can be clearly identified. Au/Ag forms surprisingly a much smoother and denser film on MoS<sub>2</sub> than on SiO<sub>2</sub>/Si. In contrast, with the appearance of pinholes, Au/Ti film shows quite similar morphology on both MoS<sub>2</sub> and SiO<sub>2</sub>/Si (Figure 3.4(b)). Therefore, the location of monolayer MoS<sub>2</sub> is very difficult to identify, though we can still identify it through its edges.

Figure 3.4 SEM images of  $MoS_2$  on  $SiO_2/Si$  substrate after (a) Au / Ag deposition and (b) Au/Ti deposition. The insets show corresponding optical image of pristine  $MoS_2$  before metal deposition. The locations of monolayer  $MoS_2$  (1L) and few-layer  $MoS_2$  (FL) are identified after metal deposition.

AFM was used to further analyze the surface roughness of the metal films. As seen in the AFM images (**Figure 3.5**), topography of the metals on MoS<sub>2</sub> and SiO<sub>2</sub>/Si substrate exhibits significant difference. Au/Ag on MoS<sub>2</sub> is smoother than on SiO<sub>2</sub>/Si (Figure 3.5(a)). A line profile shows that the surface of Au/Ag on monolayer MoS<sub>2</sub> is 0.54 nm lower than on SiO<sub>2</sub>/Si on average (Figure 3.5(b)). Since the same amount of metal is deposited on the surface, a smoother and denser metal film (Au/Ag) on MoS<sub>2</sub> results in a thinner film than that on SiO<sub>2</sub>/Si, even with the additional layer of MoS<sub>2</sub> underneath. The normalized height histograms of Au/Ag also show a narrower height distribution on MoS<sub>2</sub> than on SiO<sub>2</sub>/Si (Figure 3.5(c)). The root mean squared (RMS) surface roughness is 0.37 nm on MoS<sub>2</sub>, but 0.61 nm on SiO<sub>2</sub>/Si. For Au/Ti, however,

pinholes are clearly seen on both  $MoS_2$  and  $SiO_2/Si$  (Figure 3.5(d)). The surface of Au/Ti on  $MoS_2$  is 2.18 nm higher than that on  $SiO_2/Si$  (Figure 3.5(e)). This is reasonable by considering the height of  $MoS_2$  and its interfaces. The metal surface roughness is almost the same on  $MoS_2$  and on  $SiO_2/Si$  (Figure 3.5(f)): RMS roughness is 1.08 nm and 1.09 nm on  $MoS_2$  and on  $SiO_2/Si$ , respectively. Clearly, the Au/Ag film is much smoother than the Au/Ti film on  $MoS_2$ .

Figure 3.5 AFM and roughness analysis of metal on  $MoS_2$  and  $SiO_2/Si$  substrate: (a) Topography of Au/Ag on  $MoS_2$  and  $SiO_2/Si$ . (b) A topographic line profile of the height along the slide line indicated in figure (a). (c) Normalized histograms of height distribution of areas indicated by the square in figure (a). (d) Topography of Au/Ti on  $MoS_2$  and  $SiO_2/Si$ . (e) A topographic line profile of the height along the slide line indicated in figure (d). (f) Normalized histograms of height distribution of areas indicated by the square in figure (c). Scale bars are 500nm long for image (a) and (d).

#### 3.3.3 Raman Spectroscopy of MoS<sub>2</sub> Covered with Metal

Recently, Raman spectroscopy has been used to investigate the effects of metal-MoS<sub>2</sub> interface on the electronic and phonon properties of MoS<sub>2</sub>. [86] We carried out our Raman spectroscopy measurements on mono- and few-layer MoS<sub>2</sub> before and after deposition of the thin metal films (5 nm Au/5 nm Ag or 5 nm Au/5 nm Ti).

Figure 3.6 Comparison of Raman spectra before and after (a) Au/Ag or (b) Au/Ti deposition on monolayer (1L)  $MoS_2$  and before and after (c) Au/Ag or (d)Au/Ti deposition on few-layer (FL)  $MoS_2$ . The scatters are real data and solid lines are fitted Lorentz peaks.