## A METHODOLOGY FOR MAKING EARLY COMPARATIVE ARCHITECTURE PERFORMANCE EVALUATIONS

by

Gerald S. Doyle A Dissertation Submitted to the Graduate Faculty of George Mason University In Partial Fulfillment of The Requirements for the Degree **Doctor of Philosophy** Computer Science

#### Committee:

3 DEC 2010

Dr. Elizabeth White, Dissertation Director

Dr. Hassan Gomaa, Committee Member

Dr. Alex Levis, Committee Member

Dr. Robert Simon, Committee Member

Dr. Hassan Gomaa, Department Chair

Dr. Lloyd J. Griffiths, Dean, The Volgenau School of Information Technology and Engineering

Fall Semester 2010 George Mason University Fairfax, VA

# A Methodology for Making Early Comparative Architecture Performance Evaluations

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

Ву

Gerald S. Doyle

Masters of Science

George Mason University, 2000

Masters of Science

Naval Postgraduate School, 1979

Bachelor of Science

United States Military Academy, 1973

Director: Elizabeth White, Professor Department of Computer Science

> Fall Semester 2010 George Mason University Fairfax, VA

Copyright 2010 Gerald S. Doyle All Rights Reserved

## **DEDICATION**

I dedicate this dissertation to my family, friends, and co-workers who donated the gifts of time, patience and encouragement to advance this work to completion.

#### **ACKNOWLEDGEMENTS**

First and foremost I would like to express my gratitude to my family, friends and co-workers who provided me the time, flexibility and encouragement needed to complete this effort. The patience of Charlotte, Laura, Kim, Bruce and Bruce can not be overstated. I would like to thank Dr. Elizabeth White for her guidance in my study of architectures over the years as well as for her many suggested improvements to the manuscript. I express my appreciation to the committee for their diligent review of this work, and would further like to acknowledge the support of the broader GMU faculty in preparing me for this effort. In particular I would like to thank Dr. Sood for his insight into how to approach the dissertation, and Dr. Alexander Levis for broadening my engineering perspective on many difficult issues.

# **TABLE OF CONTENTS**

|       |                                                                 | age |

|-------|-----------------------------------------------------------------|-----|

|       | TABLES                                                          |     |

|       | FIGURES                                                         |     |

|       | ACT                                                             |     |

|       | oduction                                                        |     |

| 1.1   | Introduction                                                    |     |

| 1.2   | Systems Development Process                                     |     |

| 1.3   | Uncertainties Encountered in the Systems Development Process    |     |

| 1.4   | Performance Analysis to Date                                    |     |

| 1.5   | Architecture Performance Evaluation Options                     |     |

| 1.6   | Performance Analysis Improvement Strategy                       |     |

| 1.7   | Work Focus                                                      |     |

| 1.8   | Research Strategy                                               |     |

| 1.9   | Definitions                                                     |     |

| 1.10  | Research Approach                                               |     |

| 1.11  | Assumptions                                                     |     |

| 1.12  | Organization                                                    |     |

|       | ated Work                                                       | _   |

| 2.1   | Software Architecture Foundational Work                         |     |

| 2.2   | Architecture Description Languages                              |     |

| 2.3   | System Performance Evaluation                                   | 29  |

| 2.3.1 | Queuing Networks                                                |     |

| 2.3.2 | Petri Nets                                                      |     |

| 2.3.3 | Stochastic Process Algebras                                     |     |

| 2.3.4 | Simulation Models                                               |     |

| 2.3.5 | Combined Models                                                 |     |

| 2.3.6 | Component-based Architectures                                   |     |

| 2.3.7 | Architecture Design Domain Specific Considerations              |     |

| 2.4   | Other Domain Specific Concerns                                  |     |

| 2.5   | Identifying Good Attributes for a Performance Analysis Approach |     |

| 2.6   | Summary                                                         |     |

|       | nitecture Performance Viewed as a Specific Experiment           |     |

| 3.1   | Introduction                                                    |     |

| 3.2   | Early Performance Estimation Methodology                        |     |

| 3.3   | Defining an Experiment                                          | 47  |

| 3.4    | Performance Estimation Fundamentals                       | . 50 |

|--------|-----------------------------------------------------------|------|

| 3.5    | Identifying Uncertainty Sources                           | . 51 |

| 3.5.1  | Value or Data Based Performance Uncertainties             | . 51 |

| 3.5.2  | Algorithm-Based Performance Uncertainties                 | . 52 |

| 3.5.3  | Topology-Based Performance Uncertainties                  |      |

| 3.5.4  | Synchronization-Based Performance Uncertainties           | . 56 |

| 3.5.5  | Load-Based Performance Uncertainties                      |      |

| 3.5.6  | Sizing-Based Performance Uncertainties                    | . 57 |

| 3.6    | Summary                                                   | . 58 |

| 4 Con  | nparing Architecture Performance Potential                | . 60 |

| 4.1    | Introduction                                              |      |

| 4.2    | Deriving a Performance Probability Integral               | . 61 |

| 4.3    | Verifying the Probabilistic Analysis                      | . 68 |

| 4.4    | Example 1 - Comparing Two Normal Performance Descriptions | . 68 |

| 4.5    | Example 2 - Possibly Overlapping Performance Descriptions | . 73 |

| 4.6    | Example 3 - Comparing Discrete Performance Descriptions   | . 77 |

| 4.7    | Example 4 – Asymmetric Performance Descriptions           |      |

| 4.8    | Summary                                                   | . 81 |

| 5 Con  | structing Architecture Performance Descriptions           | . 82 |

| 5.1    | Introduction                                              |      |

| 5.2    | Summation                                                 | . 84 |

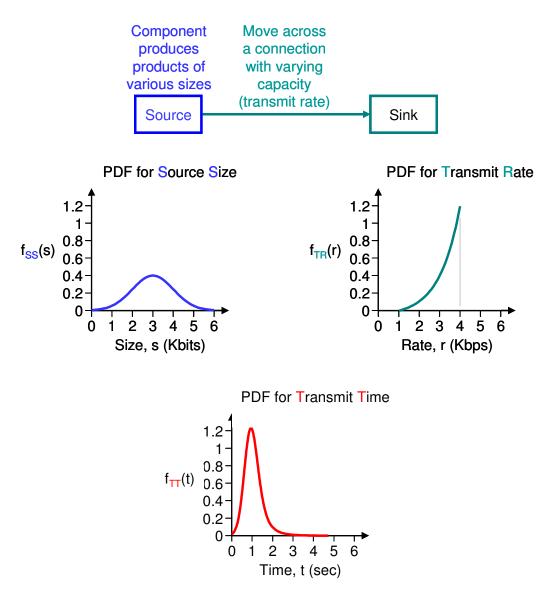

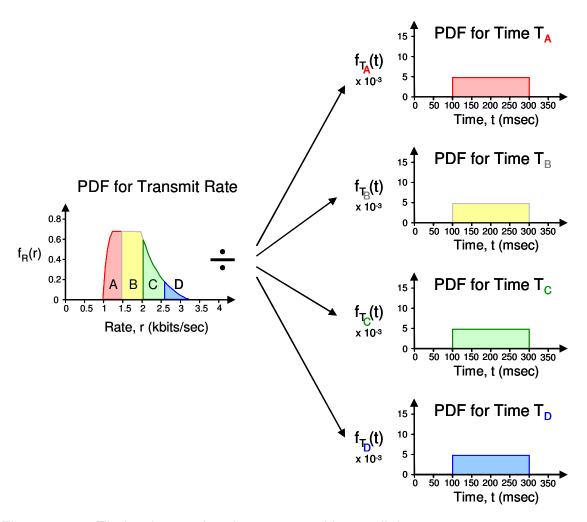

| 5.3    | Quotient                                                  | . 86 |

| 5.4    | MIN                                                       | . 89 |

| 5.5    | MAX                                                       | . 91 |

| 5.6    | Composite                                                 | . 95 |

| 5.7    | Summary                                                   | . 99 |

| 6 An I | Ilustrative Practical Architecture Example                | 101  |

| 6.1    | Introduction                                              | 101  |

| 6.1.1  | Selecting Specific Architectures for Demonstration        | 105  |

| 6.2    | Assigning Delay Descriptions to Architecture Elements     | 107  |

| 6.2.1  | Characterizing the Architectural Elements                 | 110  |

| 6.2.2  | Architecture A                                            | 111  |

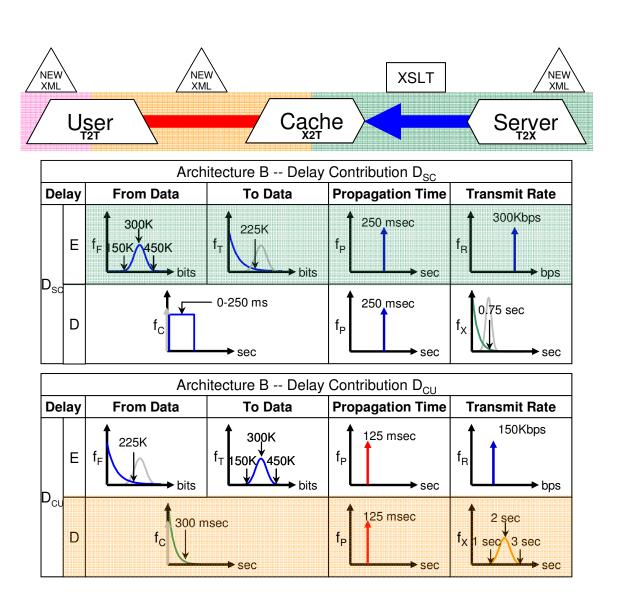

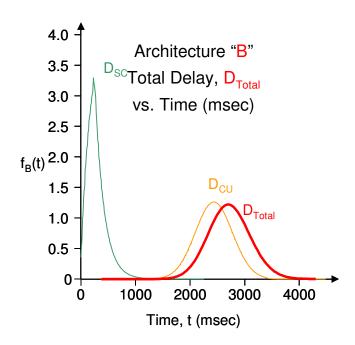

| 6.2.3  | Architecture B                                            | 115  |

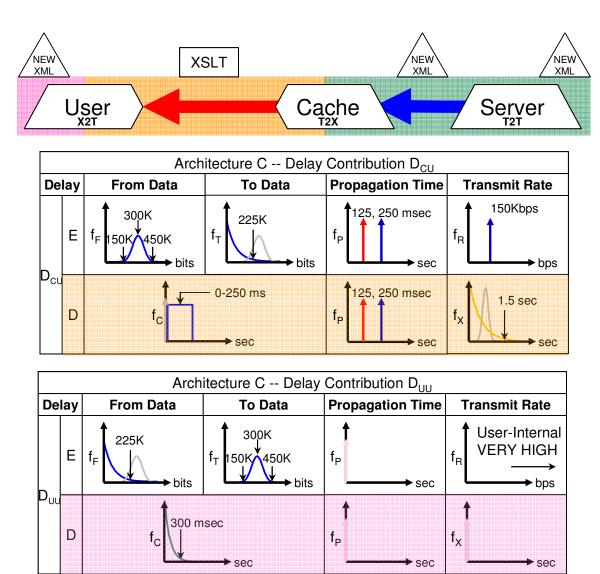

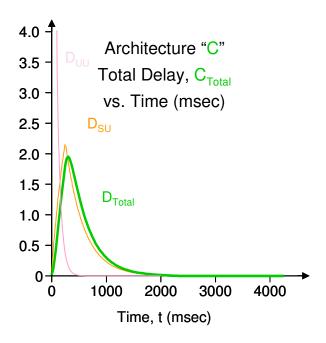

| 6.2.4  | Architecture C                                            | 117  |

| 6.2.5  | Architecture D                                            | 119  |

| 6.3    | Comparing Results Across Architectures                    | 121  |

| 6.3.1  | Scaling Issues                                            | 123  |

| 6.4    | Summary                                                   |      |

| 7 Two  | Larger Examples >                                         | 126  |

| 7.1    | Example One: Data Exfiltration                            |      |

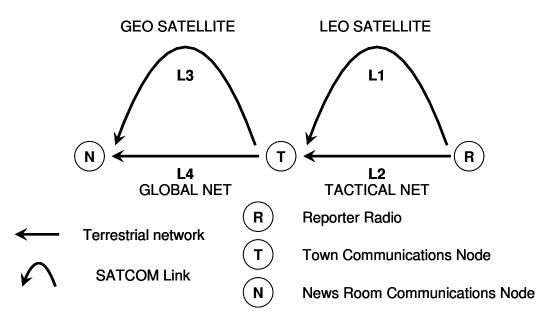

| 7.1.1  | Problem Definition                                        | 127  |

| 7.1.2  | Large-Grain Delay Descriptions                            | 128  |

| 7.1.3  | Alternative Problem Architectures                         | 130  |

| 7.1.4  | Delay Characterization                                    | 132  |

| 7.1.5  | Data Characterization                                      | . 132 |

|--------|------------------------------------------------------------|-------|

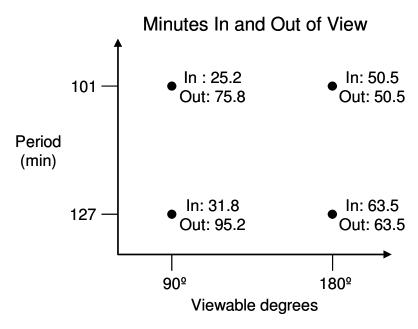

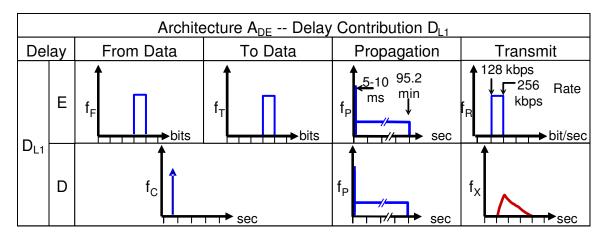

| 7.1.6  | Characterizing Delay D <sub>L1</sub>                       | . 133 |

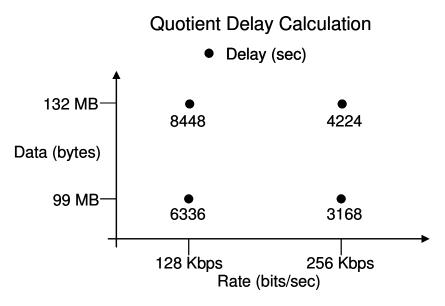

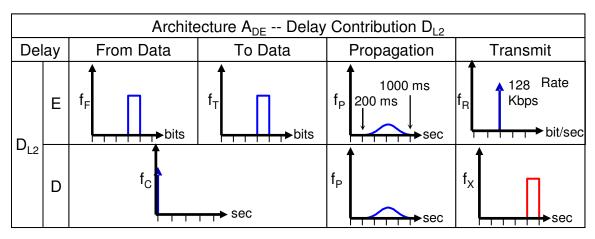

| 7.1.7  | Characterizing Delay D <sub>L2</sub>                       | . 137 |

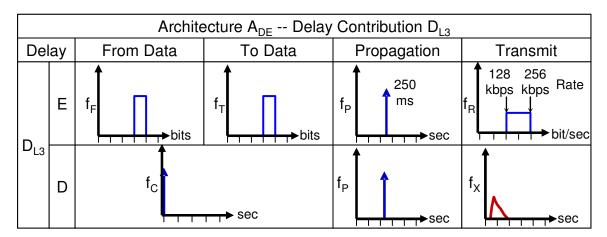

| 7.1.8  | Characterizing Delay D <sub>L3</sub>                       | . 139 |

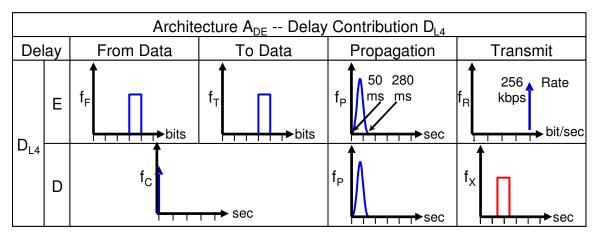

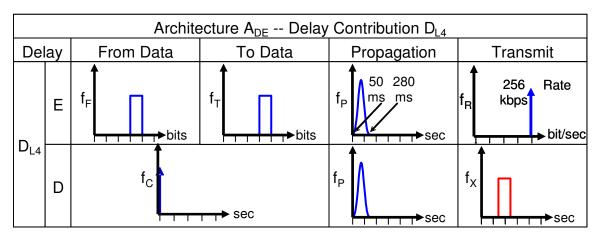

| 7.1.9  | Characterizing Delay D <sub>L4</sub>                       | . 140 |

| 7.1.10 | Combining Component Performance Descriptions               |       |

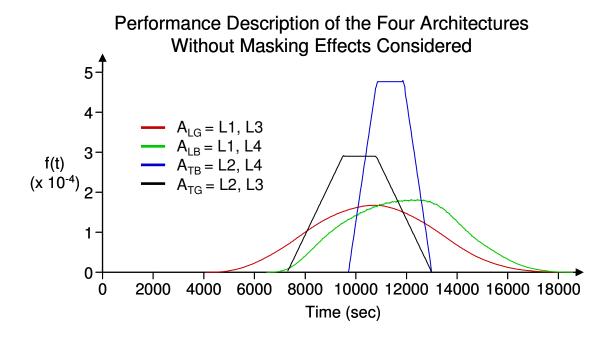

| 7.1.11 | Comparing the VIDEO Performance of the Alternatives        | . 142 |

| 7.1.12 | Example One Summary                                        | . 144 |

| 7.2    | Example Two: A Service Oriented Architecture Based Service | . 144 |

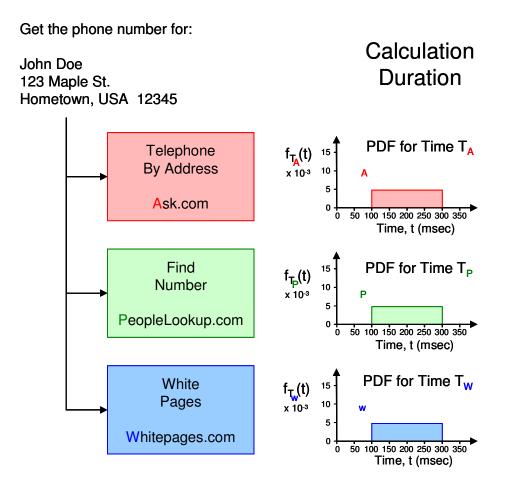

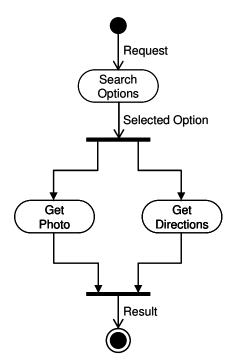

| 7.2.1  | Problem Description                                        |       |

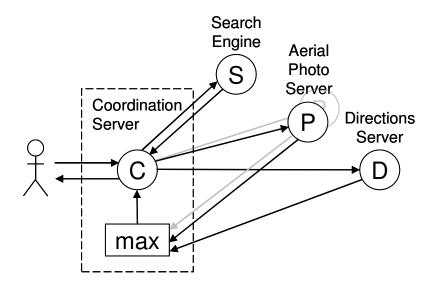

| 7.2.2  | Large Grain Delay Descriptions                             |       |

| 7.2.3  | Delay Characterization                                     |       |

| 7.2.4  | Data Characterization                                      | . 149 |

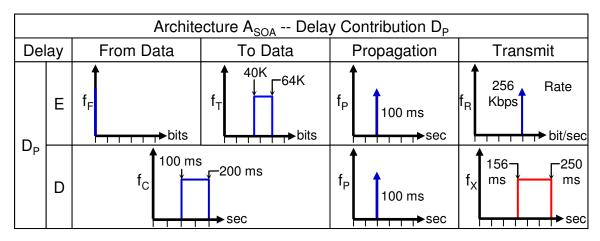

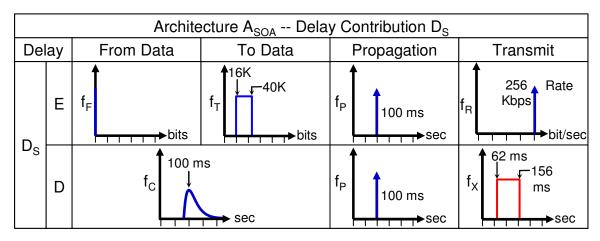

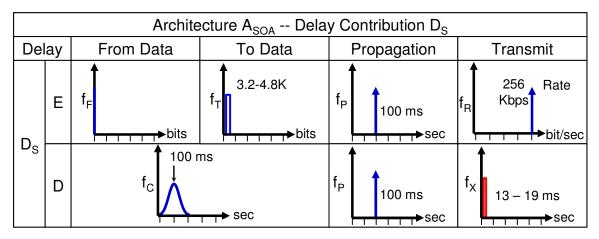

| 7.2.5  | Delay Characterization to the Photo Server, P              | . 149 |

| 7.2.6  | Delay Characterization to the Search Engine, S             | . 150 |

| 7.2.7  | Delay Characterization to the Directions Server, D         | . 151 |

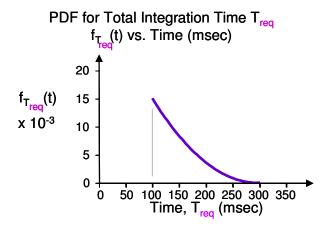

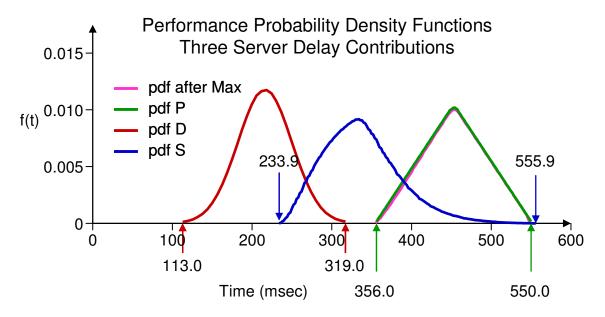

| 7.2.8  | Combining Server Delays                                    | . 153 |

| 7.2.9  | Example Two Summary                                        |       |

| 7.3    | Summary                                                    | . 159 |

|        | CAPE Tool                                                  |       |

|        | Introduction                                               |       |

|        | The CAPE Tool Design                                       | . 161 |

| 8.3    | Code Snippet Functionality                                 |       |

| 8.3.1  | Function Definitions                                       |       |

| 8.3.2  | Modeling Topological Aspects of the Architecture           |       |

| 8.3.3  | CAPE Evaluation of the PPI                                 |       |

|        | Library Support                                            |       |

| 8.4.1  | Results                                                    |       |

| 8.4.2  | A Simple Complete Example                                  |       |

| 8.4.3  | Summary                                                    |       |

|        | nodology Validation                                        |       |

|        | Introduction                                               |       |

|        | Modeling Technique                                         |       |

|        | Result Comparison Techniques                               |       |

| 9.3.1  | Chi Squared Goodness of Fit Testing                        | . 179 |

| 9.3.2  | Norm Based Difference Measurement - MESA vs. CAPE          |       |

|        | Validation Examples                                        |       |

| 9.4.1  | Example One – The Army Tactical Environment                |       |

| 9.4.2  | Example Two – Real Estate Service                          |       |

|        | Comparing MESA and CAPE Results Quantitatively             |       |

| 9.5.1  | Hypothesis Testing - MESA vs. CAPE                         |       |

|        | Conclusion                                                 |       |

|        | Summary                                                    |       |

| TO Con | tributions and Future Research                             | . 205 |

| 10.1   | Introduction                                                 | 205 |

|--------|--------------------------------------------------------------|-----|

| 10.2   | Research Contributions                                       | 207 |

| 10.3   | Future Research                                              | 209 |

| 10.3.1 | Expand Offered Workload Analysis                             | 209 |

| 10.3.2 | Improve Model Implementation Efficiency                      |     |

| 10.3.3 | Applying CAPE to the Design of Software Architectures        | 210 |

| 10.3.4 | Simplify Performance Specifications Graphical User Interface |     |

| 10.3.5 | Generate Parameterized Pre-built Architectural Entity Models | 211 |

| 10.3.6 | Quantify Improvement Factor                                  | 212 |

| 10.3.7 | Specify an Appropriate Multi-Attribute Utility Function      | 212 |

| 10.3.8 | Specify a Compatible Cost Model for a Bayes Decision         |     |

| 10.3.9 | Summary                                                      |     |

| A Fun  | ction Model and Elementary Function Operations               | 215 |

| A.1    | Introduction                                                 | 215 |

| A.2    | Representing Functions of One Variable                       | 215 |

| A.3    | Operations on Functions                                      | 216 |

| A.4    | Scalar Multiplication                                        | 216 |

| A.5    | Shift Operation                                              |     |

| A.6    | Integration Operation                                        | 216 |

| A.7    | Differentiation Operation                                    |     |

| A.8    | Convolution Operation                                        |     |

| A.9    | makeCanonical() Operation                                    |     |

| A.10   | Representing Functions of Two Variable                       | 217 |

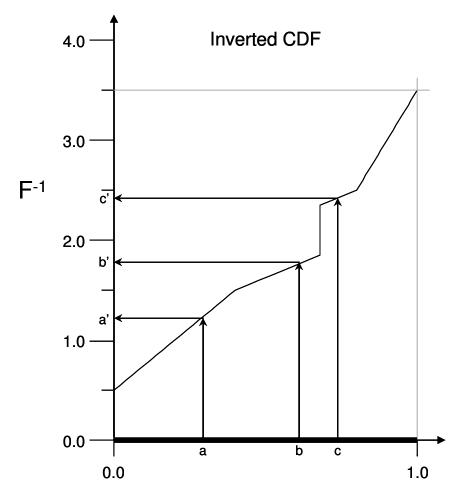

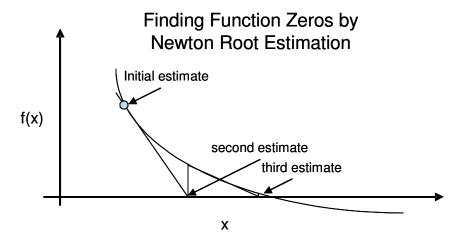

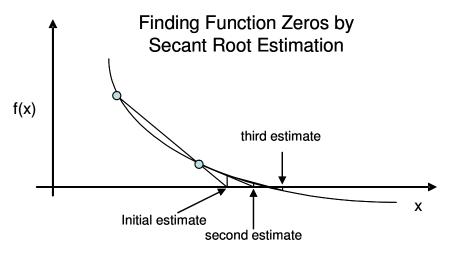

| A.11   | Quasi-Arbitrary Random Variable Generation Functions         | 218 |

|        | ailed Examples of Uncertainty                                |     |

|        | nputational Methods and Verification                         |     |

| C.1    | Introduction                                                 | 224 |

| C.2    | Summation                                                    | 224 |

| C.3    | Quotient                                                     | 228 |

| C.4    | MIN                                                          |     |

| C.5    | MAX                                                          |     |

| D PLC  | OT Library Functionality                                     | 237 |

| REFERE | NCES                                                         | 239 |

# **LIST OF TABLES**

| Tables    |                                                            | Page |

|-----------|------------------------------------------------------------|------|

| Table 2.1 | Performance and Domain Specific Architectures              | 3̈́9 |

| Table 2.2 | Desirable approach attributes                              | 41   |

| Table 6.1 | Standard data table for comparing transition delays        |      |

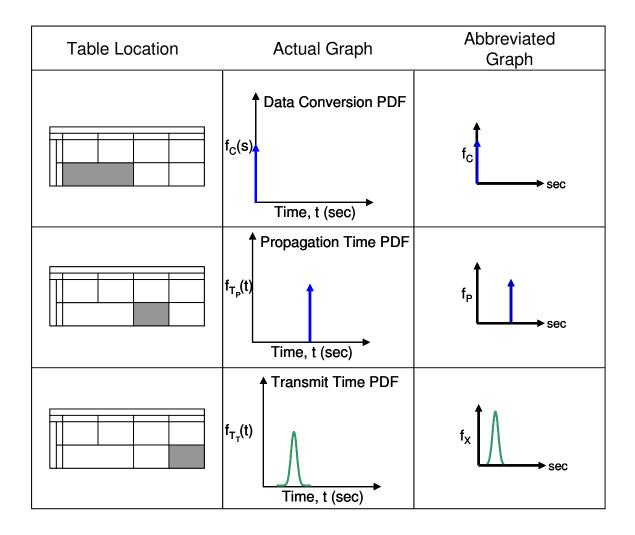

| Table 6.2 | Graph abbreviations used in analysis tables that follow    | 109  |

| Table 7.1 | Summary of data exfiltration system performance estimates. | 130  |

| Table 7.2 | Table of architectures considered                          | 131  |

| Table 7.3 | PPI Results for Data Exfiltration                          |      |

# **LIST OF FIGURES**

| Figures                  |                                                                                    | Page     |

|--------------------------|------------------------------------------------------------------------------------|----------|

| Figure 1.1               | V-type systems development process                                                 | 5        |

| Figure 1.2               | Implementations possible from the systems development proce                        |          |

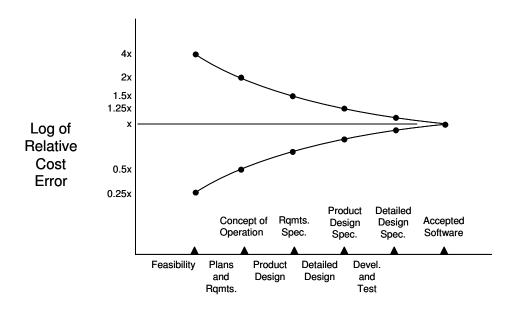

| Figure 3.1               | Visual description of the experiment                                               | 48       |

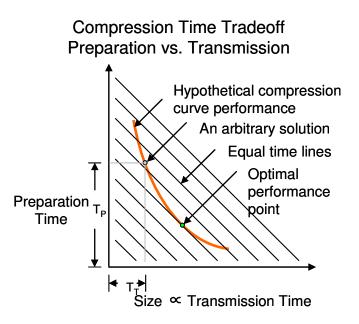

| Figure 3.2               | Curve characterizing processing and transmission time tradeof                      |          |

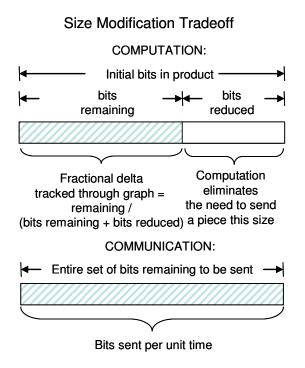

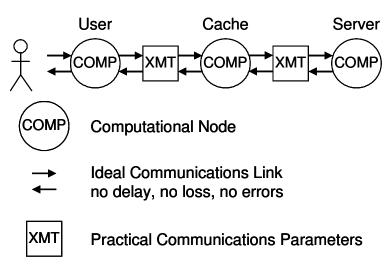

| Figure 3.3               | Computation and communications normalization                                       | 54       |

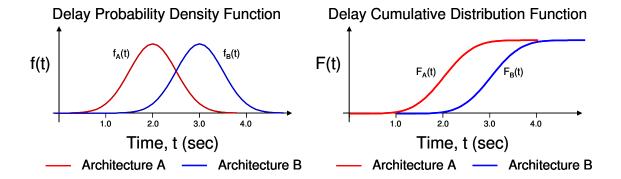

| Figure 4.1               | Delay density function and cumulative distribution function                        | 62       |

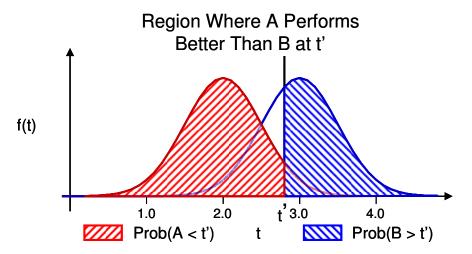

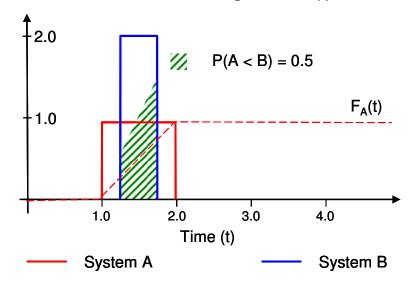

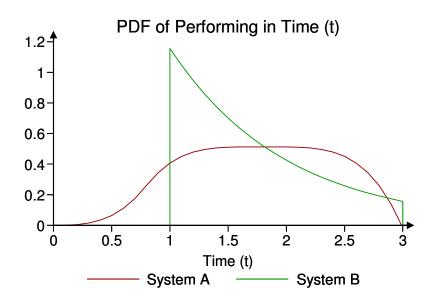

| Figure 4.2               | Calculating the probability System A outperforms System B                          | 64       |

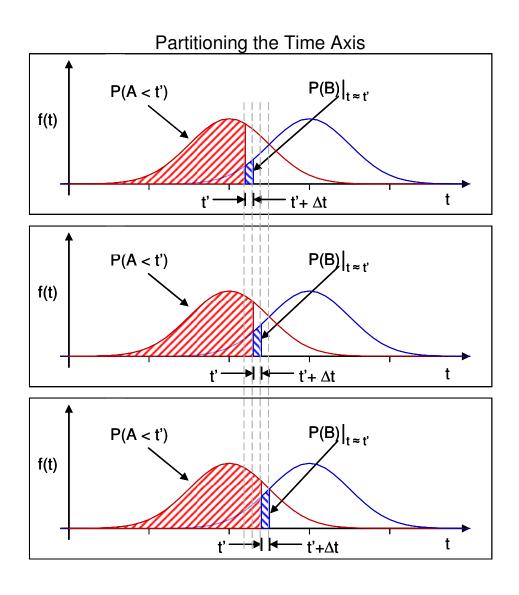

| Figure 4.3               | Evaluation of the P(A < t') for increasing values of t'                            | 65       |

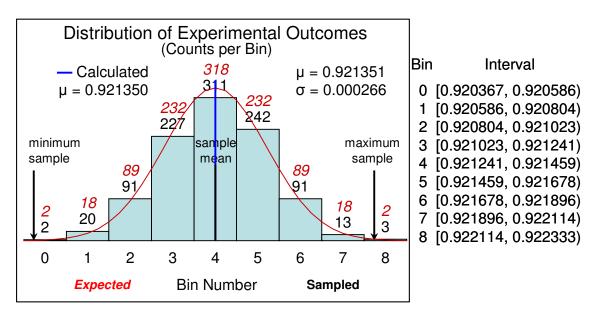

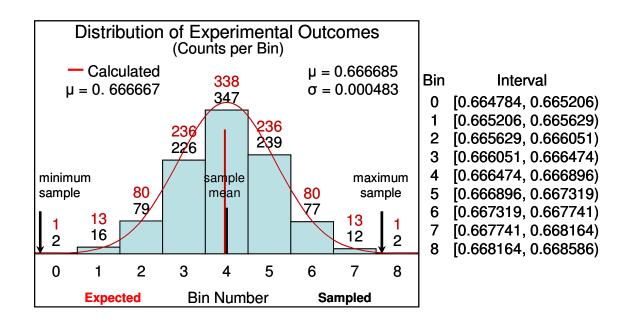

| Figure 4.4               | Simulation results for comparing systems from Figure 4.2                           | 71       |

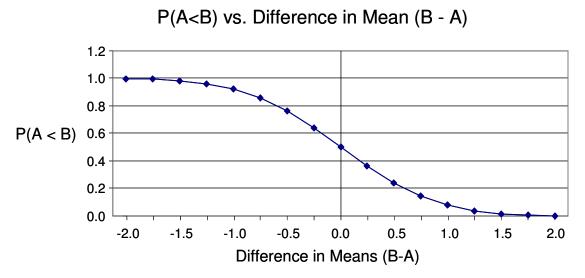

| Figure 4.5               | PPI values vs. difference in mean (B – A)                                          | 72       |

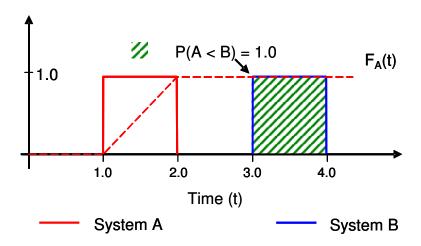

| Figure 4.6               | PPI calculation: non-overlapping performance descriptions                          | 73       |

| Figure 4.7               | PPI calculation: overlapping performance descriptions                              | 74       |

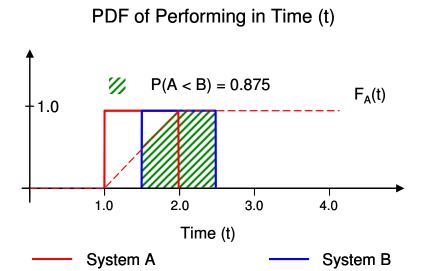

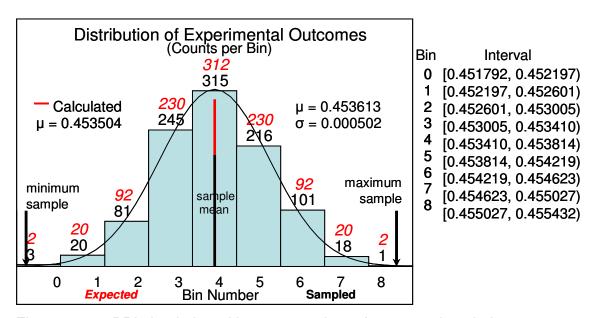

| Figure 4.8               | PPI simulation: overlapping performance descriptions                               | 75<br>70 |

| Figure 4.9               | PPI calculation: complete overlap of performance descriptions                      | 76       |

| Figure 4.10              | PPI simulation: narrow overlapping architecture                                    | 76<br>70 |

| Figure 4.11              | PPI calculation: discrete example                                                  | 78<br>70 |

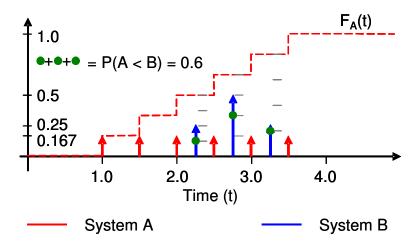

| Figure 4.12              | PPI simulation: discrete example                                                   | 79       |

| Figure 4.13              | Non-symmetric performance description comparison                                   | 80<br>80 |

| Figure 4.14              | PPI simulation: Non-symmetric performance description                              | 85       |

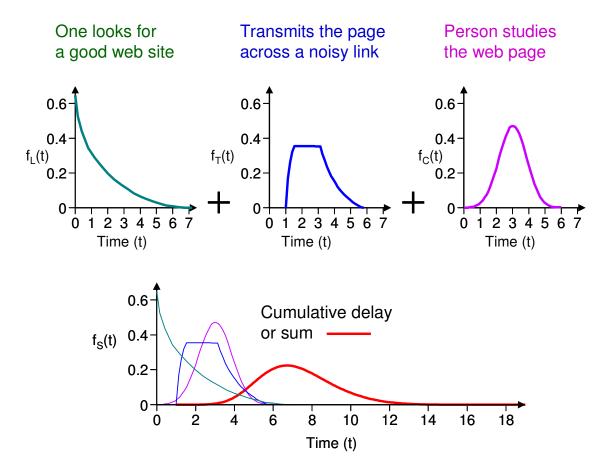

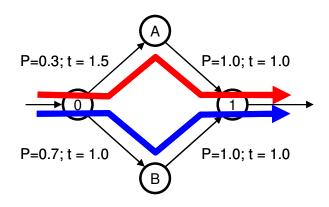

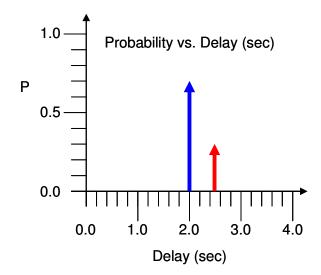

| Figure 5.1               | Summing process for activity performance descriptions                              | 88       |

| Figure 5.2               | Source-sink performance descriptions for quotient calculation                      | 90       |

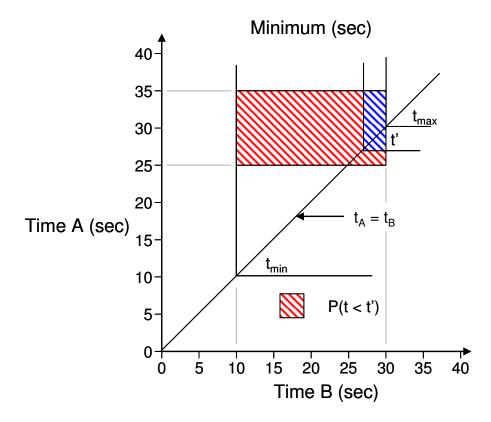

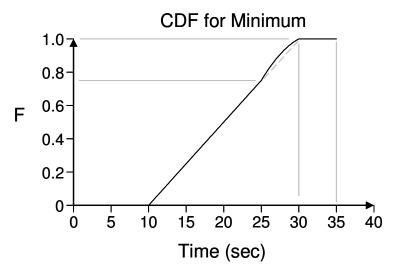

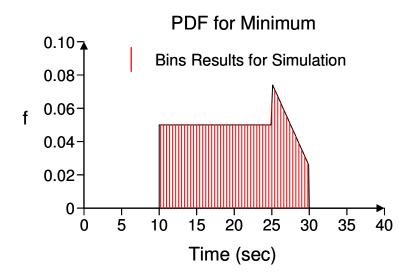

| Figure 5.3               | Example case where first result is sufficient  Minimum function computation result | 91       |

| Figure 5.4<br>Figure 5.5 | Minimum function computation result Timing for a subtasks processed in parallel    | 93       |

| Figure 5.6               | Maximum function computation result                                                | 94       |

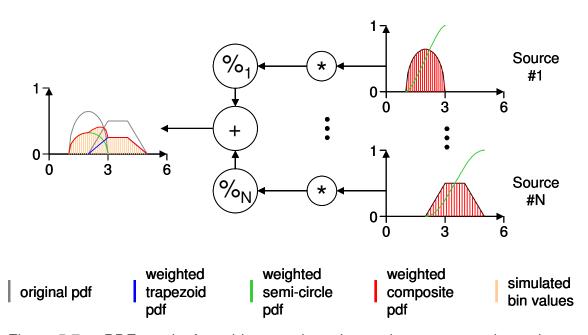

| Figure 5.7               | PDF result of combing two data classes in a common channel                         | 96       |

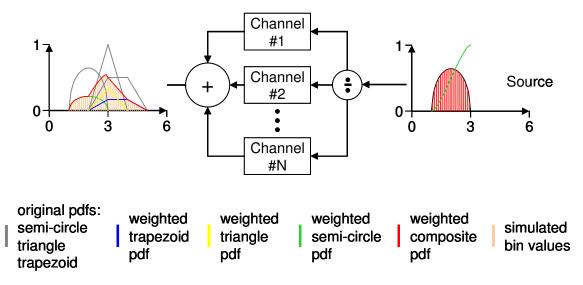

| Figure 5.8               | A single class of data is transmitted over any of multiple paths                   | 97       |

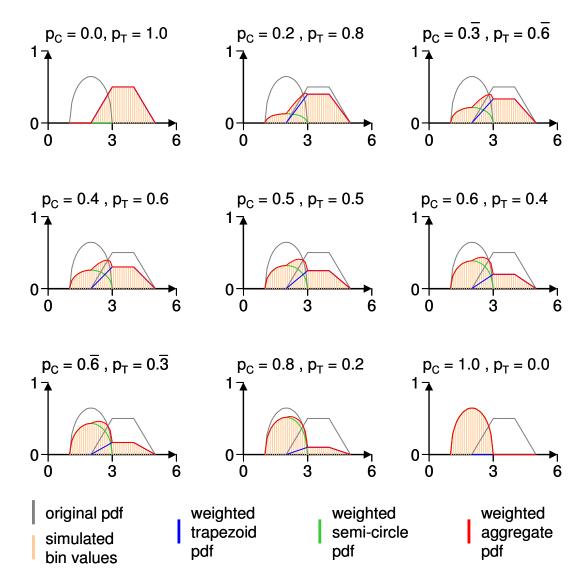

| Figure 5.9               | Simulation confirmation of weighted composite calculations                         | 98       |

| Figure 5.10              | Composite delay result for example two path calculation                            | 99       |

| Figure 6.1               | Classical three tier architecture                                                  | 103      |

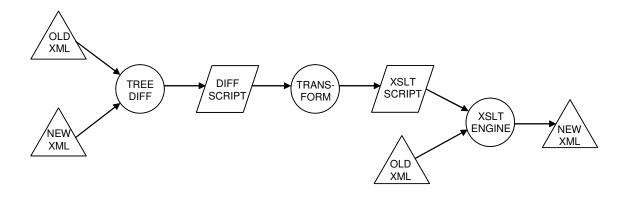

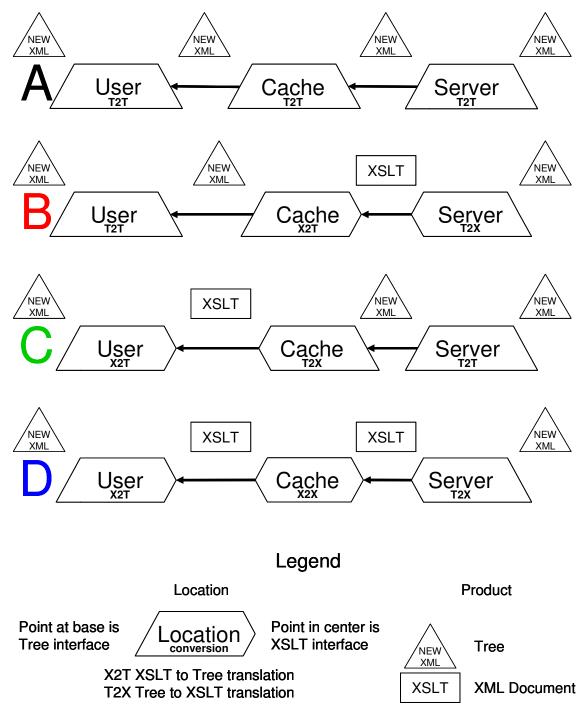

| Figure 6.2               | XML Tree Transform Process Example                                                 | 104      |

| Figure 6.3               | Alternative example architectures                                                  | 105      |

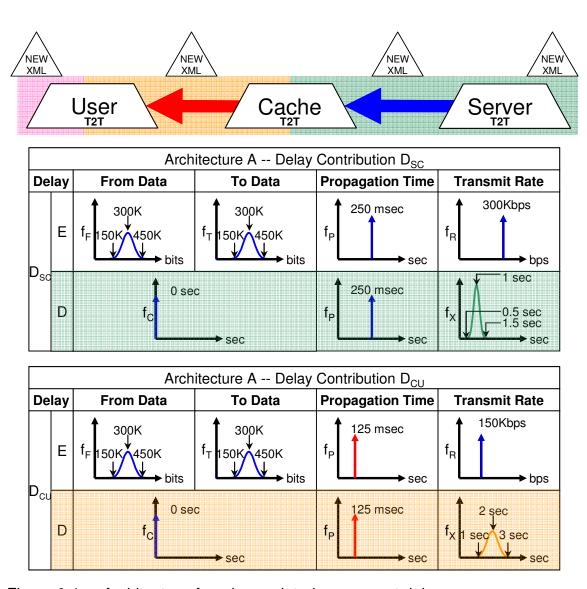

| Figure 6.4               | Architecture A and associated component delays                                     | 113      |

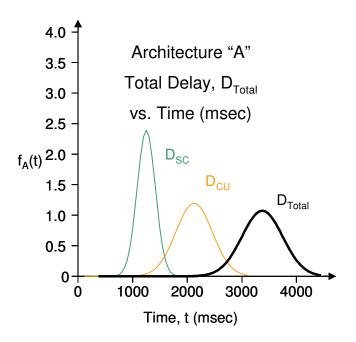

| Figure 6.5               | Performance description for architecture A                                         | 114      |

| Figure 6.6               | Architecture B and associated delay tables                                         | 116      |

| Figure 6.7               | Performance description for architecture R                                         | 117      |

| Figure 6.8  | Architecture C and associated delay tables                               | 118 |

|-------------|--------------------------------------------------------------------------|-----|

| Figure 6.9  | Performance description for architecture C                               | 119 |

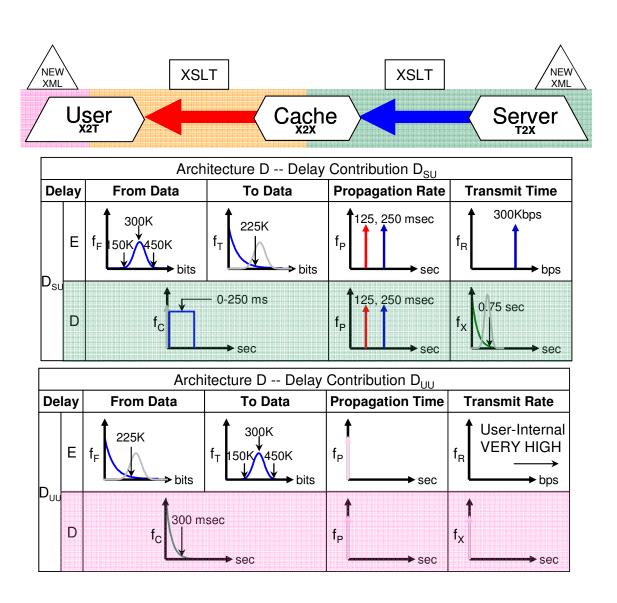

| Figure 6.10 | Architecture D and associated delay tables                               | 120 |

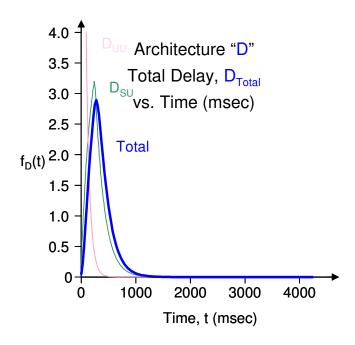

| Figure 6.11 | Performance description for architecture D                               | 121 |

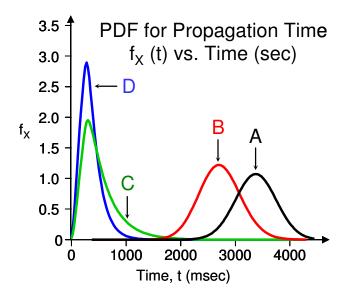

| Figure 6.12 | Plot of all four architecture delay descriptions                         | 122 |

| Figure 6.13 | Summarizing all architectural performance results                        | 123 |

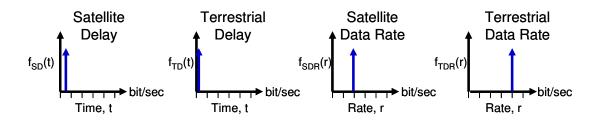

| Figure 6.14 | Establishing related propagation delays and data rates                   | 124 |

| Figure 6.15 | Result of scaling the satellite delay to the terrestrial delay           | 125 |

| Figure 7.1  | Data exfiltration architecture and labeling convention                   | 131 |

| Figure 7.2  | LEO satellite accessibility times                                        | 134 |

| Figure 7.3  | Critical points for LEO satellite transmit delay                         | 135 |

| Figure 7.4  | Architecture A <sub>DE</sub> , characterization of delay D <sub>L1</sub> | 136 |

| Figure 7.5  | Combined delay contributions for D <sub>L1</sub>                         | 137 |

| Figure 7.6  | Architecture A <sub>DE</sub> , characterization of delay D <sub>L2</sub> | 138 |

| Figure 7.7  | Architecture A <sub>DE</sub> , characterization of delay D <sub>L3</sub> | 139 |

| Figure 7.8  | Architecture A <sub>DE</sub> , characterization of delay D <sub>L4</sub> | 140 |

| Figure 7.9  | Video architecture performance descriptions                              | 141 |

| Figure 7.10 | Initial activity diagram for SOA real estate service                     | 146 |

| Figure 7.11 | Symbolic SOA real estate service architecture graph                      | 147 |

| Figure 7.12 | Architecture SOA, Photo Server delay                                     | 150 |

| Figure 7.13 | Architecture SOA, Aerial Search Engine delay                             | 151 |

| Figure 7.14 | Architecture SOA, Directions Server delay                                | 152 |

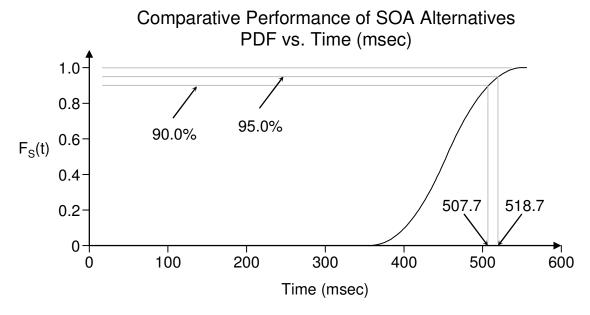

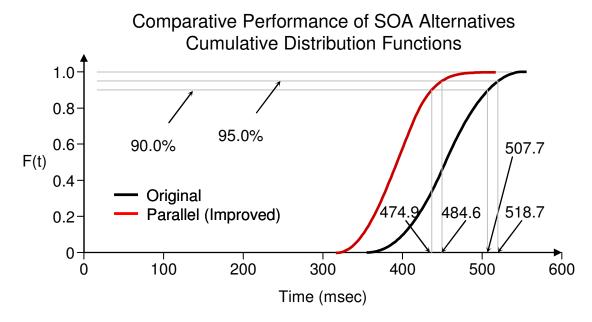

| Figure 7.15 | Cumulative results for describing the delays of each server              | 154 |

| Figure 7.16 | Projected performance of original example SOA                            | 155 |

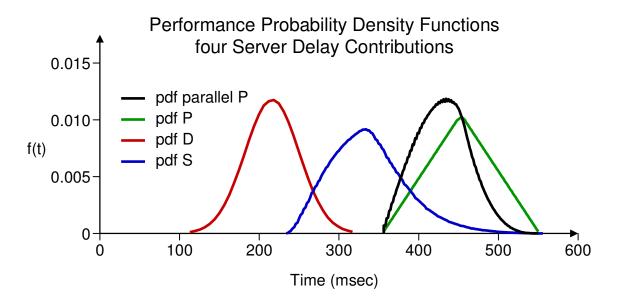

| Figure 7.17 | Server contributions with parallel Photo Server                          | 156 |

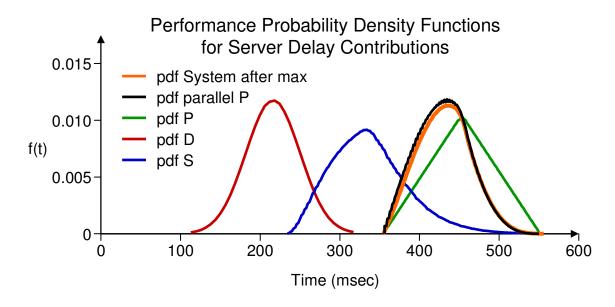

| Figure 7.18 | Performance of parallel Photo Server architecture                        | 157 |

| Figure 7.19 | Projected performance of modified example SOA                            | 158 |

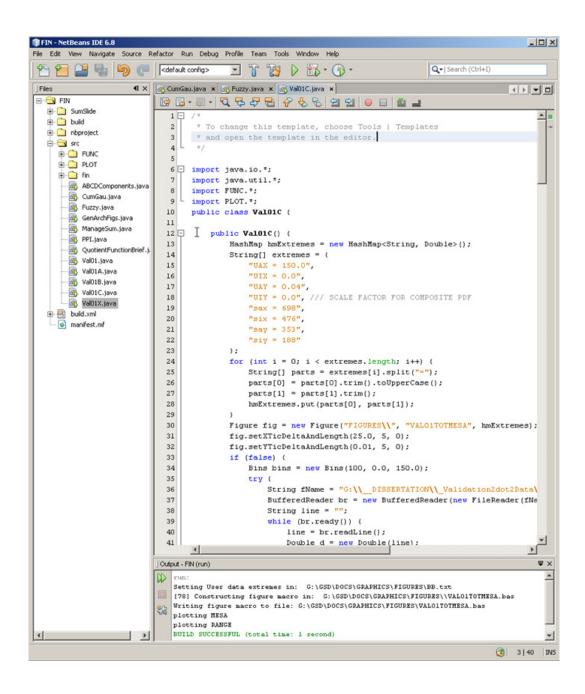

| Figure 8.1  | NetBeans IDE with partial code templates                                 | 162 |

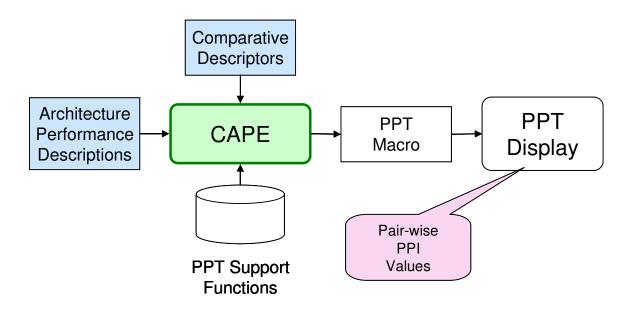

| Figure 8.2  | CAPE tool structure - PDF analysis                                       | 164 |

| Figure 8.3  | CAPE tool structure - PPI analysis                                       | 165 |

| Figure 8.4  | Building a Function point-wise within the code                           | 166 |

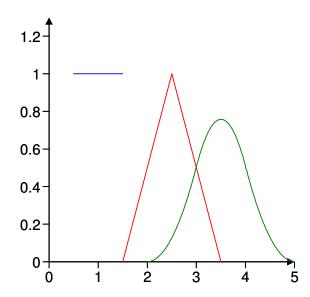

| Figure 8.5  | CAPE pdf functions validating the chapter nine Army example              | 167 |

| Figure 8.6  | CAPE used to compute PPI                                                 | 169 |

| Figure 8.7  | CAPE text output from example                                            | 172 |

| Figure 8.8  | CAPE input for example analysis                                          | 173 |

| Figure 8.9  | Raw macro result once executed within PPT                                | 174 |

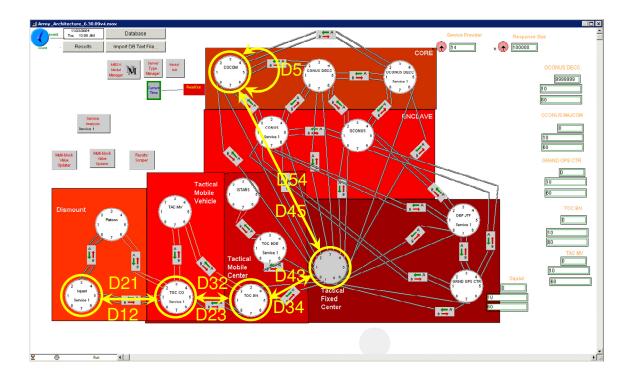

| Figure 9.1  | Top level MESA model for Army SOA example                                | 185 |

| Figure 9.2  | Detailed CAPE delays with bounding values                                | 186 |

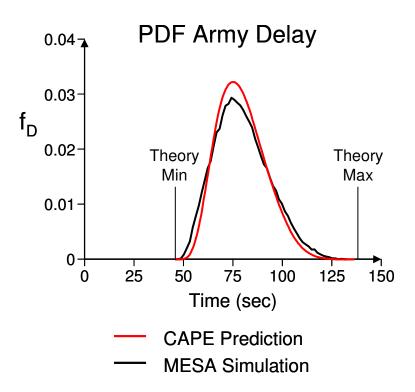

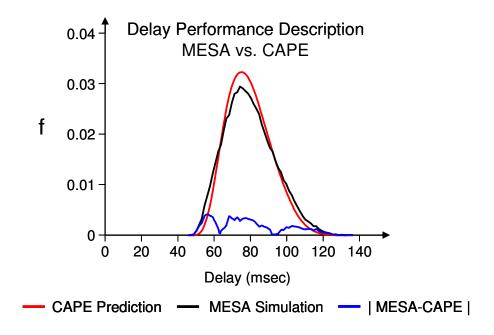

| Figure 9.3  | PDF comparison of CAPE and MESA results Army example                     | 187 |

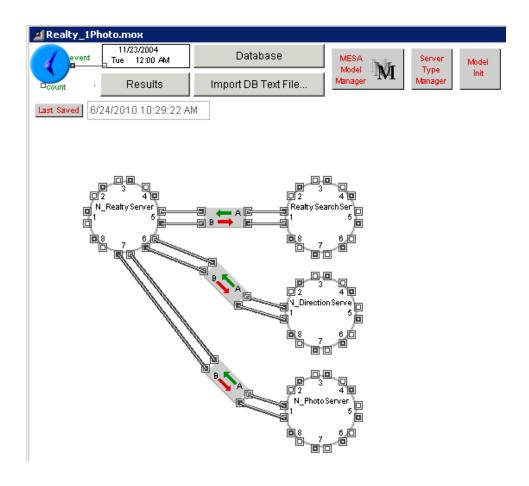

| Figure 9.4  | MESA model for the real estate service (single photo server)             | 189 |

| Figure 9.5  | Single photo server delay contributions                                  | 190 |

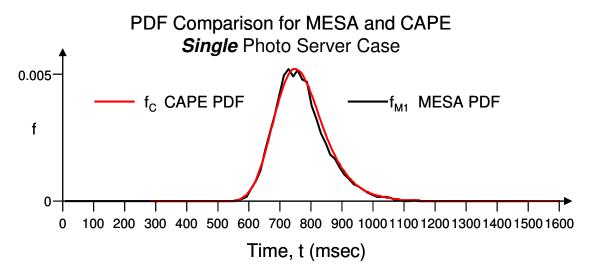

| Figure 9.6  | Total delay for single photo server                                      | 191 |

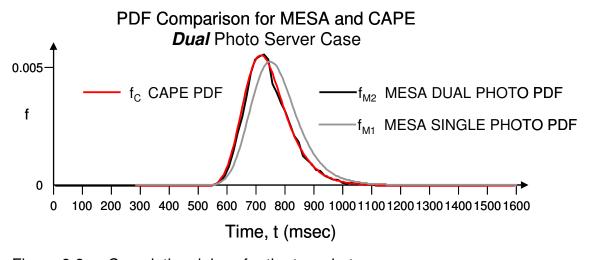

| Figure 9.7  | Transmission delay contribution for the two photo server case            | 192 |

| Figure 9.8  | Cumulative delays for the two photo server case                          | 192 |

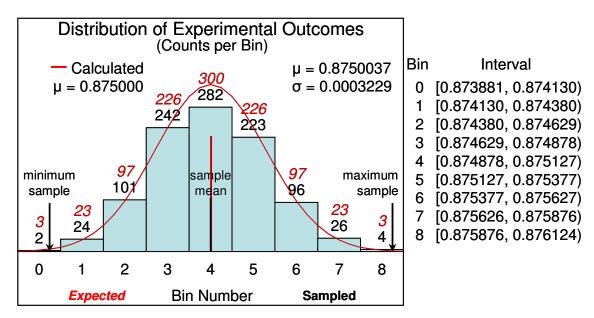

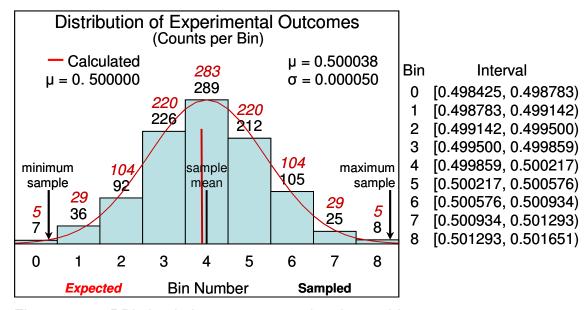

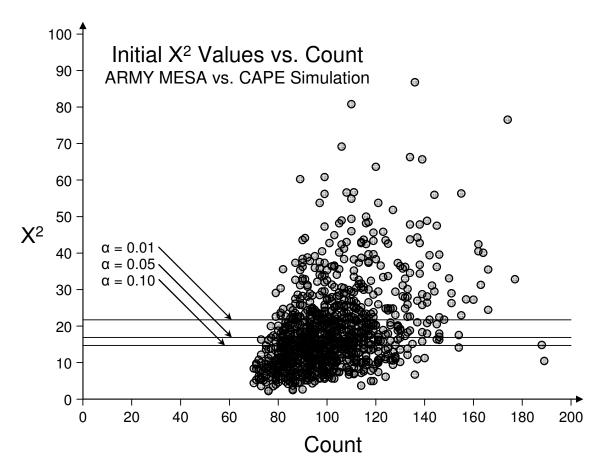

| Figure 9.9    | Initial $\chi^2$ values vs. count needed to meet rules of thumb | 194 |

|---------------|-----------------------------------------------------------------|-----|

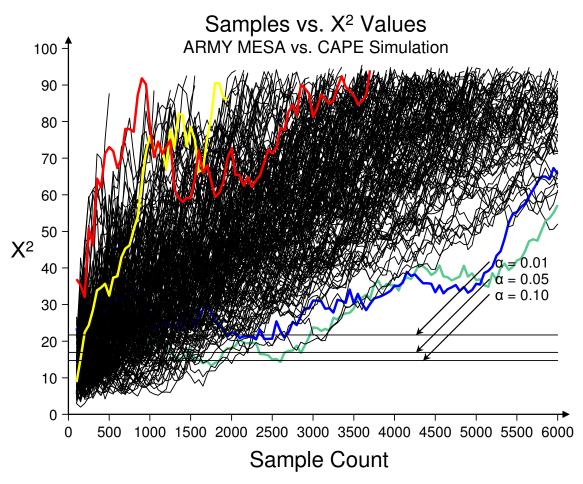

| Figure 9.10   | Plot of $\chi^2$ values over time                               | 195 |

| Figure 9.11   | Absolute MESA-CAPE estimate difference— Army example            | 197 |

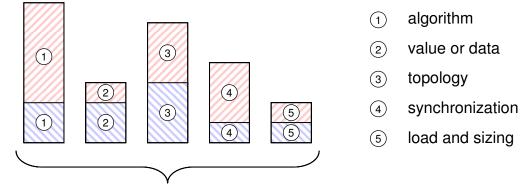

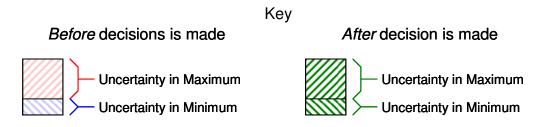

| Figure 9.12   | Uncertainty contributions before design decisions are made      | 201 |

| Figure 9.13   | Changing performance bounds as decisions are made               | 202 |

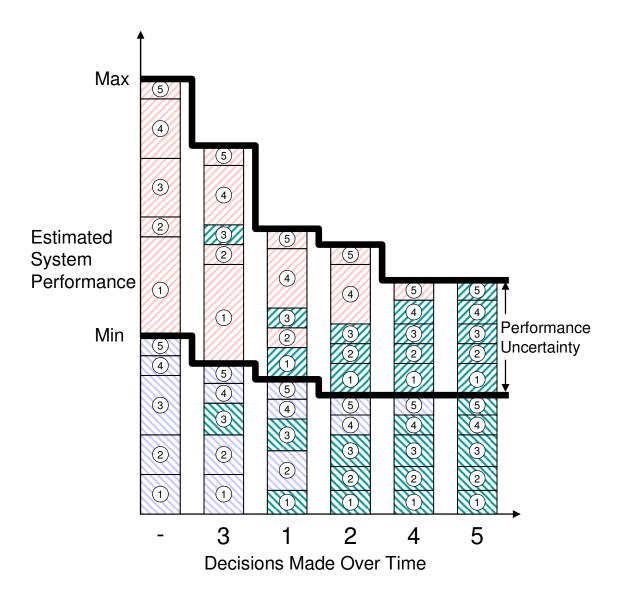

| Figure 9.14   | Boehm software development cost uncertainty description         | 203 |

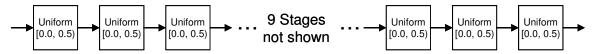

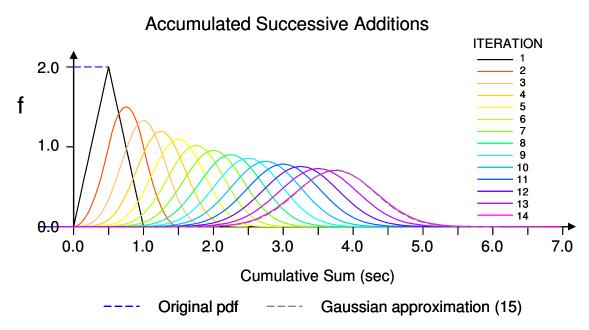

| Figure C.0.1  | Fifteen independent stage uniformly distributed delay line      | 224 |

| Figure C.0.2  | Iterative summation of uniform densities                        | 225 |

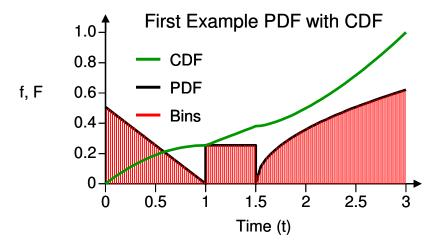

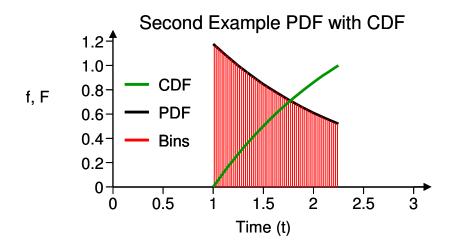

| Figure C.0.3  | An irregular pdf describing system performance                  | 227 |

| Figure C.0.4  | Another pdf describing system performance                       | 227 |

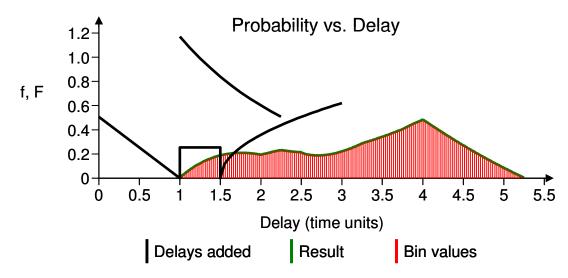

| Figure C.0.5  | Convolution of pdfs from Figure C.3 and Figure C.4              | 228 |

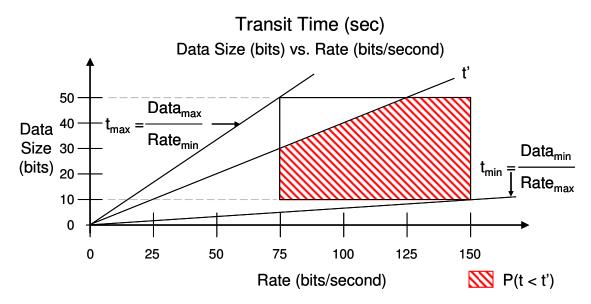

| Figure C.0.6  | Relationship of transmit time to data size and data rate        | 229 |

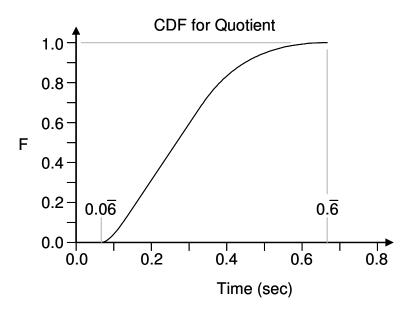

| Figure C.0.7  | Quotient cumulative distribution function for the example       | 230 |

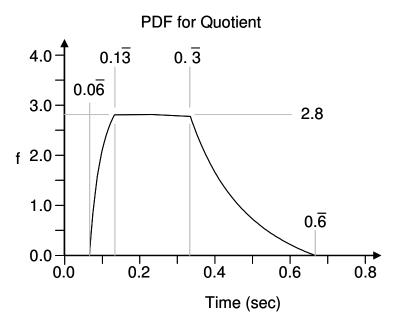

| Figure C.0.8  | Example probability density function                            | 231 |

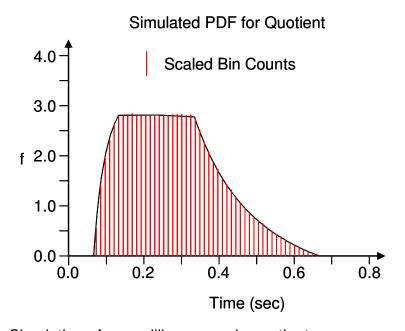

| Figure C.0.9  | Simulation of one million example quotients                     | 231 |

| Figure C.0.10 | Example two input minimum geometry calculation                  | 232 |

| Figure C.0.11 | Calculated cdf MIN for two input example                        | 233 |

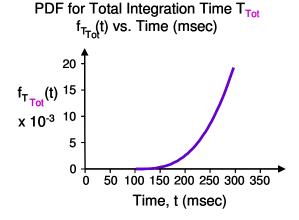

| Figure C.0.12 | PDF for minimum of the uniform joint pdf                        | 234 |

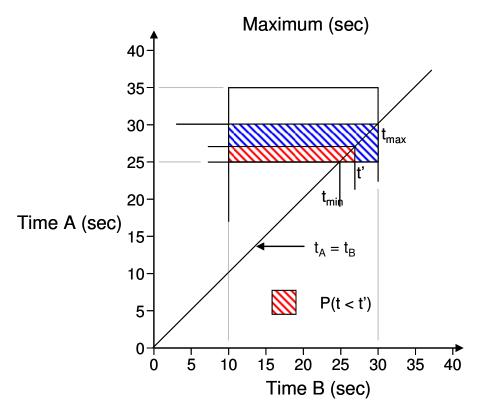

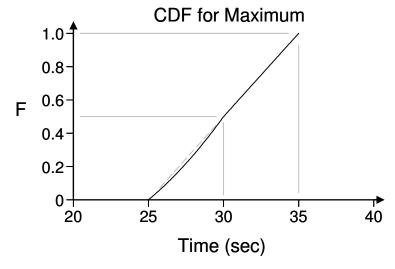

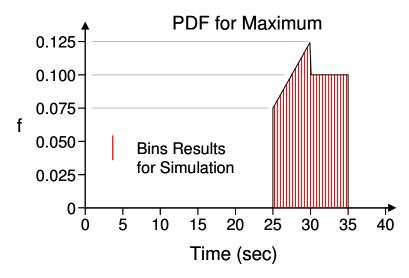

| Figure C.0.13 | Example two input maximum pdf geometry calculation              | 235 |

| Figure C.0.14 | Example cumulative distribution – two input example             | 235 |

| Figure C.0.15 | Example two input maximum pdf calculation                       | 236 |

**ABSTRACT**

A METHODOLOGY FOR MAKING EARLY COMPARATIVE ARCHITECTURE

PERFORMANCE EVALUATIONS

Gerald S. Doyle, PhD

George Mason University, 2010

Dissertation Director: Dr. Elizabeth L. White

Complex and expensive systems' development suffers from a lack of method for

making good system-architecture-selection decisions early in the development

Failure to make a good system-architecture-selection decision process.

increases the risk that a development effort will not meet cost, performance and

schedule goals. This research provides a method to mitigate that risk based on

the idea that a development can be characterized as the management of

uncertainties in a probabilistic experiment. The method developed shows how to

estimate the probability that an arbitrary implementation of one system-

architecture will perform better than an arbitrary implementation of an alternate

system architecture.

The analysis technique presented acknowledges that many implementation

uncertainties exist at system-architecture-selection time and identifies steps that

can be used to characterize these uncertainties. The process by which uncertainty descriptions are combined into architectural performance descriptions is presented. Once all alternative system architecture performance descriptions are developed relative system architecture performance comparisons can be made.

After the analysis technique is described, three examples are considered. The first example is a simple three tier web-enabled database application. This small web application is used to illustrate the analysis method and demonstrate some methods for characterizing uncertainties. The next two examples are more complex. These examples expose a broader set of uncertainties and show how to handle cases where large numbers of uncertainties exist. Sections on validation of results follow. The dissertation concludes with a list of future research opportunities in this area.

#### Chapter 1

#### Introduction

#### 1.1 Introduction

Developing a large system is a complex task that requires an understanding of the functional and non-functional requirements as documented in the systems requirements specification. Functional requirements relate to what the system does, and non-functional requirements relate to system quality. Non-functional requirements (often called quality attributes) include reliability, modifiability, portability, security, and performance, among others. Requirements relating to quality influence early system development much like functional requirements. Unlike functional requirements, performance requirements are often addressed later in the development process, and often addressed in an unstructured manner.

System architectures can be used to help manage the complexity inherent in systems development. A system architecture is a high level description of the proposed solution. It is valued for its ability to describe the large grain structure

of the objective system, suppressing unnecessary detail. Since a system's architecture affects all types of requirements, it is critical that a suitable system architecture be selected early in the development process.

A system architecture can be characterized as an enumeration of the system's large-grain components and the connections between those components. There are several techniques for describing system architectures. The earliest work in the software field used boxes (components) of various shapes, combined with lines (connectors) to characterize the interactions between components. This description based on combining boxes and lines creates a high-level pictorial representation of the proposed system structure. Many current description techniques are similar.

The most concise insight on the impact that the system architecture has on system performance comes from work done by Clements and Lakos. "Whether or not a system will be able to exhibit its desired (or required) quality attributes is largely determined by the time the architecture is chosen." [ClNo96] Similarly Lakos [Lako96] writes, "If we fail to address our performance goals in the beginning, we may adopt architectures or coding practices that will preclude our ever achieving these goals, short of rewriting the entire system."

While there are a number of important quality attributes associated with systems, performance is the one that is the focus of this research.

#### 1.2 Systems Development Process

A systems development process is established in order to make the development process repeatable and to ensure that the product will have known quality. It usually enumerates a sequence of steps that the developer should follow. System development success hinges on meeting established goals for three criteria: cost, schedule, and performance [OMBC09]. Failing to achieve any of these goals compromises the project.

One of the primary sources of failing to meet goals is related to change. Changes resulting from either re-architecting or redesigning increase cost and extend schedules. The costs associated with making changes are accrued in activities like revising functional requirements, changing quality attribute specifications, modifying the system architecture, and changing the system design to fix unmet quality goals and functional requirements. System development costs are not uniformly distributed over the system lifecycle and neither are the costs of change. There is general agreement that mistakes made early in the system development process are more costly to correct than those made later in the lifecycle [WiKe00]. There are disproportionately large expenses associated with architectural modification due to the deep understanding that is required to successfully make significant architectural changes and due to the magnitude and number of the changes that are routinely

needed [CIDB98]. Reducing the risk of making an inappropriate architectureselection-decision will decrease the expected cost of the development.

There are many approaches to systems development. A typical system is built using a development model like the classical waterfall model, waterfall models with feedback, V-models [Somm04], or alternatives. The development model establishes a sequence of activities or steps that guide developers as they plan the work to be done. This series of steps usually begins with requirements specification and runs through end-of-life disposition. While different development approaches address different development concerns, each approach includes some type of architecture design phase followed by a detailed design phase. Most include feedback mechanisms between the phases. The waterfall model with feedback, for example, helps accommodate the reality that the dividing line between the architecture design and detailed design phases is imprecise. The model's feedback paths allow information learned while performing the detailed design to force changes in the architecture design. Architectural changes as well, often directly influence detailed design decisions. An architecture design phase is usually identified early in the step sequence. Once a particular problem is identified and system requirements are specified, an architecture-design effort identifies a set of potential or candidate architectures to be considered.

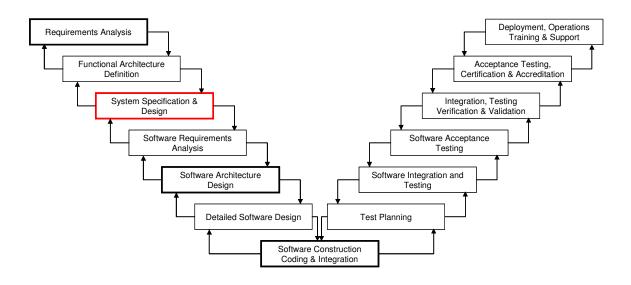

Figure 1.1 shows a V-model systems design process including an early architecture design phase, labeled "System Specification and Definition."

Figure 1.1 V-type systems development process

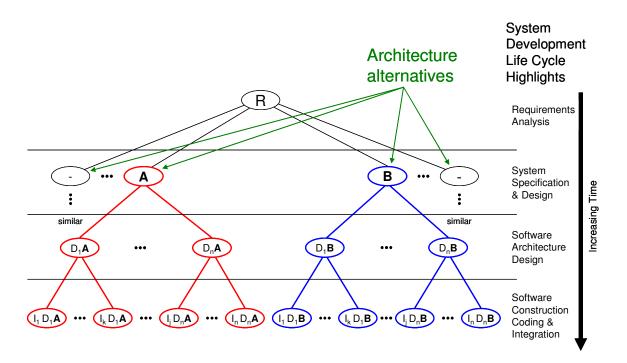

From a single set of requirements, there can be a number of different alternative architectures. In a similar way, from each architecture there can be a number of detailed designs, and again from each detailed design there can be a number of implementations. The implementations that can result from performing the intermediate design steps are shown in the bottom row of Figure 1.2. Branching off from the requirements specification at the top level are the alternative

architectures. Below them are the possible detailed designs, followed by the implementations.

Figure 1.2 Implementations possible from the systems development process

From that set of initial architectures, either a specific architecture may be selected or the architecture-selection decision may be delayed until further analysis is conducted. When the selection decision is delayed, another set of

steps is executed to refine each of the architecture options. The developer refines broader descriptions to more specific ones. For each of the choices considered, the product's required functions are assigned to architecture specific sub-systems or components. When the functions or the components to which they are assigned are complex, either may be decomposed again (possibly a number of times). This iterative process defines the structure of the detailed design. Eventually, one specific detailed design is selected from a number of possible alternatives.

In a similar way, for each design there is a set of reasonable implementations. As the implementation options are examined, the design process eventually locks-down the types of data structures to be used, the control flow of the computations, the amount of concurrency that will be provided, as well as a number of other factors. Each of these low level design decisions can be viewed as the selection of one specific choice from a number of options. Before the decision is made however, each decision carries with it an amount of uncertainty in the system performance.

## 1.3 Uncertainties Encountered in the Systems Development Process

That there are undefined parameters early in the system design, and that there are many design decisions yet to be made in the development processes leads to two conclusions: 1) not knowing the performance impact of the specific

implementation decisions (those yet to be made) means that uncertainties exist, and 2) both the sources and amounts of uncertainty will likely change over time. The uncertainties present in the earlier development stages are reduced as the detailed design decisions are made.

At architecture-selection time, there are a large number of implementation details that have not been decided. The uncertainty generated by not knowing these details prevents the designer from comprehensively and hence precisely assessing the expected performance of the final product. Any performance analysis method to be used early in development must be able to handle the fact that design details will be missing when architectural evaluations are conducted. Over the early to middle part of the development, the percentage of architectural design usually decreases as the product design matures, while the amount of detailed design increases as the design is refined and gets closer to the actual implementation. It is the specification of these details during the subsequent course of the system design that collectively determines the final performance of the instantiated system.

There are also non-technical issues that can affect the quality attributes resulting from executing the systems development process. Issues not directly related to the system actually built, but to the processes and people that are used to generate that implementation. A designer's capabilities, i.e., their knowledge

strengths and weaknesses, can vary widely. Different implementers will be either more or less efficient and do either a better or worse job in creating the implementation. Each of these non-technical uncertainties may lead to a different implementation and hence different performance expectations.

Until the implementation exists, an exact performance characterization of an "asproduced" system can not be established. Estimated values (with uncertainties) must be used for analysis. This research presents a structured method for managing these types of uncertainties.

#### 1.4 Performance Analysis to Date

Performance analysis is routinely done near the end of a development cycle and is informed by a number of design and code artifacts. Performance analysis near the beginning of the development cycle does not have access to this information. While most development processes already include an uncertainty reduction characteristic realized through iterative feedback, most performance evaluation methods do not. There are three methods often used to assess and improve system performance: code profiling, queuing analysis and modeling and simulation.

Over the past decade, engineers have begun to address performance issues but later in the development effort. They often use a cyclic performance-

improvement approach. There are two general cases. In the first case, available code elements are profiled so that code sections consuming larger proportions of time can be identified. Recoding "slow" sections then changes the performance. The profiling process is then repeated to quantify the performance of the modified system. The newly measured performance is compared with the desired performance goal. If the goal is not met, the profile-rewrite cycle continues until no further improvement seems possible [WiKe00]. In those cases, if performance is still considered to be unacceptable, system redesign or architectural changes provide the next target for making improvement [Bulk00].

In the second general case, the anticipated detailed design is analyzed using either queuing theory or simulation. These closely related methods are usually applied after the architecture-selection decision has been made. For both queuing models and simulation, detailed system models are usually created. These models typically require detailed design information, e.g., component topologies, data flow rates, queuing model strategies, execution time constants, etc. to characterize the proposed system effectively. The queuing or simulation approaches target performance estimation earlier than those that actually make measurements on code, but the required information is still not available until late in the development's detailed design phase. At this point, the developer can choose to wait for detailed design values to become available, or can provide estimates of structure and performance without knowing these details. In the first

case, waiting until later in the design process, the evaluation is delayed. In the second case, uncertainties are injected into the evaluation process. While the estimates such queuing and simulation models produce could give insight into performance uncertainty, there is seldom an attempt to characterize it.

#### 1.5 Architecture Performance Evaluation Options

In selecting an approach to evaluate architecture performance, there are at least three ways to proceed. From a conceptual point of view, if given sufficient resources, all implementations could be instantiated and tested across the anticipated input datasets to provide data for making performance comparisons (using a suitable performance metric). This technique would identify the architecture which produced the best performing implementation. This approach is impractical. Even for a small system, the set of implementations can be very large. At the opposite extreme, a single architecture could be selected (perhaps at random) to be developed. This is routinely what is done as state-of-the-art today. A third and more beneficial approach would be to perform an analysis on each of the alternative architectures to approximate the likely performance attributes of each, then base architecture selection on these estimated values.

By necessity such an analysis would have to speculate or assume the assignment of functions to components, the internals of component design, specify details of implementation, etc. Since the true design decisions have not

yet been made, such estimates could provide a viable way to proceed. In cases where there is additional information, informed decisions can be made to eliminate early implementations that are projected to perform less well, thus pruning the previously described tree, Figure 1.2. While this approach can reduce the size of the potential outcome space it does not routinely identify a single architecture as being the best to select.

#### 1.6 Performance Analysis Improvement Strategy

This work focuses on those systems whose development success is closely tied to meeting performance expectations. The ability to make a good architecture-selection decision is critical to achieving that outcome. Moving performance analysis earlier in the development process requires these performance uncertainties to be managed in a structured manner. This effort proposes a methodology for making architecture-selection decisions in a way that should reduce overall system development costs by reducing architecture-selection-risk. It is the early characterization of the system's performance that is the focus of this research effort. Since there are many uncertainties associated with the development, having a structured process to manage these uncertainties would be beneficial.

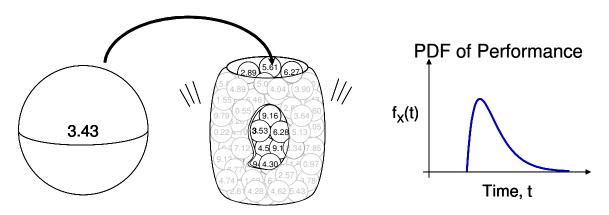

At architecture-design time there is no way to determine what the actual implementation will be. There is also no way to tell how well the actual

implementation will perform. Hence, a probabilistic approach is appropriate. The assertion made here is that the performance of the "to be" instantiated system can be viewed as a random variable which is characterized by a performance probability density function (pdf). This random variable can be thought of as the rule for mapping an event (architecture selected) to a number (the actual performance of system built constrained by the architecture selected). This probabilistic approach allows development planners to include not only design performance uncertainties, but uncertainties associated with the teams performing activities and the processes used to create and implement the designs. Taking this approach, the performance-concerned developer can reduce the risk of selecting an architecture which can not meet the desired performance specifications by assessing the probability that a typical implementation of one particular architecture will perform better than a typical implementation of another.

#### 1.7 Work Focus

This work concentrates on performance-centric development process improvements and focuses on how to improve the architecture-selection process as this will reduce costs associated with fixing performance problems that pop up later in the development that result from poor architecture selection. Any method proposed to replace existing performance evaluation techniques must have attributes that make it better than current practice. Based on a review of related

work as discussed in chapter two, the most important attributes can be enumerated in four categories.

#### 1) Earliness in the design process

Executing performance analysis earlier in the development process is considered beneficial as it reduces performance-failure risk, and can thereby reduce costs. Substantial work has already been done on evaluating designs (and hence indirectly architectures) late in the development process when code has already been delivered. Much less work has been done for the design phase and still less addresses analysis at architecture design time.

The method proposed here addresses performance-goal-achievement by managing uncertainty directly. The approach can be applied early in the development when there is less detailed information available. As the final design matures some of this uncertainty will be eliminated, while other uncertainties like system load may remain (usage of the system may change over time). As the design evolves from architectural design through detailed design, the characteristics of components and connections will be resolved and the system performance uncertainty will be reduced.

#### 2) Accommodation of all available data

The methodology developed should be able to accommodate both actual performance values and performance estimates for cases where true values are unknown. Estimates are most useful before decisions have been made about the precise performance of platforms, communications paths, algorithms, etc. The process should manage both the estimated values and the value uncertainties to ensure that final performance comparisons depict meaningful performance differences. It should be sufficient to use relative performance estimates for alternatives' performance descriptions, since there can be a large number of potentially good solutions to be evaluated.

## 3) Repeatability

The process must be repeatable. The results obtained should not depend on the skills of the analyst. The results should be consistent for different executions using a particular dataset. It must produce predictable and understandable results.

## 4) Practicality

In complex systems, there are a large number of decisions that need to be made.

As each decision is made, the uncertainty in system performance is reduced.

The decision making process employed must avoid introducing exhaustive statespace searches which are often not feasible [AABI00] when large numbers of options must be considered. As well, the method adopted should be practical and useful to a broad set of analysts.

## 1.8 Research Strategy

State-of-the-art methods used for performance management might be referred to as "continuously optimistic." One follows good design guidelines in generating the solution and then checks to see how well that design performs once implemented. For software intensive systems, performance shortcomings are handled through redesign or recode and re-measurement efforts. For the broader system design problem, reconfiguration of elements and modification to the data-flow topology can provide improvements. The method developed in this research takes an "estimate before build" approach. It is patterned on the INCOSE [ICSE07] and Department of Defense Systems Engineering processes [DODI08] but modifies certain activities to account for the estimation and management of uncertainties throughout the development. While performance budgeting can be done either top-down or bottom-up, the method developed as part of this research uses the bottom-up approach since those mathematical tools are more tractable.

Conceptually the process is simple. In all of these approaches, top level system requirements are defined and then the budgets for critical quantities are allocated to subsystems. In a weapons system development, the quantities budgeted might include system weight, power, heat dissipation, etc. In the method described in this research, it is delay that is allocated across the architectural components and connections of each of the alternative solutions. This allocation is done in a hierarchical manner. At any particular level these components may in turn be composed of sub-elements. When that is the case, performance budgets are again sub-allocated to these smaller elements. This process continues until all elements have been assigned a performance allocation. After each allocation, the provided techniques are used to combine assigned budgets along with their uncertainties to ensure end-to-end or total system performance meets the goal. At the lowest level, individual components are built or selected to meet these derived performance budgets. There are two difficulties: 1) there is more than one way to split up a performance budget across a set of elements, and 2) in many developments, some components may already exist, and the performance of the top-down approach needs to end up with a budgeted value that matches the performance values of those existing components when the analysis is complete.

An alternative approach using the same tools is possible. The performance of the lowest elements in the architecture design can be characterized and the performance of the overall system built up incrementally from such descriptions. When performance is estimated this way, one does not know in advance whether that the requested system requirements will be met.

Both of these sets of problems can be solved by redefining the problem to be one based on anticipating performance differences between architecture options. My research extends current performance evaluation methods and concepts by considering the uncertainties in performance estimates of components and connections and provides methods of combining these uncertainty values into an overall, end-to-end estimate of system performance in a relative way so that comparisons can be made between alternatives.

The management of uncertainties when done as proposed can further assist the developer in analyzing implementation costs (work that is outside the scope of this effort). The Bayes Criteria [MeCo78] describes how to combine alternative cost with the probabilities of selecting those alternatives. A Bayes approach could leverage the probabilistic descriptions developed here and provide a basis for future work directed at further reducing the cost of system developments by balancing performance risk against cost.

#### 1.9 Definitions

There are multiple definitions of architecture and performance in common use as related to analysis in this field. These terms as used for this research are defined next.

Architecture. A system architecture is classically defined as the enumerated set of entities (that perform system functions), how they are connected, and how they evolve with time [DODA97]. It routinely contains at a minimum, identification of the components or large-grain pieces of the system, as well as descriptions of the connections between those pieces. The quality of an architecture is directly related to its ability to constrain eventual implementation options to ones that are likely to meet both the desired quality goals and the functional requirements. Architectures are intended to maximize the flexibility of developers to make lower level design decisions while ensuring that these developers can meet system quality and functional requirements. This view is consistent with many others like [FrBo98] [UcYa00] which identify components, connectors, and ports as key features.

Performance. Performance is defined to be the number of events of interest that occur per unit of time. It is either the rate at which a set of activities is completed, or the time required to complete a specific activity. This intentionally broad definition allows us to qualify the performance of a system differently depending

on the types of information that may be available to characterize the system elements and the related uncertainties associated with activity performance descriptions.

Since much of this work focuses on probabilistic results and the manipulation of functions of random variables, the following definitions are provided. While these terms have other meanings in the computer science field, they are used in the following context with these definitions.

Experiment. An experiment is an activity that produces an identifiable outcome. Common experiments include the roll of a die, the toss of a dart, etc. In this context, the experiment is routinely the selection of an architecture. The associated result or outcome is the performance value that this selected architecture will have based on an input selected from the feasible system inputs. For this work, the experiment or the space of all outcomes is the closed interval of the real line [0, X], where X is some large rational number.

Event. An event is a collection of outcomes to which we can assign probabilities. The set of events constitutes a mathematical field. In the context of this work, all "sensible" outcomes will qualify as events [Papo65]. There exist several technical restrictions on what can be an event. These restrictions are not listed here since for architecture selection purposes they are not important.

## 1.10 Research Approach

This dissertation provides a method for improving the system development process by identifying a technique for making quantitative comparative performance assessments of alternative system architectures early in the development life cycle.

The problem statement for this effort is:

There are many methods that can be used to evaluate system performance. Most are applied to systems that are either at least partially implemented or where detailed component and connector performance information has been clearly defined. Approaches based on queuing simulations produce precise results where the detailed design factors are known. When design parameter values are not clearly established however, a queuing approach usually has to resort to checking combinations of sets of possible values. This assures that existing uncertainty can be reflected in the end-to-end performance estimates which will vary depending on the outcomes future design decisions. Examining large numbers of cases takes time. There aren't generally accepted techniques that can directly manage the performance uncertainty that exists at architecture selection time. Statistical techniques exist that could be used to reduce the

number of solution options to be analyzed and as such should reduce the time required for analysis before the architecture selection is made.

The thesis statement for this research is:

Consider a set of proposed system architecture options (architectural designs) and a probabilistic description of the performance of the architectural elements that make up those designs. For each ordered pair of architectural options in that set, one can calculate an estimate of the probability that the first option will perform better than the second option should both options be implemented.

In executing this research, the following activities were conducted:

- Five fundamental functions were identified for use in architecture performance modeling.

- Algorithms were implemented to evaluate each of these five functions for quasi-arbitrary descriptions of performance uncertainties.

- A method was developed to generate a probabilistic description of the performance of an architecture based on combining the descriptions of the constituent elements using the five functions.

- A method was derived to compute the probability that one particular architectural description will produce an implementation which will perform better than a similar implementation of an alternative architecture.

- The method was applied to a small but realistic three-tier information management example problem.

- The method was applied to two more complex architecture examples to demonstrate the analysis required to identify and characterize architecture component and connection uncertainties.

- Discrete element simulations were run on connection and processing elements. These simulations established that one can estimate an element's mean performance consistent with theory. It further established that one can estimate the element performance uncertainty around the mean. This second descriptive characterization is not routinely available through analytic-closed-form efforts.

## 1.11 Assumptions

The analysis process is based on a number of assumptions:

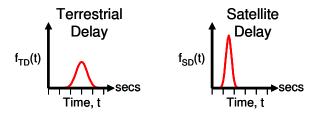

- Components component performance does not vary over time, and the conversion of data from input to output can be characterized by a single probability density function.

- 2) Connectors the delay of connectors is approximated by the quotient of the probability density function for the size of transmitted elements divided by the probabilistic description of the link data rate.

- 3) Contention for resources can be simulated by subtracting resources used by other tasks (both computational and transmission) from those available for the task under analysis.

- 4) Congestion/bottlenecks . When network congestion or bottlenecks can be anticipated, they are included in the low level performance descriptions of the connectors. When they are not or cannot be anticipated, they will not be reflected in the performance characterizations.

## 1.12 Organization

Chapter one presented the context of the problem and reason for addressing this research goal as well as the research approach. Chapter two surveys related work in this area. Chapter three considers the architecture selection problem as a type of probabilistic experiment. Uncertainties to be expected are identified and the underlying performance design problem is characterized. Chapter four assumes that the uncertainties of the architecture selection process can be characterized as a probability density function. It then explains how to compare architecture alternatives in terms of their likelihood of performing better than other alternatives. Chapter five explains how to combine the probability density functions (pdfs) describing the performance of subsystems into a probability density function which describes the performance of the entire architecture alternative. Chapter six uses a classic three tier database problem as an example of the techniques described in chapters four and five. Chapter seven takes two more realistic problems and applies the described techniques to identify which of several alternative architectures perform better. Chapter eight describes the CAPE tool built as part of this research. Chapter 9 describes the validation methods used and a preliminary error bound for the architecture comparison metric. Chapter ten identifies the research contributions and future research directions.

#### Chapter 2

#### **Related Work**

This system performance research effort is largely built upon established results in four areas: foundational work in software architecture, architecture description languages, performance evaluation requirements and performance evaluation analysis. Much of the work discussed here provided the rationale for the approach taken in this research effort. Other portions of the work discussed are indicative of the amount of active research ongoing with regard to performance evaluation (much of it architecture related) as well as suggesting that the approach documented here has not already been attempted.

#### 2.1 Software Architecture Foundational Work

A 1992 paper written by Perry and Wolf [PeWo92] began the study of software architectures as a significant factor in creating quality software. This paper addressed the elements, form and rationale for using a particular structure to develop a software capability. This is the start of the association of quality attributes (performance) with architectural elements. In the mid-1990s, papers on the topic were published in numbers. The theme of these papers was that software projects have architectures, either generated intentionally or evolved

from the detailed system design, and that architectures can be categorized into a relatively small number of styles [BaCK98]. Some researchers formalized the description of those architectural styles [AlGa94] [GaPZ94]. These styles provide a categorization scheme for identifying useful elements when considering performance contributions. Shortly thereafter Garlan and Shaw published a seminal work [GaSh96] which began to enumerate software architectural styles and the quality attributes of those styles. The identification or classification of architecture styles is important because it provides a fundamental way to look at the elements of a software system and hence points to the fundamental entities that must be considered when performance is an important consideration. Substantial analysis continues as investigators study the relationship between architectural styles and software quality. Much of the work that followed focused on Architecture Description Languages in an attempt to make the definition and manipulation of architectures more precise.

## 2.2 Architecture Description Languages

Precise descriptions of architectures, or perhaps more accurately the fact that architectural descriptions are currently not precise with respect to performance concerns, is critical to establishing an appropriate method for analysis. Efforts were made to increase the precision of the architectural descriptions. The concept of an Architectural Description Language (ADL) was developed to provide a basis for capturing the essential elements and relationships between

those elements in formal languages to express software architectural concepts and structures. The role of the ADL is to express the software structure in a notation appropriate for manipulation by supporting tools. These languages focus on the large-scale or high-level design and provide developers and designers with an analysis-appropriate description of the system under study. Their value rests in their ability to clearly define relationships between entities and to provide a common understanding among readers of the underlying "structure" of the concept to be presented. The languages make it possible to explore the functional properties of architectures and provide a means to concisely define the characteristics of system elements in a precise and expressive manner.

There are a number of ADLs, each focusing on a slightly different aspect of overarching architectural concerns. A survey of architectural description languages is covered in [Clem96]. Some of the more well-known languages include: ACME [GaMW97], Aesop [GaAO94] [Garl95], C2 [MORT96], Gestalt, LILEANNA [Trac93], MetaH [Vest96], SADL [MoRi97], UniCon [SDK+95], Weaves [GoRa91], Regis [MaDK94], Rapide [LKA+95] [LuVe95], Darwin [Darw94], and Wright [GaSh96] [Alle97]. Some, like Rapide, are executable, while most are not. Nearly all include analysis capabilities addressing specific architectural concerns. None of these ADLs specifically addresses performance issues, although each reference gives insight into places where performance

related information could be inserted into a specification so that they would be more useful in studying performance issues.

## 2.3 System Performance Evaluation

The earliest work on performance associated with software architectures focused on the large grain issues relating to interoperability, the matching of interfaces and the extent to which systems composed of parts could function properly. A paper by Garlan, Allen and Ockerbloom [GaAO95] is characteristic and addresses the impact of architectural considerations on system performance in a fundamental way. Their analysis focuses on the types of mismatches that can occur between components and connectors and how these mismatches can remain undiscovered until well into the development life cycle. Their technique concentrates on identifying problems, (i.e., assumptions about component characteristics, connectors, and the global architectural structure) before they become part of the design. The authors discuss methods to avoid making improper assumptions about these architectural elements. They provide insight into early interface indicators that may warn of failure when the elements are assembled. Unfortunately, the paper does not address a specific methodology for correcting these types of deficiencies. There are many other papers of this type. They generally avoid addressing performance in terms of metrics or in a numerically quantifiable way. Some efforts continue to analyze potential interface mismatches and other model checking techniques in work done by Campos and Merseguer [CaMe06].

In 2004, Balsamo et. al. summarized the state of performance work in published approaches focusing on three evaluation factors: earliness of integration, model used for performance estimation and the amount of automation available. Performance work had progressed from identifying failures to the actual prediction of performance indices such as response time, throughput and utilization. For my research, the first two are of most interest. The paper [BaMI04] exposes the principal research techniques, and suggests that the benefits of probabilistic analysis show promise. The survey divides the work into models and evaluation methods. The models fell largely into four categories: queuing networks, stochastic Petri nets, stochastic process algebra, and simulation models. Evaluation methods were divided into analytical techniques and simulation.

## 2.3.1 Queuing Networks

Queuing networks characterize the proposed solution of a number of researchers in this area. In early work, CHAM (CHemical Abstract Machine) [BalM98] [ColW99] employs an N-layer Queuing Network Model and was used to estimate performance based on a network automatically derived from an architecture description language. The ATLAS Transformation Language can be used to

automatically map UML models into queuing networks [CoGM08]. With the growing acceptance of UML, recent efforts started to focus on the mapping of Message Sequence Chart descriptions of architectures to queuing networks [AABI00]. This work is one of the reasons for suggesting that UML sequence diagrams could be effective in a probabilistic analysis. Similarly, UML diagrams were automatically and consistently translated into queuing-network-based performance models in [CoMi00] and [Ambr05]. [BaMa05] started with annotated UML use cases, activity and deployment diagrams to create performance models based on multi-chain and multi-class Queuing Networks (QN) annotated according to the UML Profile for Schedulability, Performance and Time Specification. Other attempts have been made to use this specification to construct models to make quantitative predictions regarding performance characteristics. These efforts demonstrated generating Layered Queuing Network (LQN) performance models based on a graph-grammar and a UML model annotated with performance information [PeSh02]. An XSLT approach to transform UML artifacts into LQNs is described in [GuPe02]. Some have attempted to move the evaluation of performance even earlier than architectureselection time back to scenario definition time. This is the case with the Scenario to Performance (S2P) algorithm described in [PeWo05] which transforms scenario models automatically into performance models and uses the LQNGenerator tool to build layered queuing network performance models.

#### 2.3.2 Petri Nets

Petri nets come in a number of forms and can be used for modeling and evaluating software architecture performance. Colored Petri Nets are used in [XuKu98] to model a mobile-phone-family execution architecture characterize both the time and space performance of a large software intensive Interval Time Petri Nets (Petri Nets that have random firing time system. intervals) are used for a similar purpose in [NaBG09]. PEPA nets, a type of colored stochastic Petri nets, are used with stochastic process algebras to derive steady state performance measures in [GHKR04] and in [CGHT99]. As part of a larger security analysis effort, Generalized Stochastic Petri Nets (GSPNs) are used in [CoTr08] to inform on the performance impacts of security related architectural decisions. Additionally, [Cort05] discusses the need for performance anthologies based on evidence from operational profiles (annotating performance parameters onto software models) and their translation into Stochastic Petri Nets to quantify performance. Several UML diagram types provide information for the Software Performance Engineering process which is capable of generating GSPNs as described in [LoMC04]. Similarly state charts and sequence diagrams provide the input to automatically generated GSPNs in [BeDM02]. Analysis using GSPNs to generate worst and best case system performance is discussed in [NaBG09].

#### 2.3.3 Stochastic Process Algebras

Stochastic process algebras provide another strategy for addressing the performance estimation task. In [LTK+02], UML diagrams provide information to characterize a generalized semi-Markov process used to do performance analysis. They are also used in TIPPtool [HHK+00] to address compositional performance modeling. The architecture description language AEMPA characterizes the syntax and semantics of architecture descriptions in [BeCD00] and is used for performance analysis.

#### 2.3.4 Simulation Models

Simulation models are the basis of a number of different approaches that do not fit neatly into the above categories. Initially mean-value-analysis was used in performance modeling of combined computer-communication systems. Later, simulations were used to generate performance intervals which better characterized systems than these single mean value numbers [LuHa98]. A simulation environment called Arena has been used with UML data to simulate performance in a meta-modeling environment [TKMG08]. In [SaJP05] the simulation output is used to inform where improvements can be made in the architecture. [BeKR07] addresses a method to parameterize architectural features using the Palladio Component Model, a domain specific modeling language, to gain insight into performance. Activity diagrams are simulated to characterize performance with both exponentially distributed and deterministic

delays in [LTK+02]. Indicative of efforts considering hardware parameters before design and relating them to performance expectations is [Alsa04a] where disk and CPU delays drive architectural analysis. New UML stereotypes are introduced in [AmCl01] where use case, activity and deployment diagrams representing performance, complete the architecture performance description. An algorithm for deriving a simulation model from an annotated UML software architecture is explained in [BaMa03]. Sequence diagrams and state charts are used to represent execution paths in [BeDM02] where performance estimates are derived.

#### 2.3.5 Combined Models

Combining models is common as well. [BaBS02] uses Stochastic Process Algebras and Queuing Networks to leverage formal techniques and verify functional properties. A component-based predictive analysis built on stochastic process algebras and simulation forms a system called NICE that addresses communications performance concerns [BMMI04].

# 2.3.6 Component-based Architectures

Component-based architectures are often handled a bit differently. With components, the estimation problem may be simpler particularly if there is some experimental information available. A specification might already exist for estimating performance even before components have been built. This need to

determine or estimate the performance of elements is consistent with the information needs of this research's proposed approach. Establishment of a set of scenarios based on Use Cases to enumerate the sequence of tasks or component responsibilities to be performed by the system is covered in [PIFa02]. Once element characteristics are established, the challenge shifts to one of combining results to describe a complete system estimate [GrMi04]. Performance estimation with components can be difficult since systems already built on component technology [CLGL05] have existing interfaces. When these interfaces do not match parts of the business process, performance degradations often result. Components routinely have interfaces that reflect their underlying function; changes in processes will cause changes in component coordination and performance. How to manage the expected estimate changes that crop up from a substitution of elements is described in [AaHT02]. The importance of workload characteristics and service demand is discussed using an XML Component-Based Modeling Language in the analysis presented in [WuXi04]. Executable models are described in [WHKT08] where the authors identify a set of architectures with a component-based modeling language called COLA. Component based design benchmarking and profiling are explained in [CLGL05] which includes case studies in CORBA and J2EE. Combining RT-UML and CB-SPE (an automated approach for composing elements that addresses performance engineering) [BeMi04], provides insight into methods for parameterizing performance as well as combining elements. COTS-Aware

Requirements Engineering and Software Architecting, (CARE/SA) [ChCo05] is introduced as a method to iteratively match, rank, and select COTS components and subsequently aggregate their functional and non-functional performance into an architecture. Other informative but more generic approaches are included in [BFG+04] and [CoTr08] which address using patterns in a building block approach to give insight into architecture performance.

Once a model has been established, there remains the need to populate that model with information tailoring it to the specific architecture being evaluated. A number of contributions can assist in this process. Model information exchange formats have been designed to facilitate both the flexibility of bringing different models together, as well as helping to define the minimal set of characterizing parameters that are needed. A useful exchange schema is discussed in [MoSW08] and descriptions of XML interchange formats are discussed in [SLC+05]. These approaches suggest that, in the future, performance evaluation tools may be combined in a plug-and-play manner. Others have extended architecture description languages to include the ability to maintain performance A review of different notations or languages useful for representing performance characteristics exists in [CoMI03]. A number of UML extensions have been proposed: Performance Aware Software Development (PASD) includes information on resource demand budgets. Others use UML 2.0 sequence diagrams and the newer structured control constructs, like

CombinedFragments (an expression for sets of interaction fragments), express concurrency [ShVN08] or use the composite structure diagram [PSG+09]. State charts are refined in [LoMC04] and UML 2.0 versions of activity diagrams are demonstrated in [CGH+04]. Service composition processes are described using Business Process Execution Language for Web Services in [AmBo07].

#### 2.3.7 Architecture Design Domain Specific Considerations