#### NOVEL MOLECULAR MEMORY ON SI AND TWO-DIMENSIONAL MATERIALS

by

Kai Jiang A Dissertation Submitted to the Graduate Faculty

Of

George Mason University in Partial Fulfillment of The Requirements for the Degree

Of

Doctor of Philosophy Electrical and Computer Engineering

| Committee: |                                            |

|------------|--------------------------------------------|

|            | Dr. Qiliang Li, Dissertation Director      |

|            | Dr. Dimitris E. Ioannou, Committee         |

|            | Member                                     |

|            | Dr. Rao V. Mulpuri, Committee Member       |

|            | Dr. Sujitra J. Pookpanratana, Committee    |

|            | Member                                     |

|            | Dr. Patrick Vora, Committee Member         |

|            | Dr. Monson H. Hayes, Department Chair      |

|            | Dr. Kenneth S. Ball, Dean, Volgenau School |

|            | of Engineering                             |

| Date:      | Spring Semester 2019                       |

|            | George Mason University                    |

|            | Fairfax, VA                                |

#### Novel Molecular Memory on Si and Two-Dimensional Materials

A Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

by

Kai Jiang Master of Materials Science Nanjing University, 2015 Bachelor of Materials Science Central South University, 2012

Director: Qiliang Li, Professor Department of Electrical and Computer Engineering

> Spring Semester 2019 George Mason University Fairfax, VA

Copyright 2019 Kai Jiang All Rights Reserved

#### Acknowledgement

First of all, I would like to thank my research advisor, Prof. Qiliang Li, for his guidance and support during my graduate studies at George Mason University. His solid background in semiconductor device physics and open-minded research vision have a great impact on me. I sincerely appreciate the time and support that Prof. Li has committed to the achievement of this work.

I very much appreciate Dr. Sujitra J. Pookpanratana and Dr. Curt A. Richter for their helpful advice and great support during the whole period of my research at NIST. This work would not have been possible without their generous mentoring.

My special thanks to Prof. Dimitris E. Ioannou, Prof. Rao V. Mulpuri and Prof. Patrick Vora for the valuable knowledge I learned from them during the graduate studies, and for accepting to be part of my doctoral committee.

I would like to extend my thanks to my colleagues in NIST and GMU, Dr. Christina Hacker, Dr Siyuan Zhang, Dr. Lin You, Oleg Kirillov, Dr. Son Le, Dr Brent. A Sperling, Sheng Yu, Kwesi Eshun, Chen Shi, Zhenyi Ye for their help, support and friendship.

Finally, I wish to express my deepest thanks to my family, for their love, patience and life-time support.

## **Table of Contents**

|                                                                           | Page |

|---------------------------------------------------------------------------|------|

| List of Tables                                                            | vi   |

| List of Figures                                                           | vii  |

| Abstract                                                                  | vii  |

| Chapter 1 Introduction                                                    | 1    |

| 1.1 The development of CMOS scaling and Impact on Memory                  | 1    |

| 1.2 Flash memory technology                                               | 4    |

| 1.3 Beyond the floating gate structure                                    | 8    |

| 1.4 Overview of dissertation                                              | 14   |

| Chapter 2 Fabrication, Operation and Characterization of Molecular Memory | 16   |

| 2.1 Introduction                                                          | 16   |

| 2.2 Recent development of molecular memory                                | 17   |

| 2.3 Fabrication of Si based redox-active molecular flash memory           | 26   |

| 2.4 Fabrication of 2-D material based molecular memory                    | 30   |

| 2.4 Physical and electrical characterization                              | 32   |

| Chapter 3 Redox-active Molecular Memory Based on Si                       | 34   |

| 3.1 Introduction                                                          |      |

| 3.2 Experimental details                                                  | 36   |

| 3.3 Physical and electrical measurement for molecule attachment           | 40   |

| 3.4 Molecular memory characterization                                     |      |

| 3.5 Summary                                                               | 52   |

| Chapter 4 Process Variation Control                                       | 53   |

| 4.1 molecular attachment control                                          | 53   |

| 4.2 Dielectric layer control                                              | 54   |

| Chapter 5 Redox-Active Molecular Memory on Two-Dimensional Materials      | 57   |

| 5.1 Introduction                                                          | 57   |

| 5.2 Experiment details                                                    | 61   |

| 5.3 Exfoliated MoS <sub>2</sub> and molecule attachment characterization  |      |

| 5.4 Characterization of molecular memory on monolayer MoS <sub>2</sub>    | 68   |

| 5.5 Summary                                                               |      |

| Chapter 6 Conclusion and Future Work                                      |      |

| 6.1 Conclusion                                                            |      |

## **List of Tables**

|                          |                                           | page |

|--------------------------|-------------------------------------------|------|

| Table 1. Performance com | parison of different non-volatile memory. | 4    |

## **List of Figures**

|                                                                                                   | Page     |

|---------------------------------------------------------------------------------------------------|----------|

| Figure 1 Illustration of a floating-gate Flash memory cell                                        | 5        |

| Figure 2 NOR and NAND Flash architecture                                                          | 6        |

| Figure 3 Schematic of 3-D flash architecture                                                      | 8        |

| Figure 4 Schematic picture of Strees-induced leakage current (SILC)                               | 9        |

| Figure 5 Schematic plot of a SONOS memory cell                                                    |          |

| Figure 6 Atomic force microscopy image of a nanoscale cross-point molecular switch                | hing     |

| device                                                                                            | 18       |

| Figure 7 structure of a pentacene organic FET                                                     | 20       |

| Figure 8 Schematic of electrolyte-molecule -Si capacitor structure and corresponding              | <b>5</b> |

| equivalent circuit                                                                                | 22       |

| Figure 9 Schematic of α-ferrocenylethanol molecular memory structure and the exce                 | llent    |

| endurance property                                                                                |          |

| Figure 10 Illustration of molecule attachment process                                             | 28       |

| Figure 11 Capacitor memory device fabrication flow                                                |          |

| Figure 12 Illustration of attachment process on MoS <sub>2</sub>                                  | 32       |

| Figure 13 The molecule structure of Redox-active Ru molecule and the aliphatic AUS                | S.37     |

| Figure 14 Schematic of the MAROS capacitor structure                                              | 39       |

| Figure 15 CyV of the EMOS capaciptor at 10mV/s sweep rate                                         | 41       |

| Figure 16 XPS measurement of (left) samples with Ru molecule attached on SiO <sub>2</sub>         |          |

| surface, and(right) sample before "click" reaction.                                               | 42       |

| Figure 17 AFM image of (left)Bare Si, (middle)substrate with AUS and (right)Ru                    |          |

| molecular SAM on Substrate                                                                        |          |

| Figure 18 C-V measurements of memory devices with Ru attached structure                           |          |

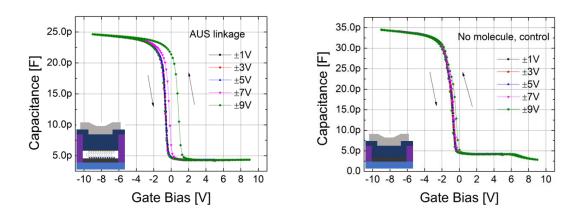

| Figure 19 C-V measurements of memory devices with (left) only AUS linkage and (r                  |          |

| with no molecule                                                                                  |          |

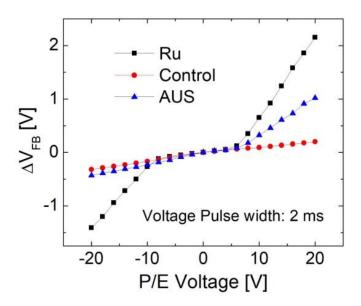

| Figure 20 $\triangle V_{FB}$ of these 3 structures as a function of P/E voltage with pulse width= |          |

|                                                                                                   |          |

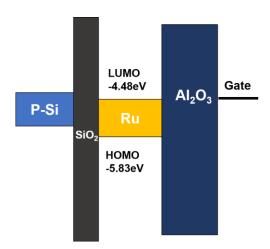

| Figure 21 Schematic band diagram of Ru molecular memory structure                                 |          |

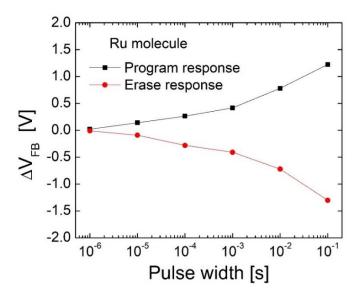

| Figure 22 Response speed characteristic of Ru molecular memory device                             |          |

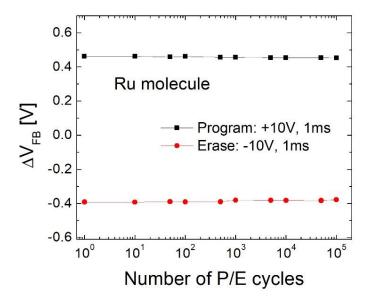

| Figure 23 Endurance characteristics of Ru molecular memory devices under P/E puls                 |          |

| $V_G = \pm 10 \text{ V}$ with 1 ms pulse width                                                    |          |

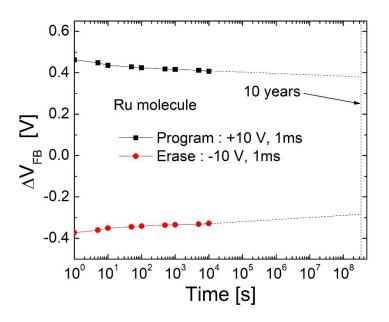

| Figure 24 Retention Characteristic of Ru molecular memory at room temperature                     |          |

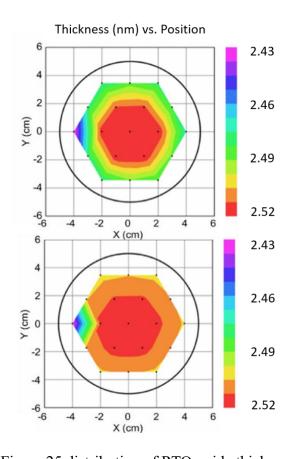

| Figure 25 distribution of RTO oxide thickness                                                     | 55       |

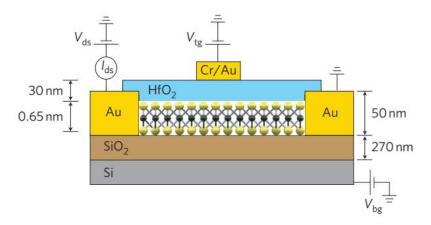

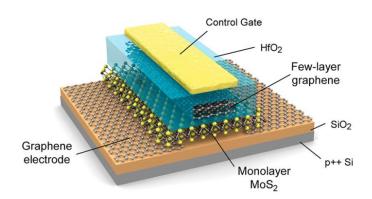

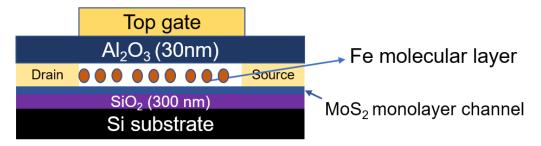

| Figure 26 Schematic view of MoS <sub>2</sub> monolayer transistor                                         | . 58 |

|-----------------------------------------------------------------------------------------------------------|------|

| Figure 27 schematic view of memory device based on monolayer MoS <sub>2</sub>                             | . 59 |

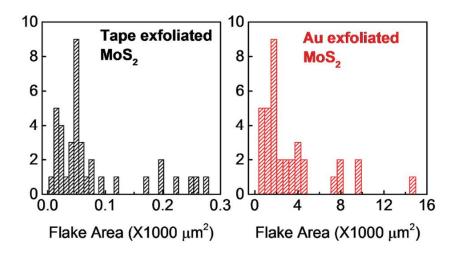

| Figure 28 Histogram of flake areas for tape-exfoliated vs. Au-exfoliated MoS <sub>2</sub>                 | 61   |

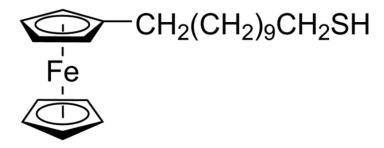

| Figure 29 molecule structure of 11-(Ferrocenyl)undecanethiol                                              | 62   |

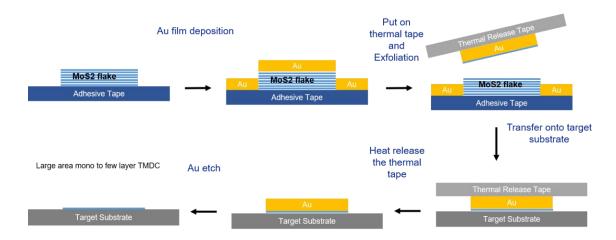

| Figure 30 schematic illustration of the Au exfoliation process                                            | 63   |

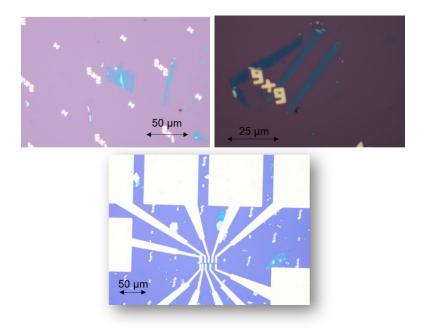

| Figure 31 Optical microscope images of (left) a large monolayer MoS <sub>2</sub> , (right) patterne       | ed   |

| MoS <sub>2</sub> stripe and (bottom)MoS <sub>2</sub> with electrode                                       | 64   |

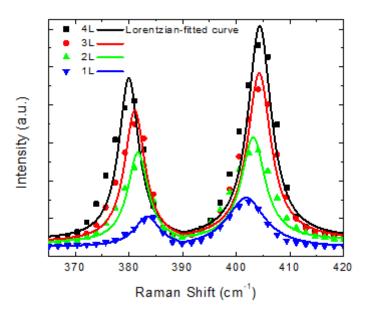

| Figure 32 Raman spectra measurement on MoS <sub>2</sub> samples with different layer number               | . 66 |

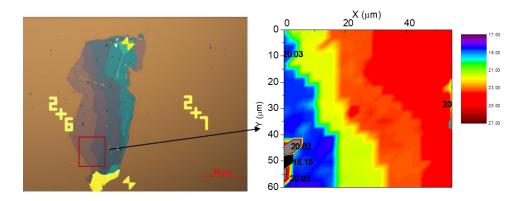

| Figure 33 Microscope image of MoS <sub>2</sub> flake contain different layer number and                   |      |

| corresponding Raman peak mapping, the color reflects the peak position difference                         | 67   |

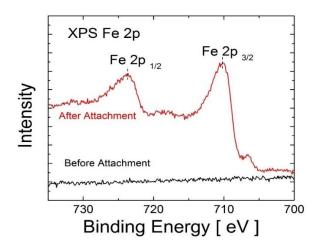

| Figure 34 XPS of the samples with 11-(Ferrocenyl)undecanethiol attached on MoS <sub>2</sub> and           | d    |

| Bare MoS <sub>2</sub> before attachment                                                                   | . 68 |

| Figure 35 schematic of a MoS <sub>2</sub> based Fe molecular memory cell based on monolayer               |      |

| MoS <sub>2</sub> channel                                                                                  | . 69 |

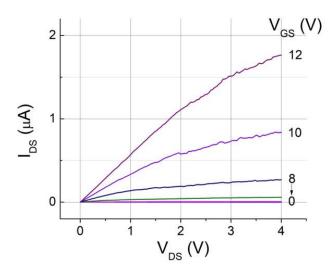

| Figure 36 Output characteristic of MoS <sub>2</sub> based Fe molecular memory with V <sub>GS</sub> varies |      |

| from 0V to 12V, with step of 1V.                                                                          | . 70 |

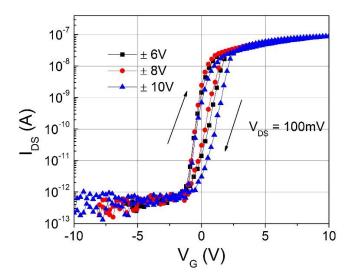

| Figure 37 Transfer characteristics of $MoS_2$ based Fe molecular memory with $V_{DS} = 100$               | )    |

| mV                                                                                                        | . 70 |

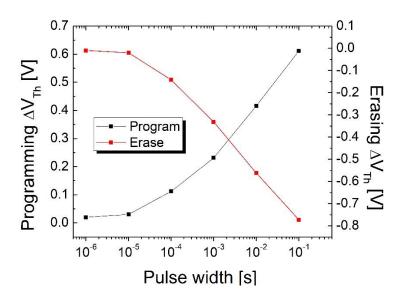

| Figure 38 P/E switch characterization of MoS <sub>2</sub> based Fe molecular memory                       | . 71 |

| Figure 39 Retention characterization of MoS <sub>2</sub> based Fe molecular memory                        | . 73 |

| Figure 40 Endurance property of MoS <sub>2</sub> based Fe molecular memory                                | . 74 |

**Abstract**

NOVEL MOLECULAR MEMORY ON SI AND TWO-DIMENSIONAL MATERIALS

Kai Jiang, Ph.D.

George Mason University, 2019

Dissertation Director: Dr. Qiliang Li

The dimensional scaling down of microelectronics to further increase the storage ability

and density is confronting the fundamental and physical limit. The performance of high

density, low power consumption non-volatile memory as the important part in portable

electronic devices like cellphone, tablet and laptop will have a drastic impact on these

devices. Molecular electronic technology has attracted much attention due to its nanoscale

features, flexibly tunable properties and tremendous application prospects, etc. Replacing

the currently used traditional flash memory with high-performance Flash-based molecular

non-volatile memory for further scaling down, will be an effective method for increasing

storage density and stability.

In this study, we introduce the development of molecular electronics in the application of

non-volatile memory. Recently, solid-state non-volatile memory devices based on redox-

active molecules have been reported, exhibiting fast speed, low operation voltage,

excellent endurance and multi-bit storage, outperforming the conventional floating-gate flash memory. I have fabricated and characterized a kind of Flash-like Ru molecular memory devices. This Ru molecular exhibit excellent memory window under high-frequency CV measurement. The programming and erasing response speed are also suitable for Flash memory applications. The stability of our molecular memory devices is demonstrated by endurance characterization for more than 10<sup>5</sup> cycles. The charge storage in these molecular memory devices is basically derived from the intrinsic redox processes lead by a sweeping gate voltage bias. Compare with the traditional flash memory, the intrinsic redox and the stable molecular properties lead to a very reliable and high-density charge storage ability.

Two-dimensional materials, especially layered transition metal dichalcogenides (TMDCs), such as molybdenum disulfide (MoS2) and tungsten diselenide (WSe2) have recently become superstar materials as nanomaterials for future flexible, portable and high-performance electronic devices due to their excellent physical, electrical and mechanical properties. We have developed approaches of redox-active molecule attachment on 2-dimensional materials. Redox-active molecular memory based on 2-dimensional materials have been fabricated and measured. Our finding about redox-active molecule provides many opportunities for novel non-volatile memory applications.

#### **Chapter 1 Introduction**

#### 1.1 The development of CMOS scaling and Impact on Memory

The scaling of Metal-Oxide-Semiconductor field-effect transistor (MOSFET) will continues with the new emerging technologies to extend Complementary Metal-Oxide-Semiconductor (CMOS) beyond 22-nm technology node have been proposed by the 2013 International Technology Roadmap for Semic. onductors (ITRS) [1]. However, the conventional path of scaling planar CMOS will face significant challenges set by performance and power consumption requirements. Dennard et al. set forth the trend of CMOS scaling has deviated from the prediction of Moore and the scaling rules due to technical and physical limitation in recent years [2, 3]. System scaling enabled by Moore's scaling is more and more challenged with the scarcity of resources such as power and interconnect bandwidth. Particularly due to the development of cloud, seamless interaction of big-data and instant data have become a necessity [4]. 5-nm node where the lithography scale approaches a few times of atom diameter will probably be the stop point of future CMOS scaling [5-7]. Scaling limitation of thin gate oxide, channel length modulation and system series resistance have become a growing concern about maintaining density, speed, reliability and power dissipation despite the introduction of high-k materials.

Different approaches toward CMOS scaling challenge has been proposed and reported. For example, process based on silicon-on-insulator (SOI) structure, 3-D FET structure and

SiGe BiCMOS technology are considered as effective method to avoid the doping, carrier transportation and series resistance scaling. [8-12]

High-performance, low energy cost and reliable systems built on CMOS architecture are still pursuing driven by development of big-data and instant data [13]. Despite the slow down of CMOS logic device scaling, semiconductor industry growth explosively in this decade. The richness of proposed new materials and novel structures provide opportunities for future semiconductor device applications. DNA methodology, single electron devices, molecular electronics and quantum computing are considered as promising new technologies which receive more and more attention both in industrial and academic research.

Memory device is an essential component in many of these electronic devices for data processing, storage, and communication. With the development of IT technology, Huge market demand has been created for high performance semiconductor devices for future applications in memory and emerging portable/wearable electronic devices. Solid-state mass storage occupies a growth portion of memory market, due to its compatibility with CMOS process technology, non-volatile keep the data without power supply and reliability in harsh environment without mechanical parts. Typically, non-volatile memory including these types of memory: ferroelectric random-access memory (FeRAM), Magnetic random-access memory (MRAM), resistive random-access memory (RRAM), phase-change random-access memory (PCRAM), and Flash memory [14-17]. They have been well developed and investigated during these decades.

Non-volatile memory is typically applied for the long-term storage task. Which

usually does not need extremely fast Program/Erase (P/E) speed or integration density. the non-volatile market is expected to gain momentum due to explosive development of portable, smart device and big-data centers. A variant of charge storage memory referred to as Flash memory is widely used in consumer electronic products such as cell phones and music players while NAND Flash-based solid-state disks (SSDs) are increasingly displacing hard disk drives as the primary storage device in laptops, desktops, and even data centers [18]. The industry is expected to gain momentum owing to increasing demand for high scalable, fast and economical memory solutions. With increasing data there is an increasing need to manage and store the data and information for future references. The growing demand for mass storage and universal storage devices is expected to favor market growth over the forecast period. High designing cost and stability in extreme environmental conditions is expected to hinder the growth over the next decades.

Emerging nonvolatile memory technologies such as magnetic random-access memory (MRAM), ferroelectric random-access memory (FeRAM), phase-change memory (PCRAM), resistive random-access memory (RRAM), and molecular flash-like memory, combine the speed of static random-access memory (SRAM), the density of dynamic random-access memory (DRAM), and the non-volatility of Flash memory and so become very attractive as another possibility for future memory architecture. Table 1.1 compares different mainstream non-volatile memory performance.

Table 1. Performance comparison of different non-volatile memory

|                 | NAND<br>Flash | PCRAM    | FERAM     | MRAM      | RRAM     |

|-----------------|---------------|----------|-----------|-----------|----------|

| Structure       | 1T            | 1T1R     | 1T1C      | 1T1R      | 1T1R     |

| Program voltage | >10V          | <3V      | 1~3V      | ~2V       | 1V       |

| Read voltage    | 2V            | 2V       | ~3V       | 1.5V      | 0.5V     |

| Speed           | ms            | ns       | ns        | ns        | ns       |

| Retention       | 10 years      | 10 years | 10 years  | 10 years  | 10 years |

| Endurance       | $10^{5}$      | $10^{9}$ | $10^{12}$ | $10^{14}$ | $10^{5}$ |

From Table 1, we can find out that each of them has drawbacks and the best candidate for next-generation non-volatile memory technology is undetermined. As such, scientist and engineers have been devoting effort on emerging technologies aiming to go beyond physical limitations and potentially replace all or most of the existing semiconductor memory technologies [19-20].

#### 1.2 Flash memory technology

All through the non-volatile memory candidates for primary storage, Flash memory is the most widely investigated and commercialized non-volatile memory. Flash memory market size is more than 30 billion dollars in fy2016 as a major part of total memory revenue [21]. Flash memory is a very successful industrial product due to its fast read times, good reliability and compatibility with CMOS process technology [22-23].

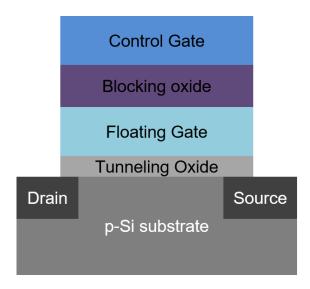

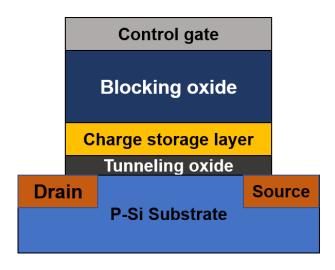

Figure 1 Illustration of a floating-gate Flash memory cell

Figure 1.1 shows the structure of a Flash memory cell. Also known as the floating gate memory, a Flash memory cell is composited by intercalate a floating gate inside the MOSFET gate oxide. The storage method of a Flash memory is trapping and de-trapping electrons in the floating gate, which is sandwiched by a relatively thick blocking oxide layer and a thin tunneling oxide, respectively. As the isolation by two nearby dielectric oxide, the stored electrons can remain for a long period. Flash memory was supposed to replace the Electrically erasable and programmable read-only memory (EEPROM) rapidly in every application at the end of 1980s. There are two main memory architecture of flash memory – NOR flash memory and NAND flash memory based on the way that the memory cells are organized. Two type memory architectures are illustrated in Figure 1.2.

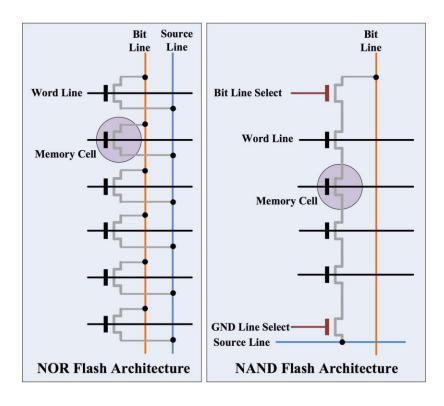

Figure 2 NOR and NAND Flash architecture

Toshiba developed flash memory from EEPROM in the early 1980s and commercialized flash memory in 1984. First NAND flash memory technology was presented by Toshiba at IEEE international Electron Devices Meeting (IEDM) in 1987 and Intel introduced the first commercial NOR flash chip in 1988. In NAND flash memory, several memory cells (typically 8 cells) are connected in series similar to a NAND gate, by that NAND flash memory realized the reduction of memory cell area so that a lower bit cost could be achieved. In NOR flash memory, one end of each memory cell is connected to the source line and the other end directly to a bit line resembling a NOR gate. The advantage of NOR flash architecture is address lines are enough to map the entire memory range and gives real random access and short read times. But the memory cell size is larger

and the per bit cost is higher than NAND structure. Based on the cons and pros, NAND flash memory is mainly used for data storage application and NOR flash memory can be used in embedded systems.

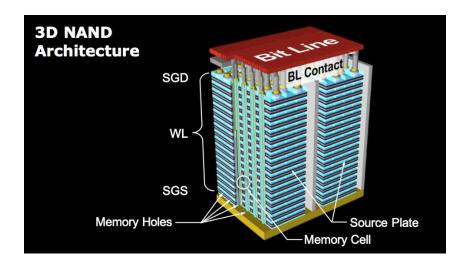

In both NAND and NOR flash memory, the cells are organized into erase blocks. This strategy helps compromise the memory performance and fabrication cost. Also, flash memory is able to erase the stored information by entire blocks, lead to a very fast update speed comparing with EEPROM, which update its data by one byte at a time. Flash memory is considered as a preferable technology for many applications which required multi-time reading and writing of large numbers of data, for example, solid state drive and portable memory stick. The storage density, total capacity and performance keep increase as the development of technology scaling. Now the flash memory scalability has already down to 12 nm by Samsung, Micron and Toshiba. The floating gate transistor architecture of a flash memory is compatible with traditional CMOS process. In addition, 3-D flash memory architecture was first manufactured and commercialized by Samsung in 2014, which open a new door to improve the flash memory storage capacity. Figure 1.3 illustrates the schematic architecture of 3-D flash memory.

Figure 3 Schematic of 3-D flash architecture

However, the integration limit of flash memory is approaching. The further scaling limitation constrain the flash memory capacity increase. Nowadays, research on memory is toward these goals: lowering operation voltage, scaling down the single memory size and increase the density of state in on cell by multilevel. To keep the trend of continuous scaling, revolutionary changes might happen on traditional flash memory.

#### 1.3 Beyond the floating gate structure

Further scaling requires very thin vertical dielectrics to solve the short channel effects and optimize the memory performance. But serious leakage occurs when the tunneling oxide thickness is below 7 nm due to the defect in tunneling oxide caused by multi program/erase operations, thus lower the memory reliability [24-25]. A conventional floating gate memory device must keep the thickness of tunneling oxide at least 8 nm to

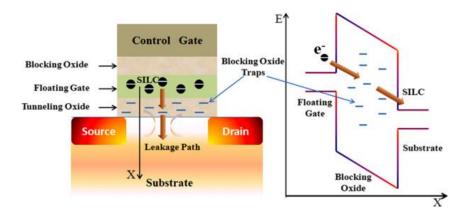

meet 10 years retention time requirement. This necessity will limit flash memory further scaling. Moreover, conventional flash memory still requires a large operation voltage at about 12-15V, which is much larger than CMOS logic devices. For conventional flash memory, if the tunneling oxide could be scaled down to 2nm, the operation voltage could be reduced to 4V. However, the retention time would also be reduced from 10 years to 10 seconds due to stress-induced leakage current (SILC) showing in figure 1.4.

Figure 4 Schematic picture of Strees-induced leakage current (SILC)

The limitation of the tunneling oxide thickness becomes more and more important, Novel storage concepts and materials is becoming attractive as a reasonable solution to overcome some of the further scaling challenge. Charge trapping non-volatile memory is an attractive new flash technology by replace the poly-silicon floating gate with dielectric charge trapping materials [26-28]. The charge trapping non-volatile memory displayed better scalability, good reliability and relative lower operation voltage. Charge trapping

memory technology is derived from the basic structure of conventional flash memory. The Charge trapping memory devices is basically replaced gate oxide of a MOSFET with oxide-charge trapping material-oxide dielectric. Comparing with conventional floating gate flash memory, charge trapping memory has a better retention performance when tunneling oxide is below 8 nm [29]. Besides, charge trapping memory exhibits many other advantages like higher P/E speed. Typically, there are three types of charge trapping memory: polysilicon-oxide-nitride-oxide-silicon (SONOS) memory, nitride based read-only memory (NROM), and nanocrystal memory (NCM) [30-33]. Among these charge trapping memory, the NROM occupied good retention time by applying thicker tunnel layer, but thus lead to higher P/E voltages, and corresponding large power consumption and relative complex voltage pump. NCM's memory performance is good but to keep thee uniformity and control the size of nanocrystal layer is still under research. There is a long journey for NCM from lab to market.

Figure 5 Schematic plot of a SONOS memory cell

SONOS memory has been proposed as a flash technology in 1980s, it exhibits many advantages like easy to fabricate, higher P/E speed, low programing voltage and corresponding low power consumption, even more promising in further scaling according to the ITRS [34]. Figure 1.5 demonstrated the schematic structure of a SONOS memory cell. In SONOS memory, the charge is stored in Si<sub>3</sub>N<sub>4</sub> layer. The discrete traps distribution in Si<sub>3</sub>N<sub>4</sub> make sure the store charges will not whole leaked through a single defect in tunneling layer, which is better than conventional floating gate memory. The SONOS structure can relieve the scaling problem, but the tunneling oxide thickness about 6 nm is still thick. Shallow-level traps is the reason of leakage at high temperature while scaling down the tunneling oxide thickness which contribute to poor retention property. When the trap level is shallow, erase saturation and vertical electron migration degrade the memory performance [35-36]. Erase saturation is another important draw back of the SONOS memory, it defined as the erase less as the erase voltage increased. Thus, the SONOS

memory cannot be used for NAND flash memory unless important technology innovation.

Recently, many non-volatile memory devices have been proposed on the basis of changing charge storage materials and new memory conception. An important work to improve is gain a trade-off between P/E speed and memory reliability. Many high-k materials including thin films and nanocrystals, such as HfO<sub>2</sub>, TiO<sub>2</sub> and ZrO<sub>2</sub>, have been proposed as the charge trapping materials to acquire a better scalability and memory performance [37-40]. The memory retention and P/E speed can be improved by applying thicker high-k materials with larger band gap as the blocking oxide materials while the equivalent gate oxide thickness (EOT) is similar. HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> are considered as future blocking oxide candidate to decrease the electric field through the structure [41].

The introduction of molecular electronics provides a new methodology for flash structure improvement. A molecular memory is a non-volatile memory technology that uses organic molecule as the data store material. Memory devices based on organic materials represent one of the emerging technologies [42] for information storage media to improve the memory performance and satisfy the exponential demand for high-density nonvolatile memory for low-power portable devices. In comparison with the traditional flash memory devices, molecular flash memory can be fabricated at low cost and operated with low-power consumption [43]. The types of organic molecules that have been demonstrated with a remarkable memory effect [44-46] and with different basic memory mechanisms have been reported in recent years. The reported new molecule-containing memory included flash memory, resistive switching memory, chargeable electret memory and ferroelectric memory. Among them, the flash memory based on redox-active molecules

has attracted great interest due to their inherent and relatively stable redox process for charge storage [47-51]. Substantial improvement in memory window, retention, endurance and multibit storage capability have been achieved by applying organic molecular floating gate.

The drawback of molecular flash memory is the instability of organic molecule under high temperature. Some redox molecules are not stable at 200 °C or higher temperature due to evaporation or other reactions. To solve this problem, specific condition and environment need to employ during the fabrication and CMOS integration process. Although molecular memory can achieve very good performance in some memory characteristics, there is trade-off between each aspect of memory characteristics. Overall, molecular flash memory with the integration of redox molecules in solid-state structure is still attractive due to the intrinsic properties of molecule and compatibility with the CMOS fabrication process. Many studies on organic molecule-based charge trapping memory devices have been reported. Lee et al, reported a strong memory behavior induced by ntype doping to p-type conjugated polymers [28]. Tseng et al, reported a retention improvement caused by applying a double-floating gate which has both hole carrier trap units and electron carrier trap units, with the flexible pentacene molecule acting as the channel allowing a study of the stress effect on flexible charge trapping memory devices [53].

Despite the drawbacks, molecular flash memory with the integration of redox-active molecules into a solid-state structure has still attracted intensive attention lately, due to its excellent performance and compatibility with the CMOS fabrication process. For instance,

devices with metal-molecule-metal structure have been well studied, but this structure is vulnerable to defects and metal penetration. A study on preventing contact metal penetration into the molecular layer in the metal-insulator-molecule-metal structure. But this structure suffers from a series of gate leakage problems. Kim et al. reported a study on a metal-oxide-semiconductor structure with molecules encapsulated in gate dielectrics. But the device reliability was not well investigated. [48,51] Up to now, not many studies have yet been reported of the solid-state molecular Flash memory device P/E endurance at fast speed and long time retention. This dissertation focuses on developing hybrid molecular Flash like memory containing redox molecules as store center for charge storage medium to replace current primary data storage drive. We have developed a Si-molecular integration process to preserve the intrinsic redox properties and studied the charge storage properties of the molecular memory. The devices exhibit high P/E speed and low operation voltages and excellent endurance: the devices shows almost no degradation after 10<sup>5</sup> P/E cycles. Robust charge storage behavior can be obtained by employing redox-active molecules with discrete redox states, enabling very stable storage in a given memory storage location. In this thesis, we have demonstrated that the hybrid integration of redoxactive molecules on a Si based structure and 2-Dimensional materials is very attractive for high-performance non-volatile memory applications.

#### 1.4 Overview of dissertation

This dissertation This dissertation has been presented in six chapters.

Chapter 1 (this chapter) gives a brief overview to readers about this dissertation. It starts with the history and development of scaling technology. Different non-volatile memories have been discussed. We find the advantages and drawbacks of each kind of memory devices. Chapter 2 presents a thoroughly discussion of the development of molecular non-volatile memory, the novel dielectric and molecular non-volatile memory structure. Fabrication approaches and memory characterization methodology will also be presented in this chapter. Chapter 3 presents the experiment details and characterization of redox-active molecular charge storage memory. Chapter 4 presents the process variation control. It is essential to get stable devices and high uniformity. Several important process like molecule attachment have been discussed in this chapter. Chapter 5 shows 2-D TMDC material based redox molecular memory devices fabrication process and the memory performance. Chapter 6 summarizes this research and presents a path to future research efforts related to this work.

# Chapter 2 Fabrication, Operation and Characterization of Molecular Memory

#### 2.1 Introduction

Molecular memory, among the new emerging memory candidates in recent years, is considered promising, particularly for the aim of reducing the size per cell and enhancing the memory speed, density and reliability. Molecular electronic devices are typically fabricated by forming a self-assembled monolayer (SAM) or multi-layer on different surfaces with very inexpensive and simple processing methods. Moreover, molecular memory works by the controlling of fewer electrons at the molecule scale and, therefore, has potential for low-power and ultra-high-density memory applications with a lower fabrication cost. In order to further improve the molecular memory performance. We focused on the gate stack engineering with high-k dielectric materials and redox-active molecules for access flash memory devices with fast P/E speed, good reliability, high storage density and low power consumption. We demonstrated a capacitor structure memory cells, by which charging, discharging and other memory properties can be measured straightforwardly. Metrology of Si based redox-molecular non-volatile memory in the MOSFET technique can be realized by current semiconductor electronics characterization technologies.

As the development of molecular electronics and the integration between semiconductor technology and molecular electronics devices, the Si-molecule hybrid devices will gradually become accessible both in modern electronics research and industry. Great efforts have been made to integrate molecules as the active component for fulfillment of future electronic devices.

#### 2.2 Recent development of molecular memory.

#### 2.2.1 Early stage of molecular memory

Two fundamentally different method to fabricate molecular electronics devices are graphically termed "top-down" and "bottom-up". Instead of top-down, which includes making nano-scale structures by machining and etching techniques, molecular electronics rely on the "bottom-up" approach, by using the molecule self-assembly property. Bottom-up refers to building organic or inorganic structures by atom-by-atom or molecule-by-molecule techniques. In the past few decades, research on molecular electronics has been focusing more and more on the combination of top-down device fabrication (mainly lithography) with bottom-up molecule self-assembly.

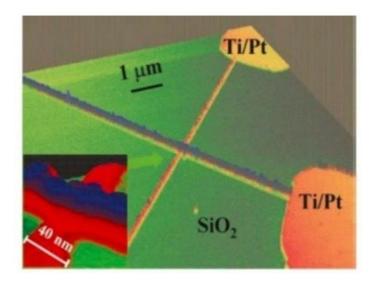

Figure 6 Atomic force microscopy image of a nanoscale cross-point molecular switching device

The crossbar molecular circuit is one of the earliest logic forms of molecular memory arrays. The switching element is a metal/molecule/metal sandwich junction, wherein the molecules are located at the cross-section of two nanoscale metal wires. The early demonstration of such junction molecular switching devices utilized molecules consisting of two mechanically interlocked rings [54-57], the AFM image of the junction they fabricate is shown in figure 2.1. The molecular monolayers were deposited as a film. The mechanical motion of these molecules is an activated redox process, and two stable and electrochemically-switchable states of the molecules form the logic on and off states. The molecular switching devices can exhibit a  $\sim 10^2$  on/off current ratio, but with limited endurance cycles numbers. Based on such switching devices, an 8  $\times$  8 crossbar has been built by the Hewlett-Packard research group [58]. This approach has the advantage of architectural simplicity and the potential of high density via fabrication of high-density

nanowires array. However, this approach has two major drawbacks, including a high rate of defective switching elements and the difficulty in controlling the metal/molecule interface. Even though a defect-tolerant architecture had been established earlier, the metal/molecule problems in such junction switching devices and crossbar circuits are still to be addressed [59]. In later research work, it was reported that the electron transport phenomena in the metal/molecule/metal junction were molecule independent; instead, they were dominated by electrode reactions with molecules, and the intrinsic spacing of the energy levels might be modified [60–62]. Another architecture utilizing metal/molecule/metal junction is the so-called nanocell molecular circuit, proposed by researchers at Rice University and Yale University [63-66]. A nanocell is a twodimensional network of self-assembled metallic particles connected by molecules that show reprogrammable negative differential resistance [63,64]. The nanocell is surrounded by a small number of lithographically-defined metal lines that provide input and output leads. The active component for a nanocell is also a metal/molecule/metal switch, and one pathway may include more than one molecular switch [67-69]. The molecule pathways can be learned first by developing appropriate computation algorithms; then, the whole cell can be programmed to realize a particular function. Such a nanocell molecular circuit uses similar molecular switches as the crossbar molecular circuit, but the circuit architecture is quite different. Compared to the crossbar approach, the nanocell approach has the advantages of large-scale circuit fabrication and integration. However, the disadvantage is that it relies on complex programming mechanism. Meanwhile, both the nanocell and crossbar approaches may have the same difficulty in controlling the

metal/molecule interface.

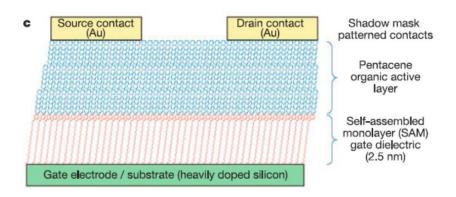

In addition to the metal/molecule/metal switching devices, molecules have also been tested as the channel material in a standard MOSFET structure [70–73]. With the replacement of the high-k dielectric with an ultra-thin SAM of an organic active layer in a field-effect transistor (FET), the researchers from Infineon have reported an organic field-effect transistor (OFET) with low operation and low gate leakage current, the structure of this molecular FET is shown in figure 2.2.

Figure 7 structure of a pentacene organic FET

#### 2.2.2 Non-volatile memory based on redox-active

Appropriate modifications of the molecular structures and switching elements have been designed to change the switching kinetics and to enhance the performance for different memory applications. Different device platforms have been engineered to interface with the molecules, such as dielectrics, oxides, nanowires, carbon nanotubes, and so forth. A well-known method to achieve a memory effect is by employing redox-active elements. The redox mechanism involves electrons being transferred from one element to another, such that a donor element gives up an electron (oxidation) to an accepting element (reduction). This process usually requires an external stimulus for redox reactions, such as an electric field or change in temperature. Such redox-active molecule-based memory devices can show fast speed, low operation voltage and high reliability, due to the intrinsic redox behavior of the molecules. Therefore, it is very attractive for flash memory device applications.

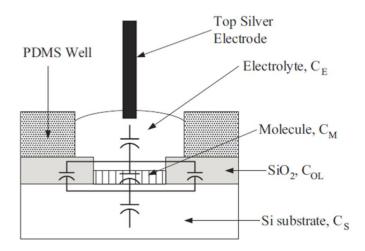

The research group at North Carolina State University proposed hybrid CMOS/molecular memory devices, in which the redox-active charge-storage molecules were incorporated into Si structures to generate a new class of electronic memory devices [74-78]. These redox-active molecules, which can be designed to self-assemble on surfaces as monolayers, exhibit charge-storage states at discrete voltage levels. This approach can provide a smooth transition from CMOS technology to molecular electronics technology by integrating develop CMOS technology with naturally derived molecular properties, the capacitor structure they developed is shown in figure 2.3 with equivalent circuit.

Figure 8 Schematic of electrolyte-molecule -Si capacitor structure and corresponding equivalent circuit.

The capacitance-voltage (C-V) and conductance-voltage (G-V) characteristics also exhibited clear capacitance and conductance peaks associated with charging and discharging in the molecules. Similarly, multiple peaks were observed with the Por-BzOH EMOS capacitor due to its two charged states. Interestingly, the two charged states within molecules, such as Por-BzOH, can be employed for a multi-bit storage application to further enhance the memory density. Despite using a redox molecule exhibiting multiple charged states, an alternative and perhaps more efficient strategy to achieve higher memory bits is afforded by simply mixing different redox-active molecules whose potentials are well separated. Fc-BzOH and Por-BzOH SAMs have been mixed on Si, and the mixed SAMs exhibit well-defined redox states [79]. The mixed SAM approach is very attractive owing to the fact that this approach is synthetically far simpler than preparing a single molecule that exhibits three or more redox states. In addition, the potential of the redox

charged states is more distinct than that of a single molecular redox center with multiple charged states. However, the disadvantage of this method is that the density of a given peak goes down [80]. Nevertheless, this mixed SAM approach still paves the way for constructing multi-bit memory storage devices.

#### 2.2.3 Towards better memory performance

The conventional polysilicon floating-gate flash memory has benefited the semiconductor memory technology for decades, due to its scalability, compatibility with CMOS process, and so forth. It relies on hot electron injection from the channel into the floating gate through a tunneling oxide layer. By attaching redox-active molecules to Si as the floating gate in the CMOS structure, one can further enhance the cell density and reduce the cell variations. The combination of top-down lithography and bottom-up molecule self-assembly processes renders a uniform charge density, and the monodisperse nature of the molecular orbitals leading to distinct energy levels can enable precise controlling of charged states [81].

The self-assembly process of the redox-active molecules to form a solid-state molecular memory enables not only high-quality attachment of molecules to semiconductor surfaces, but also uniform and high-density fabrication of low-cost devices and circuits. The disadvantages of molecular flash memory mainly lie in its reliability in volatile environments. Some redox-active molecules are instable or even do not function at temperatures higher than 200 degree due to evaporation or redox center reaction. Under volatile environments with oxygen or water, the molecule's bond might be broken, leading to poor redox behavior. As a result, some specific conditions and environments need to be

taken into account when integrating such redox molecules in CMOS devices and circuits. Future molecular technology requires advancement in both molecule properties and device integration processes.

The researchers from North Carolina State University reported a study on preventing contact metal penetration into the molecular layer in the metal-insulator-molecule-metal structure [82]. Similar work demonstrating that redox properties of molecules can be preserved after thin film encapsulation, such as atomic layer deposition (ALD), initiated the investigation on high-performance solid-state molecular memory [83]. The Cornell University research group reported a study on a metal-oxide-semiconductor (MOS) structure with molecules encapsulated in a high-k dielectric and functioning as the charge storage medium [84, 85]. molecules with different redox centers, which can show one and two charged states, have been studied for multi-bit memory. With the electrostatics determined by the alignment between the highest occupied or the lowest unoccupied molecular orbital (HOMO or LUMO, respectively) energy levels and the charge neutrality level of the dielectric, the asymmetric charge injection behavior in flat-band voltage shift (DVFB) vs. programming voltage measurement is due to the Fermi-level pinning between the molecules and the high-k dielectric [86-88]. The three programmable molecular orbital states of the 5-(4-Carboxyphenyl)-10,15,20,-triphenyl-porphyrin-Co(II) (CoP) molecule have been experimentally observed and are attractive for low-variation multi-bit memory applications. The engineering by the same group on the tunnel layer has greatly enhanced the electron retention and programming performance by forming an organic-inorganic tunnel barrier [85].

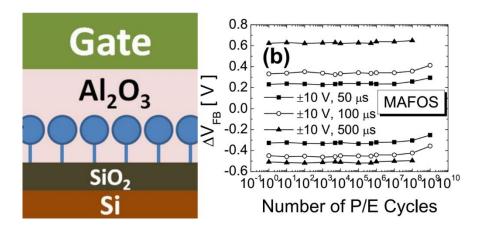

Figure 9 Schematic of α-ferrocenylethanol molecular memory structure and the excellent endurance property

Recently, the NIST researchers have reported a similar capacitor-structure molecular

non-volatile memory, but with enhanced charge retention and excellent endurance [89]. The molecular memory uses an α-ferrocenylethanol redox molecule, which has a very simple structure and one redox center. With the molecules attached to the SiO<sub>2</sub> tunnel oxide and encapsulated in the ALD Al<sub>2</sub>O<sub>3</sub> dielectric, the solid-state molecular memory exhibited excellent memory behavior, such as a sufficient memory window, good retention and endurance. Even though only ~15% of the molecules were effectively involved in the redox processes after ALD, effective memory can be realized with sufficient charge density. These characteristics are attributed to the intrinsic redox behavior of the ferrocene molecule and the effective protection from the presence of the gate dielectric covering the molecule SAM. The molecular memory showed excellent endurance properties, with negligible memory window degradation after 10<sup>9</sup> P/E cycles, which is about 10,000 times better than that of the conventional floating gate memory (1

$\times 10^5$  P/E cycles), the schematic structure of their capacitor memory structure and great endurance characteristics are shown in figure 2.4. However, the operation voltage of such molecular memory is still high, and the operation speed needs to be improved. Further study of the molecular memory depends on the engineering of redox-active molecules, such as molecules with multiple redox centers and a proper linker for multi-bit memory, and the device structure engineering to optimize the dielectric stack thickness and improve the molecule/dielectric interface. Such an exploration will be a significant breakthrough in the quest for charge-storage non-volatile memory and will enable the application of flash-like devices for future on-chip memory applications.

## 2.3 Fabrication of Si based redox-active molecular flash memory

The capacitor structure flash memory cells were fabricated by applying standard photolithography and film deposition procedures. Dielectric stacks parameters including the tunneling oxide, redox-molecular charge storage layer, and blocking oxide were employed and optimized. The attachment of redox-active molecules on Si/SiO<sub>2</sub> surfaces was fulfilled by self-assembled monolayers (SAMs) on Si/SiO<sub>2</sub> surfaces. The connection between SAMs and Si/SiO<sub>2</sub> surfaces is covalent bond through AUS linkage material. The process procedures are as the following list:

- (1) Stand RCA clean process is employed on Si wafer prior to fabrication process

- (2) A 290 nm  $SiO_2$  film is thermally grown on low-doped p-type (100) Si wafer substrates (~10<sup>16</sup> cm<sup>-3</sup> Boron doped) by dry oxidation in CMOS oxidation furnace.

- (3) Arrays of squares with different active area ranging from 100 to 10000 μm<sup>2</sup> are

defined on the wafer by photolithography with Suss MA-6 and/or MA-8 aligner.

- (4) Buffered oxide etch (BOE) solution and 2 % hydrofluoric (HF) acid are used for the removing of oxide defined by lithography process to get the arrays of experimental window areas in the 290 nm thermal SiO<sub>2</sub>.

- (5) The tunneling oxide (thin SiO<sub>2</sub>) is grow by rapid thermal oxidation (RTO) instantly after step (4), different oxide thickness can be defined by adjusting the temperature and RTO process time.

- (6) The redox molecules solution is prepared by dissolving the molecules in designated solvent. Dichloromethane and toluene are used to dissolve redox molecules for attachment process in this work.

- (7) The molecular film is realized by self-assembling process on window areas by 'click' chemical reaction. First, AUS linkage material is attached by immersing the substrate into AUS solution with 95 °C hotplate for 2-3 hours with a loose cover. The liquid evaporation helps the attachment process. After that, mix the Ru molecule solution and other proper solution which helps the attachment process evenly and drop them into Sodium L-ascorbate solution slow and evenly, then immerse the AUS covered substrate into the container covered with loose lid. The Ru molecule will be attached on substrate after several hours in room temperature. The attachment process is conducted in a glovebox with N<sub>2</sub> environment. The attachment conditions are same for both attachment on Si and SiO<sub>2</sub> surfaces. Figure 2.5 shown the illustration of molecule attachment process.

Figure 10 Illustration of molecule attachment process

- (8) After the molecular film was formed, two cycles of 5 min sonication clean was applied to rinse the attached sample for removing physisorbed residuals on the surface with DCM solvent.

- (9) The attached samples were separated into two groups: one group for attachment characterization like X-ray photoelectron spectroscopy (XPS) and Atomic Force Microscope (AFM); the other group is for molecular memory device fabrications. This group of samples will immediately load into the Atomic Layer Deposition (ALD) vacuum chamber right after the sonication clean for blocking oxide Al<sub>2</sub>O<sub>3</sub>. The ALD operation

temperature is set to 100  $^{\circ}$ C in case of the instability of organic molecule, with H<sub>2</sub>O and TMA as precursors.

(10) As the final step, Pd was deposited and patterned on the top of the devices as the top gate by photolithography and E-beam evaporation, followed by the lift-off process.

The samples for XPS and AFM are prepared by doing molecule attachment on highly doped p-type Si substrate without patterned structure, but the attaching recipe and process is same as the previous described methods.

Attachment of target molecules and successfully encapsulated by ALD deposition Al<sub>2</sub>O<sub>3</sub> is the key point of the redox molecular memory fabrication process. The molecular film was characterized by CyV, XPS and AFM measurements. Somme samples after deposition a thin layer of ALD Al<sub>2</sub>O<sub>3</sub> are measured by XPS, and the results demonstrated the molecule survived in the low temperature ALD process. The capacitor memory device fabrication is illustrating in Figure 2.6.

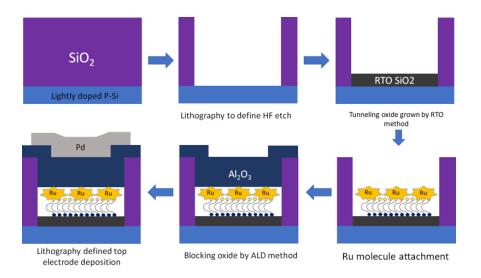

Figure 11 Capacitor memory device fabrication flow

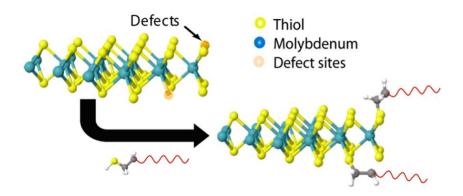

### 2.4 Fabrication of 2-D material based molecular memory

The attachment of redox-active molecules on 2-D materials is carried out by the replace the Sulfur atom or fill the Sulfur vacancy with thiol moiety on monolayer MoS<sub>2</sub> surface. The connection between molecule and MoS<sub>2</sub> is covalent bond. Figure 2.7 exhibits the illustration of replacement or fill process [90]. The characterization of molecule attachment on 2-D materials done by using XPS measurement, prior to the memory cell fabrication process, the processing steps are as follows:

- (1) Stand RCA clean process is employed on Si wafer prior to fabrication process

- (2) A 290 nm SiO<sub>2</sub> film is thermally grown on moderate-doped n-type (100) Si wafer substrates (~10<sup>17</sup> cm<sup>-3</sup> phosphorous doped) by dry oxidation in CMOS oxidation furnace. The 290nm SiO<sub>2</sub> is used for identifying the color of different layer number of MoS<sub>2</sub> under

optical microscopy.

- (3) Monolayer MoS<sub>2</sub> flakes is prepared by Au-mediated mechanical exfoliation method and then transfer to SiO<sub>2</sub> substrate. (the method will be discussed in chapter 5)

- (4) Monolayer MoS<sub>2</sub> is patterned photolithography method and then etched by Reactive-ion etching (RIE) in SF<sub>6</sub> plasma

- (5) The drain and source electrode are deposited and patterned on MoS<sub>2</sub> by photolithography and E-beam evaporation, followed by the lift-off.

- (6) The redox molecules solution is prepared by dissolving the molecules in toluene solvent. The attachment process of molecules on MoS<sub>2</sub> surface is realized by immersing the substrate in to molecular solution (0.1mMol) for several hours with 70 °C hotplate. The attachment process is performed in glovebox with N<sub>2</sub> environment.

- (7) After the molecular film was formed, two cycles of 2 min sonication clean was applied to rinse the attached sample for removing physisorbed residuals on the surface with toluene solvent.

- (8) The molecular attached samples will immediately load into the Atomic Layer Deposition (ALD) vacuum chamber right after the sonication clean for blocking oxide Al<sub>2</sub>O<sub>3</sub>. The ALD operation temperature is set to 100 °C in case of the instability of organic molecule, with H<sub>2</sub>O and TMA as precursors.

- (9) Finally, Pt is deposited and patterned on the top of the devices as the top gate by photolithography and E-beam evaporation, followed by the lift-off process.

Figure 12 Illustration of attachment process on MoS<sub>2</sub>[90]

The samples for XPS measurements are prepared by attach the redox molecule to large area MoS<sub>2</sub> sample deposited by Chemical vapor deposition (CVD) method. The attaching method and recipe is same with method described above.

### 2.4 Physical and electrical characterization

To confirm the molecule attachment process, XPS measurements were done by using a Kratos Axis Ultra instrument equipped with monochromatized Al Kα photons. We can demonstrate the molecule attachment by detecting specific element peaks, the coverage of molecule film could also be roughly estimated by the XPS measurement result. AFM images were obtained using Bruker Dimension FastScan in semi-contact mode to investigate the sample surface morphology. The surface roughness is greatly decided by the molecular size and hardness.

To study the memory device characteristics, electrical characteristics were measured in a dark environment with a commercial probe station. Bias was applied between the metal

gate and the silicon substrate during all the electrical measurements.

The memory performance of the capacitor structure molecular memory devices can be investigated by the measuring of the flat-band voltage curve under different bias sweeping conditions. A series of capacitance-voltage measurement at various frequencies were applied by using Agilent E4980A LCR meter to determine the retention attribute. Pulse response sensitivity measurements were implemented with an Agilent 4156 Semiconductor Parameter Analyzer. A Hewlett Packard 33120A waveform generator was applied to measure the Program/Erase endurance by produce designated voltage pulses.

Cyclic voltammetry (CV) measurements were performed using a Solartron Modulab potentiostat to verify the memory application potential of molecule. The electrolyte was 0.1 mol/L tetrabutylammonium hexafluorophosphate in anhydrous acetonitrile and was deoxygenated with dry  $N_2$  prior to use. A three-electrode cell configuration was used with the Ru molecule clicked onto native oxide/Si as the working (area =  $0.32 \text{ cm}^2$ ). The cell is completed with a platinum wire counter electrode, and a silver quasi-reference (AgQRE) electrode. The sweep rate was 10 mV/s.

# **Chapter 3 Redox-active Molecular Memory Based on Si**

#### 3.1 Introduction

The CMOS scaling according the Moore's law to realize faster central processing unit (CPU) is reaching the fundamental and physical limits induced by large heat production and short-channel effect as the technology node down to several times of atomic size. However, the scaling of semiconductor flash memory is far behind CPU device scaling. The EOT of the gate stack in semiconductor flash memory is still more than 10 nm while the EOT of CMOSFET with an equivalent EOT at 0.8 nm in 2001 [91]. The work hour of mobile devices and memory cell size scaling could be significantly increase if the scale of EOT of memory gate stack. Many materials have been proposed for improve this property.

Molecular electronics technology is getting more and more attention since 1970s due to the inherent scalability and intrinsic properties of molecule [92-93]. Molecular memory devices are considered as promising emerging memory candidates due to the potential for further cell scaling and improvement of reliability [94]. In a redox-active molecular flash memory cell, the redox-active molecules have distinct oxidation and reduction states accessible at different supplied voltage, which enables stable binary or multiple states for charge storage like that of traditional charge trapping materials [95]. Compared to polysilicon and Si<sub>3</sub>N<sub>4</sub> charge trapping layer, redox-active molecule has the advantage of intrinsic molecular scalability at the nanoscale, multiple bits and tunable electronic

properties to achieve ultrahigh storage density. In addition, redox molecules can be tuned to attach onto different kinds of semiconductor materials [96] and form self-assembled few-layer or monolayer structures with low-cost processes, usually a solution-based process, which provides a great advantage for promising commercial memory application in the future.

The excellent retention property of the redox-active molecules based on Si structure has been demonstrated with enduring more than  $10^{12}$  program/erase (P/E) cycles [97]. The excellent performance in reliability is naturally derived from the intrinsic reduction and oxidation states stability of redox molecule materials. Redox-active molecular memory devices usually fabricated by forming a self-assembled monolayer (SAM) or multi-layer film on various kinds of material surfaces. This process, known as attachment, is very cheap and simple achieved. Besides advantage of cheap cost fabrication process, molecular memory can work with few electrons at the molecular level, which stand for the potential for extremely low pow consumption and ultrahigh storage density. To commercialize a real molecular electronic product consist of understanding multiple comprehensive mechanism of the electrical of molecule materials both in macroscopic scales and atomic scales, interface morphologies and precise atomic level manipulation. Great efforts have been devoted on improving memory storage density, multibit data storage and the P/E speed improvement of molecular memories based on organic molecules, electrets, conjugated polymers and ferroelectric molecule materials [98-107]

For redox-active molecular memory devices, applying an oxidation voltage will cause the electron loss in redox molecules; on the other hand, electrons will be driven back to molecules under a reduction voltage bias, typically this process is very fast and lead to a very fast P/E operation speed. In addition, the intrinsic scalability of molecular level and nature-derived valence states for stable charge storage states make the redox molecule very attractive for high density, long-retention non-volatile data storage applications. [97,104,108]

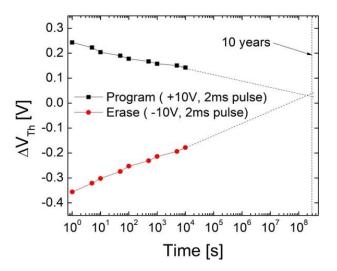

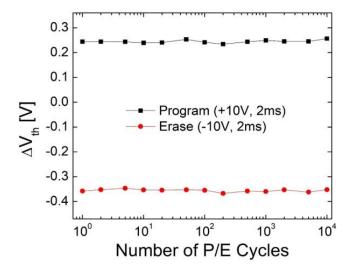

Another attractive advantage of molecular electronics is due to some redox-active molecules are compatible with present CMOS integration process. In this chapter, we present our work on characterization and optimization of redox-active molecules attached on  $Si/SiO_2$  surfaces, and experimentally judge the memory performance of Ru redox molecular non-volatile memory. The results demonstrate the molecular flash memory is promising for low power consumption, high reliability and high density memory application due to their good retention and fast P/E speed at low P/E voltages. A distinguished charge storage efficiency was exhibited with 5.2 V memory window shown under  $\pm$  9 V sweeping gate voltage. The degradation anticipation estimated by the measured data indicated that 72% of the initial memory window will remain after 10 years.

#### 3.2 Experimental details

In our work, we have developed and optimized a Si based molecular integration method to exploit the intrinsic redox properties and investigate the memory performance by measuring capacitor structure molecular memory. the memory devices based on Ru molecules exhibit nonvolatile flash like behaviors. The capacitor structure memory device exhibits a very large memory window of 5.2 V, fast response at a 10<sup>-5</sup> s short P/E pulse, a

long retention time estimated as at least 10 years, and negligible degradation after P/E cycles up to 10<sup>5</sup>. These properties are superior to other demonstrated molecular memory works [109, 110].

Figure 13 The molecule structure of Redox-active Ru molecule and the aliphatic AUS

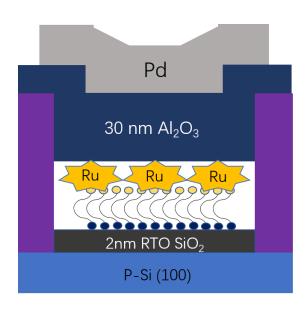

we have fabricated memory cells with a metal-Al<sub>2</sub>O<sub>3</sub>-Ru<sub>2</sub>-SiO<sub>2</sub>-Silicon (MAROS) structure with a Ru molecule SAM on SiO<sub>2</sub>. Figure 3.1 shows the structure of the synthesized Ru redox molecule with the chemical formula: C<sub>50</sub>H<sub>32</sub>N<sub>8</sub>Cl<sub>13</sub>Ru<sub>2</sub> and the linkage molecule 11-Azidoundecyltrimethoxysilane (AUS). The connection between each part is covalent bond.

The metal-oxide-semiconductor (MOS) capacitor structure, applied in our Flashbased memory devices was fabricated and used for the attachment of the redox-active Ru molecules as the charge storage layer which is the most important fabrication procedure. The Ru<sub>2</sub> molecule is attached onto the device substrates by 'click' chemistry with a linker molecule which has been reported by Pookpanratana et al. [111].

Firstly, stand RCA clean process is employed on Si wafer prior to fabrication process. A 290 nm SiO<sub>2</sub> film is thermally grown on low-doped p-type (100) Si wafer substrates ( $\sim 10^{16}$  cm<sup>-3</sup> Boron doped) by dry oxidation in CMOS oxidation furnace followed by the definition of square shaped active window areas (100  $\mu$ m × 100  $\mu$ m) by photolithography and wet etch process.

The tunneling oxide (~2 nm) is grow by rapid thermal oxidation (RTO) instantly at 840 °C for 2 min 30s.

Synthesis work of the Ru redox molecules is performed by our collaborator Prof. Tong Ren. The Ru redox molecules solution is prepared by dissolving the molecules in dichloromethane (DCM) solvent. The molecular film is realized by self-assembling process on window areas by 'click' chemical reaction. AUS linkage material is first attached by immersing the substrate into AUS solution with 95 °C hotplate for 2-3 hours with a loose cover. The liquid evaporation helps the attachment process. After that, mix the Ru molecule solution (0.1 mmol/L) and other proper solution which helps the attachment process evenly and drop them into Sodium L-ascorbate solution slow and evenly, then immerse the AUS covered substrate into the container covered with loose lid. The Ru molecule will be attached on substrate after several hours in room temperature. All attachment operation is conducted in a glovebox with N<sub>2</sub> environment. After the molecular film was formed, sonication clean was applied to rinse the attached sample for removing physisorbed

residuals on the surface with DCM and IPA solvent.

The attached samples were separated into two groups: one group for attachment characterization like X-ray photoelectron spectroscopy (XPS) and Atomic Force Microscope (AFM); the other group is for molecular memory device fabrications. This group of samples will immediately load into the Atomic Layer Deposition (ALD) vacuum chamber right after the sonication clean for blocking oxide Al<sub>2</sub>O<sub>3</sub>. The ALD operation temperature is set to 100 °C in case of the instability of organic molecule, with H<sub>2</sub>O and TMA as precursors.

Figure 14 Schematic of the MAROS capacitor structure

As the final step, a layer of 105 nm Pd was deposited and patterned on the top of the devices as the top gate by photolithography and E-beam evaporation, followed by the lift-

off process. The schematic of MAROS capacitor structure is displayed in Figure 3.2. To make sure the origin of memory effect of capacitor redox molecular memory. We also fabricated two control sample structures for comparison, one of them is no molecule on tunneling oxide, the other is only with AUS linkage molecule.

#### 3.3 Physical and electrical measurement for molecule attachment

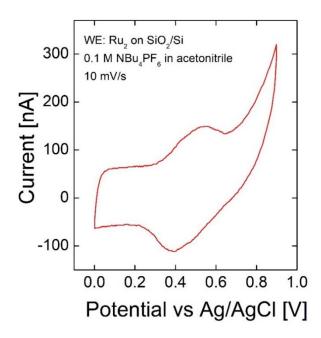

In order to investigate the quality and density of molecule attachment, we applied Cyclic voltammetry (CyV) measurement to some after-attach device substrates. Cyclic voltammetry (CV) measurements were performed using a Solartron Modulab potentiostat to verify the memory application potential of molecule. The electrolyte was 0.1 mol/L tetrabutylammonium hexafluorophosphate in anhydrous acetonitrile deoxygenated with dry  $N_2$  prior to use. A three-electrode cell configuration was used with the Ru<sub>2</sub> molecule clicked onto native oxide/Si as the working (area = 0.32 cm). The cell is completed with a platinum wire counter electrode, and a silver quasi-reference (AgQRE) electrode. Figure 3.3 shows the CyV data of the electrolyte-molecule-oxide-Si (EMOS) structure with Ru molecular SAM on substrate at 10 mV/s sweep rate. The peaks at negative gate voltage (VG) are for oxidation process and the peaks at positive VG are for reduction process, respectively. While the oxidation (or reduction) voltage is applied, the electrons are lost from (or driven back to) the molecular layer. The CyV measurements of the attached Ru molecule on SiO<sub>2</sub>/Si substrates (as the working electrode) demonstrate that the Ru molecule is electrochemically active. Upon sweeping the potential between 0V and 1.0V (with respect to the AgQRE), a reduction-oxidation (redox) pair is observed after

Figure 15 CyV of the EMOS capaciptor at 10mV/s sweep rate.

multiple cycles. The cathodic peak center is about 0.5V, while the anodic peak center is about 0.39 V. When compared to the same Ru molecule in solution, this redox feature is consistent with the reversible oxidation of the diruthenium core going from  $Ru_2(III, II)$  to  $Ru_2(III, III)$ . Therefore, the Ru2 molecules are robustly integrated to the SiO2/Si substrate and they are still electrochemically active, which is promising for solid state molecular memory applications. The surface coverage density of Ru molecule can be roughly estimated form the oxidation peak line [112], the value is calculated to be  $2\times10^{12}$  cm<sup>-2</sup> on SiO<sub>2</sub> surface.

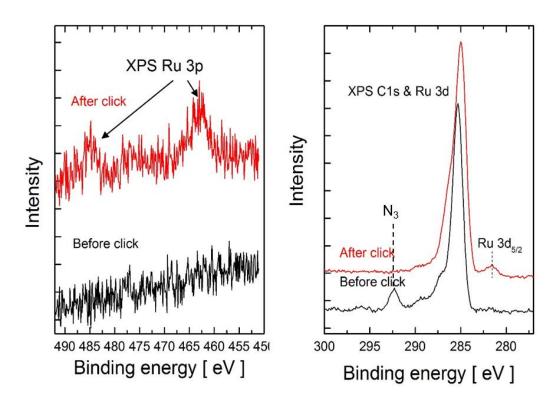

Figure 16 XPS measurement of (left) samples with Ru molecule attached on SiO<sub>2</sub> surface, and(right) sample before "click" reaction.

To directly confirm the chemical attachment information of the Ru<sub>2</sub> molecular SAM, XPS measurement were applied to the samples with Ru<sub>2</sub>-containing sample and the AUS linker Figure 3.4 presents the XPS spectra gathered from the Ru<sub>2</sub>-containing sample ("after click") and the AUS linker ("before click"). Ru 3d<sub>5/2</sub> and Ru 3p peaks can be detected in the spectra of the Ru<sub>2</sub> SAM sample in contrast to the AUS linker surface, peak for N<sub>3</sub> moieties in AUS linkage cannot be find after "click" due to click reaction open the N<sub>3</sub> ring and form covalent bond with Ru molecule, which indicates that the Ru<sub>2</sub> molecule has been

attached on the SiO<sub>2</sub> surface successfully. The coverage density of Ru molecules on the SiO<sub>2</sub>/Si substrate is estimated as 0.3 molecule per nm<sup>2</sup> by the calculation of the Ru 3d and Si 2p XPS spectral lines with Si substrate as the reference [113].

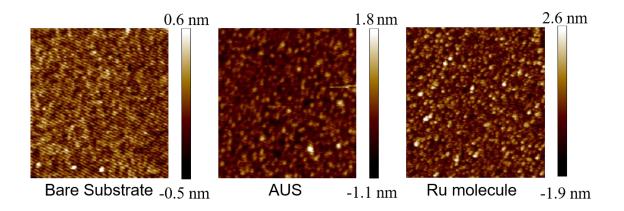

The surfaces morphology was investigated by AFM in semi-contact mode. The AFM image of bare Si substrate (left), Si substrate with azidoundecyltrimethoxysilane (AUS) linkage molecule (middle) and Ru<sub>2</sub> molecular SAM on Si substrate (right) are shown in Figure 3.5. The data revealed relatively smooth film surfaces and homogeneous monolayers. The root-mean-square (rms) roughness,  $R_{rms}$  increased after the molecule attachment process. The  $R_{rms}$  of the bare substrate, AUS layer, and the final diruthenium layer for a  $1\mu m \times 1\mu m$  scan area were found to be  $\approx 0.16 nm$ , 0.31nm and 0.64nm, respectively.

Figure 17 AFM image of (left)Bare Si, (middle)substrate with AUS and (right)Ru molecular SAM on Substrate

#### 3.4 Molecular memory characterization

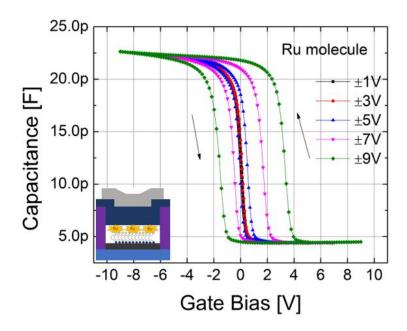

Figure 18 C-V measurements of memory devices with Ru attached structure

In memory operations, electrical bias should be applied to the gate electrode and thus induce the movement of charges between the semiconductor substrate and charge storage layer. Memory window in capacitor structure memory can be defined as the change of flat band voltage between forward and backward voltage sweeping. The memory window performance of the Ru<sub>2</sub> molecular memory devices and control samples is characterized by capacitance-voltage (C-V) hysteresis at 1 MHz, with multiple voltage sweeping range. As the result shown in Figure 3.6, the Ru<sub>2</sub> molecular memory window can be defined as the shift of the flat-band voltage ( $\Delta V_{FB}$ ) from oxidation states to reduction states is about 5.2 V at an applied sweeping gate voltage between 9 V and -9 V at 1.0 MHz. The hysteresis

loop in C-V measurement is due to the charge stored in the  $Ru_2$  molecule SAM: electrons tunnel out of the molecules to Si at negative  $V_G$  (oxidation) and tunnel back into the molecules at positive  $V_G$  (reduction). The density of the trapped charges per unit area  $(N_t)$  can be roughly estimated by using the following formula:

$$N_t = C_{ox} \Delta V_{FB} / qA$$

,

where  $C_{ox}$  represents the capacitance at the accumulation region,  $\Delta V_{FB}$  of the shift in the flat-band voltage, A of the effective device area, and q of the elementary charge. The density of the trapped charges in Ru<sub>2</sub> molecular memory devices at a sweeping voltage with  $\pm$  9 V, 1 MHz is calculated as  $7.3\times10^{12}$  cm<sup>-2</sup>, which means about 0.25 electron could be stored in every Ru molecule.

Figure 19 C-V measurements of memory devices with (left) only AUS linkage and (right) with no molecule

For comparison, the sample with AUS linkage molecule but no Ru<sub>2</sub> molecules has a much smaller program  $\Delta V_{FB}$  and almost no erase  $\Delta V_{FB}$  and the sample with no molecule showed even smaller  $\triangle V_{FB}$  (Figure 3.7). We define positive (or negative)  $\triangle V_{FB}$  with positive (or negative) V<sub>G</sub> as programming (or erasing) operation, corresponding to electron get (or loss) in Ru<sub>2</sub> molecule, corresponding to reduction (or oxidation) of the molecules, respectively. The interface next to Al<sub>2</sub>O<sub>3</sub> usually have some trap states and thus lead to charge storage, inducing a small  $\triangle V_{FB}$  also. As the result shown in Figure 3.8, the  $\triangle V_{FB}$ of the samples without molecule is smaller than that of Ru<sub>2</sub> molecular samples after the same voltage pulse, indicating that the electron storage effect is mainly from the Ru<sub>2</sub> molecules. The hole injection starts to show observable  $\Delta V_{FB}$  at lower than -8 V gate voltage, while the  $\approx$  6 V gate voltage is required for electron injection to show a clear  $\triangle V_{FB}$ . This slight difference of  $\Delta V_{FB}$  at low gate voltage is partially due to the more preferred of electron storage than electron at the Ru/Al<sub>2</sub>O<sub>3</sub> interface, which will be discussed in following paragraph. While increases P/E voltage bias, the ferrocene molecular memory shows larger  $\Delta V_{FB}$ , indicating the charges are injected and mainly stored in the redox centers of Ru molecule.

Figure 20  $\triangle V_{FB}$  of these 3 structures as a function of P/E voltage with pulse width= 2ms

Figure 3.9 exhibits the P/E speed characteristics of Ru molecular memory devices. Pulses of  $\pm 10$ V with different widths were applied to determine the response speed of the P/E operations. Ru molecule memory device shows a fast switch speed in both programing and erasing actions. From the high-frequency (1 MHz) C-V curves in figure 15, even with a pulse width as small as  $10^{-5}$  s, Ru memory devices still have a response and show  $\Delta V_{FB}$  at 0.15V (program) and 0.09V (erase), respectively. We notice that the distribution of  $\Delta V_{FB}$  during the erase operation is relatively less compared to  $\Delta V_{FB}$  under the same voltage amplitude program operation. And this suggests that the programming response is faster than erasing response in our Ru<sub>2</sub> molecule memory devices although the difference is not big in this Ru<sub>2</sub> molecular memory. This response different phenomena could be due to the difference in the density of traps for electrons and holes within the storage layer and the

relative energetic positions of the molecular orbitals with respect to the band edges of the inorganic layers. Figure 3.10 shows the band diagram alignment of the Ru molecular memory structure. The highest occupied molecular orbital (HOMO)/ lowest unoccupied molecular orbital (LUMO) for Ru molecule are measured by Prof. Tong Ren [114], the provider of molecule. The levels of HOMO and LOMO is -5.83 eV and -4.48 eV, respectively. The charge neutrality level (CNL) of Al<sub>2</sub>O<sub>3</sub> deposited by ALD method is at -5.2 eV, which can be roughly considered as a local Fermi level of the interface states. For electron injection, the extra energy for electrons to get injected into ferrocene LUMO is  $E_{LUMO} - E_{C} = -0.33$  eV, where  $E_{C}$  is the level of Si conduction band bottom. The injected electrons will be relaxed into interface states surrounding the CNL due to the lower energy level. At the same time, the extra energy for holes to be injected into ferrocene HOMO is  $E_{V} - E_{HOMO} = 0.55$  eV, where is the level of Si valance band top. Therefore, electron injection is preferable than hole injection.

Figure 21 Schematic band diagram of Ru molecular memory structure

Figure 22 Response speed characteristic of Ru molecular memory device.

Figure 23 Endurance characteristics of Ru molecular memory devices under P/E pulse at  $V_G=\pm 10~V$  with 1 ms pulse width