# DESIGN, IMPLEMENTATION AND ANALYSIS OF EFFICIENT FPGA BASED PHYSICAL UNCLONABLE FUNCTIONS

by

Bilal Habib

A Dissertation

Submitted to the

Graduate Faculty

of

George Mason University

in Partial Fulfillment of

The Requirements for the Degree

of

Doctor of Philosophy

Electrical and Computer Engineering

| Committee: |                                                           |

|------------|-----------------------------------------------------------|

|            | Dr. Kris Gaj, Dissertation Director                       |

|            | Dr. Jens-Peter Kaps, Dissertation Co-Director             |

|            | Dr. Houman Homayoun, Committee Member                     |

|            | Dr. Huzefa Rangwala, Committee Member                     |

|            | Dr. Monson H. Hayes, Department Chair                     |

|            | Dr. Kenneth S. Ball, Dean, Volgenau School of Engineering |

| Date:      | Summer Semester 2016 George Mason University Fairfax, VA  |

# Design, Implementation and Analysis of Efficient FPGA based Physical Unclonable Functions

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

By

Bilal Habib

Master of Science

George Washington University, 2010

Bachelor of Science

University of Engineering and Technology, Pakistan, 2005

Director: Kris Gaj, Associate Professor Co-Director: Jens-Peter Kaps, Associate Professor Department of Electrical and Computer Engineering

> Summer Semester 2016 George Mason University Fairfax, VA

Copyright 2016 Bilal Habib All Rights Reserved

#### Dedication

I dedicate this to my loving wife Madeha. She has been a constant source of support during my graduate studies. She worked tirelessly at home and at her job, so that I can focus more on my PhD. To my son Ghani, who has been a cheerleader in my doctoral studies. Lastly, to my mom, Parveen and my late father Habib ur Rehman, who always prayed for my success.

### Acknowledgements

I would like to thank my PhD advisor Prof. Kris Gaj for his continuous guidance, support and mentoring. He urged me to explore new ideas and think along mathematical lines for analysis. He thoroughly reviewed my publications before submission. His comments greatly improved the quality of my papers.

I am also very grateful to my co-advisor Prof. Jens-Peter Kaps for his valuable directions. His suggestions in the implementation of low area hardware designs were remarkably useful.

Additionally, I am very thankful to my committee members Prof. Houman Homayoun and Prof. Huzaifa Rangwala for taking keen interest in my research.

I would like to thank my colleagues and friends in the CERG lab. They include Marcin, Umar, Rabia, Aaron, Rajesh, Panasayya and Ahmad. They always provided a congenial company during my stay in the lab.

Additionally, I would like to thank McQ Inc for allowing me to use their equipment for testing.

I am grateful to the Government of Pakistan and the Provost Office of graduate education for their generous financial support, without which all this was not possible.

Lastly, I would like to appreciate the ECE department of George Mason University, which hired me as a teaching assistant for a significant number of semesters. It helped me to cover my expenses during my studies.

# **Table of Contents**

| List | of Tables                                     | viii |

|------|-----------------------------------------------|------|

| List | of Figures                                    | X    |

| Abst | tract                                         | xiv  |

| 1.   | Introduction                                  | 1    |

| 1.1  | 1. Motivation                                 | 2    |

| 2.   | Previous Work                                 | 4    |

| 2.1  | .1. Types of PUFs                             | 6    |

| 2.2  | 2. Properties of PUF                          | 15   |

| 2.3  | .3. Target Applications                       | 16   |

| 2.4  | 4. Attacks                                    | 17   |

| 2.5  | .5. Challenges                                | 20   |

| 2.6  | .6. General Error Correction                  | 24   |

| 3.   | Goals and Contributions                       | 26   |

| 3.1  | 1. Development of new SR-Latch PUF            | 27   |

| 3.2  | 2. Development of new RO-PUF                  | 28   |

| 3.3  | 3. Robustness                                 | 29   |

| 3.4  | 4. Portability                                | 30   |

| 3.5  | 5. Efficiency                                 | 31   |

| 3.6  | .6. List of Contribution                      | 33   |

| 4.   | Methodology                                   | 35   |

| 4.1  | .1. Collection of Raw Results                 | 35   |

| 4.2  | 2. Converting Raw Results into PUF IDs        | 36   |

| 4.3  | 3. Mathematical description of PUF properties | 36   |

| 4.4  | 4. Entropy                                    | 43   |

| 5.   | Efficient SR-PUF design                       | 46   |

| 5.1  | 1. Introduction                               | 47   |

| 5.2.  | Motivation                                               | 49  |

|-------|----------------------------------------------------------|-----|

| 5.3.  | Related Work                                             | 49  |

| 5.4.  | Design Methodology                                       | 51  |

| 5.5.  | Bit Generation                                           | 61  |

| 5.6.  | Results                                                  | 63  |

| 5.7.  | Implementation on Zynq SoC                               | 79  |

| 5.8.  | Conclusions                                              | 89  |

| 6. PU | JF design using Programmable Delay Lines                 | 91  |

| 6.1.  | Introduction                                             | 91  |

| 6.2.  | Previous Work                                            | 93  |

| 6.3.  | Implementation Details                                   | 98  |

| 6.4.  | Bit-string generation                                    | 103 |

| 6.5.  | Frequency Analysis                                       | 108 |

| 6.6.  | Conclusion                                               | 114 |

| 7. A  | Comprehensive Set of Schemes for PUF Response Generation | 116 |

| 7.1.  | Introduction                                             | 116 |

| 7.2.  | Previous Work                                            | 117 |

| 7.3.  | PUF Schemes for ID generation                            | 117 |

| 7.4.  | Methodology                                              | 128 |

| 7.5.  | Results                                                  | 131 |

| 7.6.  | Conclusion and Future work                               | 135 |

| 8. Re | esearch Contributions                                    | 138 |

| 8.1.  | Development of new SR-Latch PUF                          | 139 |

| 8.2.  | Development of new RO-PUF                                | 143 |

| 8.3.  | Robustness                                               | 146 |

| 8.4.  | Portability                                              | 147 |

| 8.5.  | Efficiency                                               | 158 |

| 8.6.  | List of Contribution.                                    | 161 |

| 9. Co | onclusions and future work                               | 163 |

| A. Pu | iblications to date                                      | 166 |

| B. Co | ourse Work in PhD program                                | 167 |

|       | vi                                                       |     |

| Bibliography | 168 |

|--------------|-----|

| Biography    | 177 |

# List of Tables

| Table                                                            | Page |

|------------------------------------------------------------------|------|

| 1 Different PUF parameters                                       | 15   |

| 2 PUF advantages and disadvantages                               | 22   |

| 3 Details of dataset for Spartan-6                               | 64   |

| 4 Comparison of results with Yamamoto et al [53]                 | 65   |

| 5 Voltage vs. Intra-chip Hamming Distance for Spartan-6 devices  | 67   |

| 6 Temperature vs. Hamming Distance for Spartan-6 devices         | 69   |

| 7 Effect of external signals on SR-latch for Spartan-6 devices   | 76   |

| 8 Comparison with [53] for Spartan-6 devices                     | 77   |

| 9 Data set for Zynq-7010                                         | 82   |

| 10 Results of Zynq-7010                                          | 82   |

| 11 Voltage vs. Intra-chip Hamming Distance for Zynq-7010 devices | 83   |

| 12 Temperature vs. Hamming Distance for Zynq-7010                | 86   |

| 13 Implementation details of PUF                                 | 88   |

| 14 Results of SR-Latch PUF                                       | 89   |

| 15 Area requirements of our design                               | 97   |

| 16 Details of dataset                                            | 106  |

| 17 Comparison with Maiti et al [34]                              | 107  |

| 18 Properties of independent strong bits                             | 108 |

|----------------------------------------------------------------------|-----|

| 19 Properties of Random with-in die variation normalized over F(0,0) | 114 |

| 20 Details of dataset                                                | 131 |

| 21 Zynq data                                                         | 131 |

| 22 Spartan-6 Data                                                    | 132 |

| 23 Spartan-3 data set                                                | 132 |

| 24 Comparing the neighboring components (CNC)                        | 133 |

| 25 Pairwise Comparison (PC)                                          | 133 |

| 26 Binary Lehmar-Gray (BLG) encoding                                 | 134 |

| 27 S-ArbRO-2 scheme                                                  | 134 |

| 28 Identity Mapping scheme                                           | 134 |

| 29 Advantages of our SR-Latch design                                 | 142 |

| 30 Major difference between our design and other designs             | 142 |

| 31 Major difference between our RO-PUF and other designs             | 145 |

| 32 Primitives used for SR-Latch design                               | 155 |

| 33 Functionality of Altera DFF primitive                             | 155 |

| 34 Functionality of Xilinx FDCE primitive                            | 156 |

| 35 Power consumption of PUF (mWatt)                                  | 160 |

| 36 Total Area consumption of PUF (slices)                            | 160 |

# List of Figures

| Figure                                                                         | Page |

|--------------------------------------------------------------------------------|------|

| 1 PUF Types and classifications                                                | 6    |

| 2 Logical circuit of an SRAM PUF (left). Electrical circuit of an SRAM (right) | 7    |

| 3 Schematic circuit of a butterfly PUF cell                                    | 9    |

| 4 Ring oscillator based PUF circuit                                            | 10   |

| 5 Systematic Variation Tuan et al [42]                                         | 12   |

| 6 Arbiter PUF: Arbiter detects faster signal                                   | 14   |

| 7 Arbiter output is based on the speed of two signals                          | 15   |

| 8 Controlled PUF [2]                                                           | 19   |

| 9 RO Frequency variation with aging under T+V stress [36]                      | 21   |

| 10 Implementation diagram for fuzzy extractor [69]                             | 25   |

| 11 Efficient Implementation diagram for fuzzy extractor [61]                   | 25   |

| 12 Dimensions of my proposed research                                          | 26   |

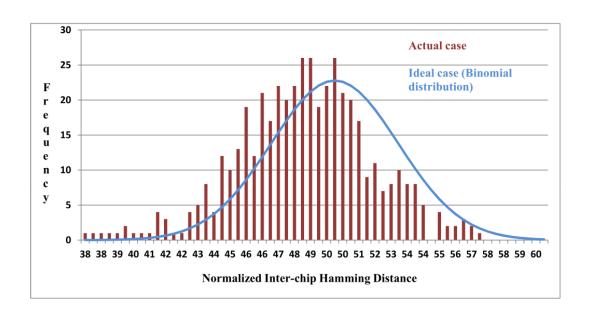

| 13 Normalized Inter-chip Hamming Distance                                      | 37   |

| 14 Normalized Inter chip HD (Average = 49%)                                    | 38   |

| 15 Normalized Intra-chip Hamming Distance                                      | 39   |

| 16 Parameters mapped on the PUF measurement dimension [58]                     | 51   |

| 17 A single SR-Latch design                                                      | 52       |

|----------------------------------------------------------------------------------|----------|

| 18 SR-latch PUF design                                                           | 54       |

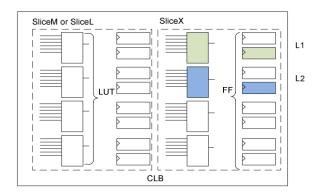

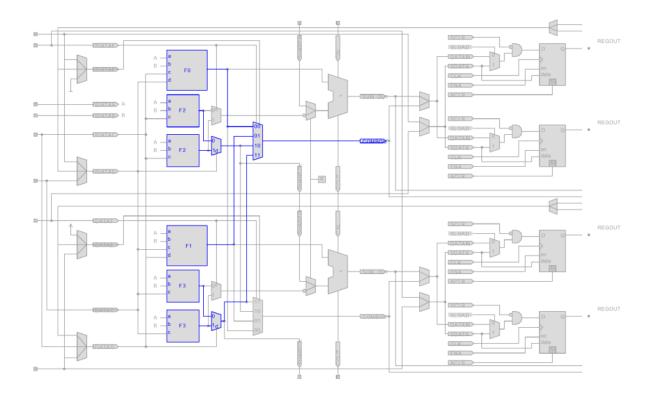

| 19 Layout on FPGA                                                                | 55       |

| 20 Our proposed design: Implementation of 4 SR-latches per CLB                   | 56       |

| 21 Design proposed in [53] for Spartan-6 FPGAs                                   | 57       |

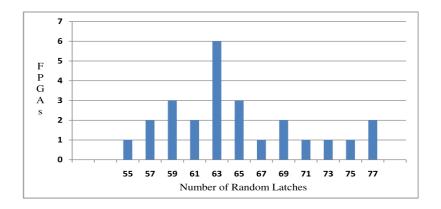

| 22 Single latch implemented per slice. 128 such latches were configured          | 58       |

| 23 Histogram for the number of random latches when a single latch per slice is   |          |

| implemented. This result corresponds to the design from Figure 22                | 58       |

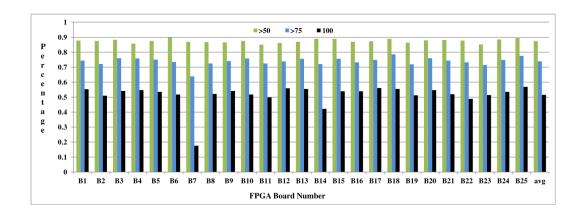

| 24 Proposed design: Percentage of stable latches per board at 1.2V and 25°C. Thi | s result |

| corresponds to the design from Figure 20                                         | 59       |

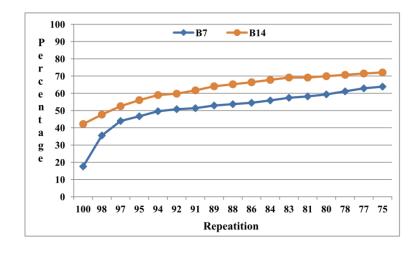

| 25 Stability of two boards                                                       | 59       |

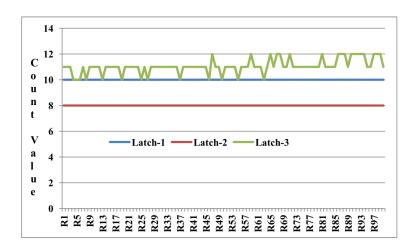

| 26 Count of three latches shown                                                  | 60       |

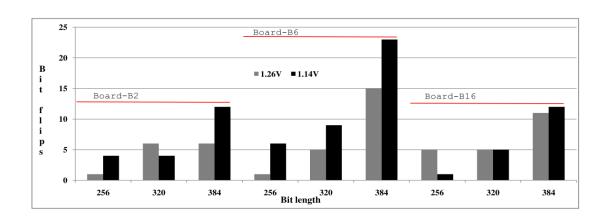

| 27 The number of bit flips vs. the bit length of PUF                             | 60       |

| 28 Normalized inter-chip Hamming distance for Spartan-6 (Mean=49.24%)            | 67       |

| 29 Normalized intra-chip Hamming Distance at 1.26V for Spartan-6 devices.        | 68       |

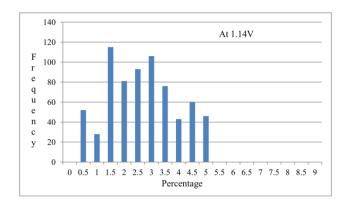

| 30 Normalized intra-chip Hamming Distance at 1.14V for Spartan-6 devices         | 68       |

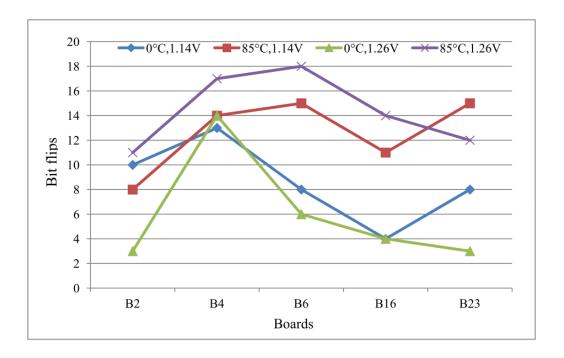

| 31 Bit flips at 1.14V [25°C-85°C] for Spartan-6 devices                          | 71       |

| 32 Error correction scheme A                                                     | 72       |

| 33 Error correction scheme B                                                     | 73       |

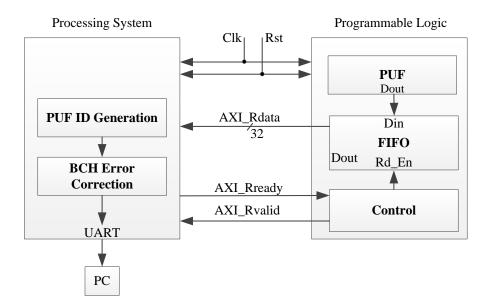

| 34 Interfacing PS of Zynq to PL using AXI-lite protocol implemented on Zynq      | 80       |

| 35 Normalized inter-chip Hamming distance for Zynq-7010 devices                     | 81  |

|-------------------------------------------------------------------------------------|-----|

| 36 Normalized intra-chip Hamming Distance at 1.05V for Zynq-7010                    | 83  |

| 37 Normalized intra-chip Hamming Distance at 0.95V Zynq-7010                        | 84  |

| 38 Absolute values of average relative changes in the metastability counts of latch | nes |

| for the boundary voltage values of 0.95V (negative changes in count values)         | es) |

| and 1.05 (positive changes in count values)                                         | 85  |

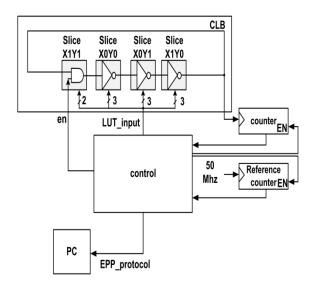

| 39 Single Ring-Oscillator with programmable delay lines                             | 96  |

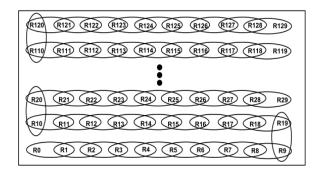

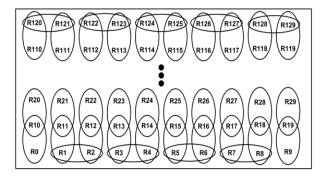

| 40 PUF array configuration of 130 RO on Spartan xc3s100e device                     | 98  |

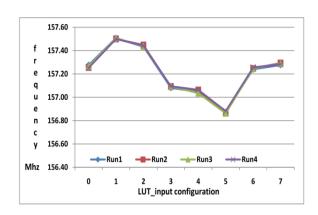

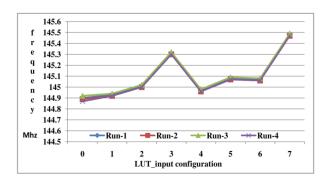

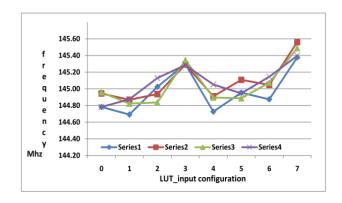

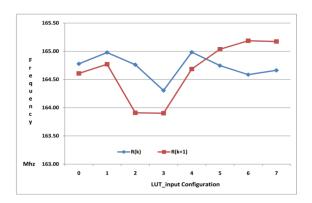

| 41 Frequency distribution due to LUT_input bits variation                           | 99  |

| 42 Characterization time equal to 1 sec                                             | 100 |

| 43 Characterization time equal to 1 msec                                            | 101 |

| 44 Comparison of rings along the rows                                               | 102 |

| 45 The comparison of rings along the columns                                        | 103 |

| 46 Crossover of two rings                                                           | 104 |

| 47 Normalized inter-chip Hamming distance                                           | 105 |

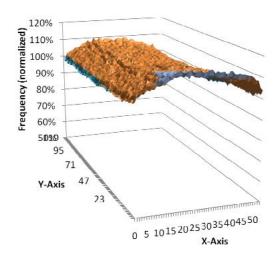

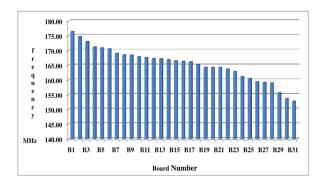

| 48 Average frequency of all ring oscillators located on each board                  | 109 |

| 49 Average standard deviation in frequency of 1040 points per board                 | 110 |

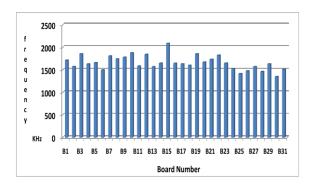

| 50 The average frequency of all boards for 130 Ring oscillators                     | 110 |

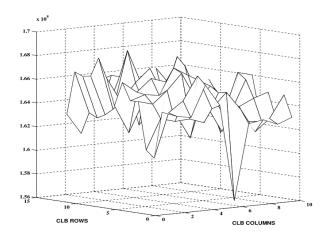

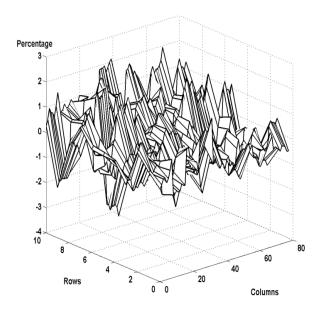

| 51 Random within die variation (normalized over F(0,0), shown as a percentage)      | 113 |

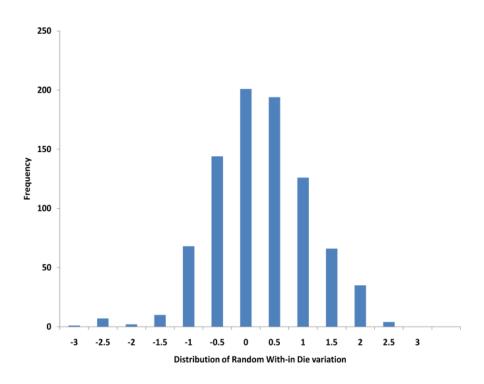

| 52 Distribution of the random within die variation                                  | 115 |

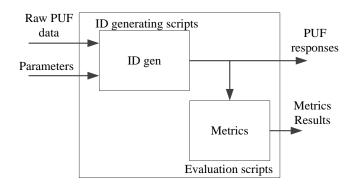

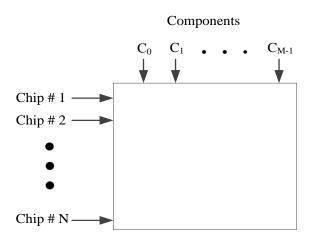

| 53 PUF ID generation and evaluation                                                            | 118      |

|------------------------------------------------------------------------------------------------|----------|

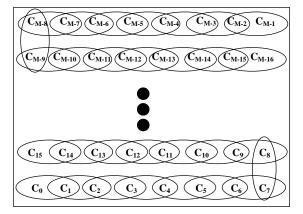

| 54 Comparison of neighboring Components                                                        | 119      |

| 55 Pairwise comparison with neighbors                                                          | 119      |

| 56 Element contains a pair of components                                                       | 123      |

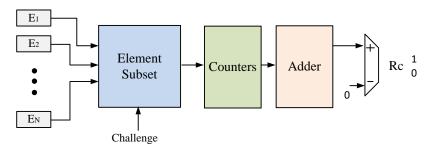

| 57 S-ArbRO-2 showing the relationship between Challenge Response Pairs                         | 125      |

| 58 Data input format for PUF-ID generating scripts                                             | 130      |

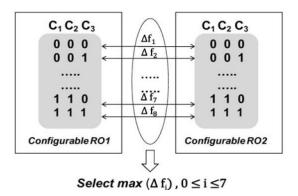

| 59 Selection of the RO-pair with the maximum frequency difference between two configurable ROs | o<br>136 |

| 60 Dimensions of my proposed research                                                          | 138      |

| 61 Single SR-Latch design                                                                      | 140      |

| 62 Placement of four SR-Latches in a Xilinx CLB                                                | 141      |

| 63 Programmable Ring Oscillator (RO) along with the control                                    | 144      |

| 64 Three types of portability                                                                  | 148      |

| 65 Ideal portability directed towards FPGA devices                                             | 150      |

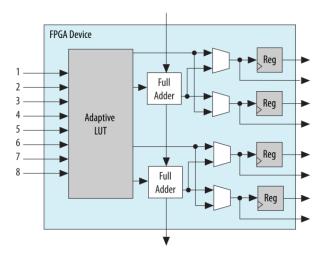

| 66 High level block diagram of Adaptive Logic Module (ALM) in Cyclone                          | 151      |

| 67 Detailed diagram of an ALM in Cyclone V devices                                             | 152      |

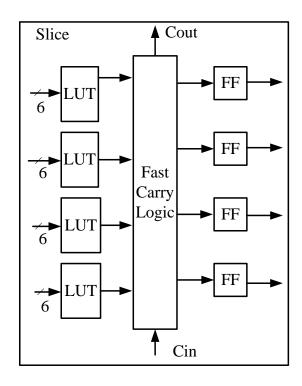

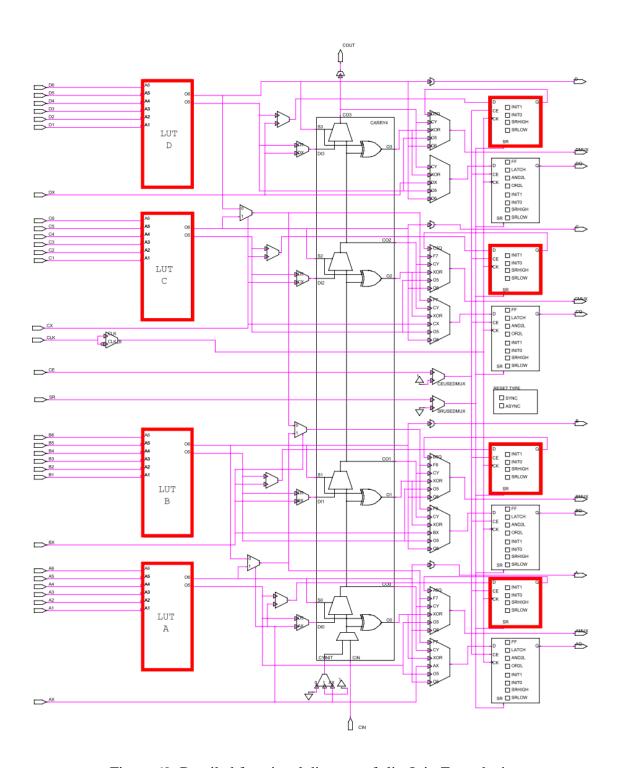

| 68 High level block diagram of Zynq slice                                                      | 153      |

| 69 Detailed functional diagram of sliceL in Zynq devices                                       | 154      |

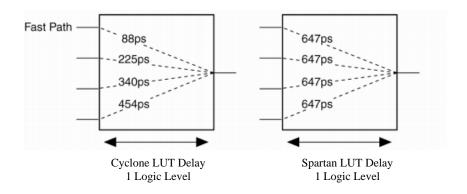

| 70 Propagation delay of Cyclone vs Spartan LUTs                                                | 157      |

Abstract

DESIGN, IMPLEMENTATION AND ANALYSIS OF EFFICIENT FPGA BASED

PHYSICAL UNCLONABLE FUNCTIONS

Bilal Habib, Ph.D.

George Mason University, 2016

Dissertation Director: Dr. Kris Gaj

With the advent of Internet of Things (IoTs), secure communication between devices is a

big challenge. Billions of new devices and sensors are going to be connected to internet.

To ensure secure communication with the devices we need hardware primitives that are

well suited to the requirements of IoTs. Recent research has led to an increased interest in

security measures, especially in solutions that are physically unique and unclonable.

Physical Unclonable Function (PUF) has been found to be a strong candidate for this

purpose. Since PUF extracts the inherent manufacturing variations of a hardware chip,

therefore it can be used as a finger print of devices. Eventually these finger prints can be

used to authenticate devices and also to generate secure keys for cryptographic functions.

This thesis describes the development of efficient and reliable PUF for FPGAs. Novel

PUFs have been designed for this purpose. Furthermore, it also covers the generation and

analysis of PUF responses in a more coherent and systematic method. For the generation

of PUF responses different bit-generation schemes have been used and their results have

been compared with each other. This novel study was done to determine the best scheme among the most popular schemes developed so far by different researchers. Software scripts were developed for all the schemes. Similarly, for the analysis, new metrics have been presented for the evaluation of PUF responses. Additionally, software scripts have been developed for analysis of PUF responses. These scripts can be applied to any type of PUF.

Design, development, implementation and testing of two major types of PUF have been carried out. One is a memory based PUF: SR-Latch based design. The second is a delay based PUF: Ring oscillator based design. Both designs have been thoroughly tested on FPGA devices. Performance metrics of both designs have been presented and compared to the state of the art PUFs. Experiments were carried out on different FPGA technologies. It was done to prove the applicability and portability of our designs.

One of the major requirements of PUF intended for IoT applications is that the device area must be efficiently utilized. The current state of the art PUFs are expensive for low area implementation. Therefore, in this work a highly efficient PUF has been developed and tested for FPGAs. Additionally, the PUF is very reliable for use at different environmental conditions. It makes it further attractive because the device can be used in broad range of temperature and voltage variations. To regenerate the same PUF response under different conditions we used the error correction scheme. We also presented different schemes that are suitable from the security point of view.

Lastly we presented a prototype of an efficient SR-Latch based PUF design, with two times improvement in area over the state of the art, thus making it very attractive for low-area designs. This PUF is able to reliably generate a 128-bit cryptographic key.

#### 1. Introduction

Physical Unclonable Functions (PUFs) are physical primitives which produce unclonable and device-specific measurements of silicon Integrated Circuits (ICs). These measurements are then processed to generate device IDs or Keys. It is very similar to the biometric feature extraction of humans. These features can be used for authentication and identification purposes. In ICs, manufacturing process variations results in physical uniqueness due to sub-microscopic level differences. Even with extreme precision, the two ICs manufactured under same conditions cannot have similar features. Thus manufacturer cannot control the development of these features during the manufacturing process. Due to this property the term 'unclonability' is used to describe it. The extraction of these IC specific features is carried out by using different PUF designs. The primary goal of any PUF construction is to extract these features cleanly and reliably. The process of extraction and the subsequent measurements must not be affected by any environmental conditions like voltage, temperature and radiation. It must be mentioned that in humans the biometric features cannot be acquired and they are 'inherent', similarly in ICs the sub-microscopic level features cannot be developed or grown on the IC fabric after the manufacturing process is complete. A common setting in which these physical primitives are used is to apply a stimulus and measure the response. The response of this primitive can be interpreted as the result of evaluating a function. Since this function is similar to mathematical functions, therefore these functions are referred as Physical Unclonable Functions. Due to the cryptographic setting in which PUFs are used, stimulus and response are called Challenge Response Pair (CRP).

Among other uses, PUFs enable device identification and authentication [9, 29], binding software to hardware platforms [12, 16, 21, and 41] and secure storage of cryptographic secrets [5, 4]. Furthermore, PUFs can be integrated into cryptographic algorithms [22], remote attestation protocols [43] or countering reverse engineering [60]. Today, PUF-based security products are already announced for the market, mainly targeting IP-protection, anti-counterfeiting and RFID applications [63, 64].

#### 1.1. Motivation

In the last couple of decades there has been an exponential increase in the digital information processing and communication systems. With this phenomenal increase, security challenges are becoming significant. An on-chip PUF (Physical Unclonable Function) can solve these challenges effectively and efficiently. A PUF is a chip-dependant unclonable challenge-response function that can be used to uniquely identify a specific integrated circuit. Furthermore, the PUF itself is tamper resistant against physically invasive attacks. Due to these attributes, a PUF offers security against intellectual property (IP) theft and counterfeiting, and solves issues such as chip authentication, reverse engineering, trusted computing, and secure key generation. The motivation for FPGA based PUF comes from the fact that FPGAs as opposed to ASICs offer a flexible and secure

solution to IP implementations in hardware. The reason for this flexibility is because FPGAs can be configured at any time in the field without any cost associated with it. Similarly FPGAs can offer secure IP implementation. In a practical application, the IP reads the PUF output and compares it with some built-in constant (chip-ID) and if both of them match then it enables the IP to run on this particular FPGA device. This way the IP vendor makes sure that the IP is licensed only for a selected device. The chip ID can be retrieved by the manufacturer during enrollment. Furthermore PUFs can be employed to verify if the system having an FPGA as one component which came from a genuine source. This can be done by extracting the chip-dependent PUF output in the field and comparing it with the one supplied by a genuine source. Another motivation of FPGA based PUFs is that FPGAs offer quick product customization as per market demands compared to ASIC, therefore it is important to investigate the security features of FPGA based PUF designs.

#### 2. Previous Work

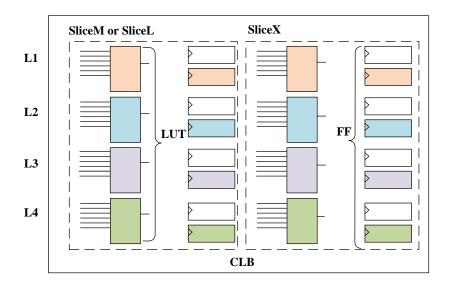

Initially the term PUF was proposed by Pappu et al in [1]. Since 2002, silicon based PUFs have been extensively investigated. The initial proposal of a delay based arbiter PUF was made in [2]. Arbiter PUF was further explored by [3, 4, and 7] to investigate reliability and security features. Although the Arbiter-PUF offers strong PUF properties, it is prone to machine-learning attacks [49]. In [5], the robustness of optical PUF is proposed. PUF based secure processor is presented in [6]. In [9], the unclonability of PUF based RFID tags is investigated. In addition, a security protocol for RFID tags is also presented. In [11], the idea of a Ring-Oscillator (RO) based PUF is presented. In this PUF the challenge is the selection of a pair of ROs. The response is the one-bit comparison result of the frequencies of those ROs. A large-scale characterization of RO based PUF has been done in [23]. In [10] the first SRAM-PUF is presented, in which the start-up values of uninitialized Embedded RAMs are used as a PUF response. From 2008-2013, FPGAs produced by Xilinx and Altera, the start-up values of memory locations were controlled by the chip manufacturer, which rendered SRAM PUF useless for FPGAs. It must be mentioned that in new 28nm (Zynq) FPGAs, SRAM PUF can be employed by using the techniques of power gating [66]. In this technique the Block RAM of FPGA is disconnected from the power line of chip. In [16], Butterfly-PUF is presented, which requires symmetric paths between registers for causing metastability. FPGA tools do not offer complete access to

symmetric design at the wire level, therefore, routing schemes make it hard to achieve symmetric butterfly design on FPGAs. This fact has been verified by [27] for both Arbiter and Butterfly PUF. In [30] and [39], the concept of programmable delay lines is presented, in which the LUT delays are used to create a metastable condition which is further used to develop a PUF and TRNG respectively. In [34], Maiti et al. presented an RO PUF, in which multiplexers were introduced in the ring to select different paths inside the ring. In [37], the number of configurations of ring oscillator has been improved by introducing a latch in the path of a ring, making it impossible to compare a latch-path with no-latch-path. In addition to RO PUF, extensive research has been done to investigate the Latch PUF. In [38], an Error Correction Code (ECC) encoder and decoder have been developed for PUF based light weight applications. In [44] and [53] it has been revealed that robust responses from SR-Latch based PUF can be derived. In Latch PUF, the set reset latch is triggered into a metastable state. After some time the latch stables into a particular state. The response bit is based on the stable state of the SR-Latch. In [44], the response bits are derived from the location of the random latches. Bitline PUF has been proposed in [62]. It is an extension of SRAM PUF. In [67] the interface for secure PUF has been described.

# 2.1. Types of PUFs

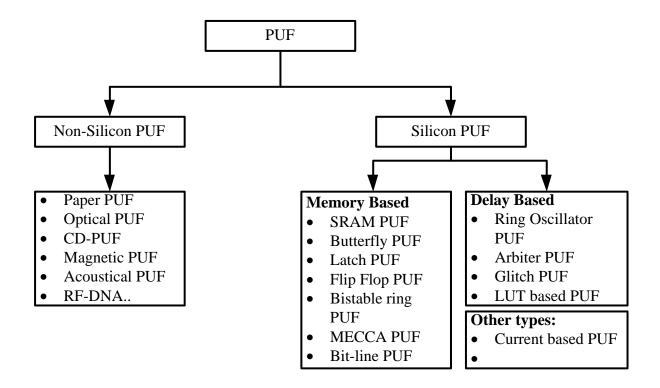

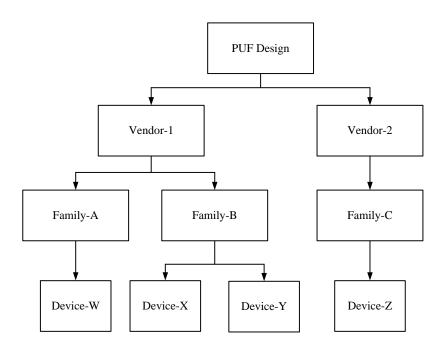

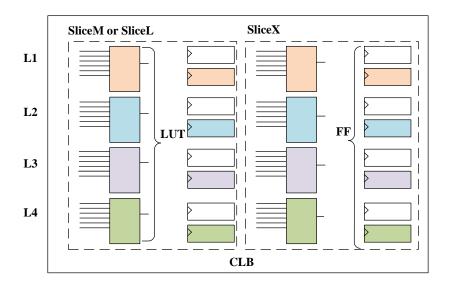

Fig. 1 shows the types and sub-types of different PUF designs.

Figure 1: PUF Types and classifications

### a) SRAM-based PUF

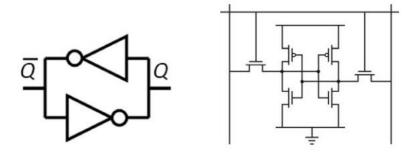

It was initially proposed by Guajardo et al. [10], the SRAM-based PUF uses the initialization values of dedicated SRAM blocks. They consider a range of memory

locations as challenges and start-up values at these locations as responses. These values depend on the small asymmetry between two cross-coupled inverters Fig. 2, ensuring that the start-up values will always be the same with high probability. Guajardo et al. defined this kind of PUF as intrinsic, because the PUF generating circuit is directly present in the design to protect. The main drawback of SRAM-based PUF with FPGAs is that most FPGA manufacturers initialize the embedded memory blocks to zero before loading the bitstream to avoid shortcuts in the reconfigurable circuitry. It must be added that SRAM PUF has been adopted by Microsemi and Altera [72] in their devices.

Figure 2: Logical circuit of an SRAM PUF (left). Electrical circuit of an SRAM cell (right) in CMOS [28].

#### b) Flip-flop PUF

It was proposed by Maes et al. [18], the flip-flop PUF uses flip-flops start-up values as responses similarly to the SRAM-based PUF. Maes et al. imagined this PUF because it is possible to prevent flip-flops from being reset. Hence, this allows having an efficient PUF suitable for every FPGA.

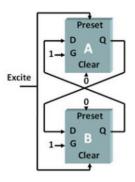

## c) Butterfly PUF

It was proposed by Kumar et al. [16], the Butterfly PUF is another solution to overcome the SRAM PUF reset drawback. It consists in two cross-coupled latches initialized with two different values to have an unstable operating point. The latches are initialized on an external signal. When this one is released, the stable state depends on the slight differences between the connecting wires which are designed using symmetrical paths on the FPGA matrix. The Butterfly PUF needs manual routing to have symmetric paths and its performance highly depends on the targeted FPGA [51]. In Fig. 3, two cross coupled latches are shown.

Figure 3: Schematic circuit of a butterfly PUF cell

#### d) MECCA PUF

Proposed in 2011 by Krishna et al [45]. In this PUF the write failure in SRAM memory cells is caused. It results into a data being written in the SRAM memory which is dependent on the chip. MECCA PUF has not been implemented on the real chip and the results come only from the simulation.

#### e) LUT-based PUF

It was proposed by Anderson [31], the LUT-based PUF harnesses the FPGA's LUT structure. It uses LUTs from the same basic logic block (slice or ALM), configured in shift-register, and the carry-chain logic. This PUF relies on delays introduced by the LUTs and the multiplexers. It uses the presence or absence of glitches along the carry chain to determine the output bit. This PUF has the advantage to be completely described in HDL.

#### f) Ring oscillator PUF

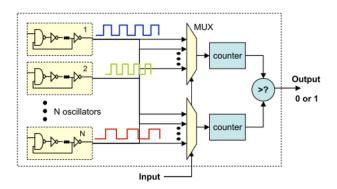

It was introduced by Suh et al. [11], it mainly relies on a self-oscillating circuit and a counter. The ring oscillator produces an oscillating signal with a delay-dependent frequency. Besides, the counter measures the number of positive edges over a period of time. The obtained value is a good representation of the ring oscillator intrinsic delay. The main drawbacks of this kind of PUF are the limited number of possible challenges and the significant dynamic power consumption. The input is the selection of a pair of oscillators while the output is the one bit result after comparing their frequencies as shown in Fig. 4.

Figure 4: Ring oscillator based PUF circuit

#### Classification into Strong and Weak PUF

PUFs can be divided into strong PUFs and weak PUFs. The strong PUF includes the optical PUF, arbiter PUF, lightweight secure PUF, etc. The weak PUF mainly includes the memory-based PUF, RO PUF and glitch PUF. The security of strong PUFs is based on their high entropy content providing a huge number of unique challenge-response pairs (CRPs), which can be used in authentication protocols. On the other hand, weak PUFs exhibit only a small number of CRPs to be applied. Although they are not applicable to authentication protocols, the corresponding responses of weak PUFs can be used as a device unique key or seed for conventional encryption systems, while maintaining the advantages of physical unclonability. In order to enable the extraction of cryptographic keys from PUFs, the fuzzy extractor [17] is necessary. In [14], fuzzy extractor has been implemented on FPGA to generate cryptographic keys.

Issues associated with Ring Oscillators

#### Systematic Variation

The frequency of RO PUF is dependent on the location of RO. In [8 and 34] it has been shown that the frequency of rings at the middle of a chip is higher than the rings located at the edges of the chip. This behavior is called 'Systematic Variation'. Fig. 5 shows this behavior. The solution proposed by Maiti et al in [34], is that while comparing the frequencies of two ring oscillators, care must be taken because too far rings will have known results from frequency comparison. They proposed to compare only the neighboring ring oscillators. In this way the effect of Systematic variation will be minimal.

Figure 5: Systematic Variation Tuan et al [42]

#### • Dependence on Voltage

The frequency of rings is highly dependent on the voltage supplied at the core of FPGA.

These two values are directly related with each other. This problem can be solved by using the PUF only at the rated voltage.

#### • Dependence on Temperature

The temperature and frequency of rings have inversely relationship with each other. Qu et al have proposed a method of 'Temperature Aware Rings co-operation' in [20]. With this method, 80% more rings can be used to generate a reliable bit.

#### Locking of Rings

Costea et al [33] showed that rings can lock with other, resulting in exhibition of same frequency when allowed to oscillate. This locking behavior occurs if two rings are

implemented very close to each other inside the FPGA fabric and if they are allowed to oscillate at the same time. This problem can be solved by running only one ring to oscillate at any particular time. Or two rings should not share the same resources like switch boxes inside CLB.

#### • Implementation Size

The number of CRPs scales linearly with implementation size of regular RO-PUF. Therefore number of rings implemented are bounded by the logical resources available in FPGAs.

New Directions and Improvements

The following are the improvements reported for RO-PUF.

- a) Increasing the CR space: Maiti et al proposed that the challenge Response pairs of RO-PUF can be increased by using the Identity mapping functions.

- b) Ganta et al proposed the concept of S-ArbRO. In S-ArbRO the CRP or RO PUF have been increased by integrating Arbiter PUF with RO PUF.

- c) In [24], circuit level techniques have been proposed to improve the reliability of RO

PUF. This technique is based on using the transistors in forward body bias.

- d) In [32], it has been shown that the quality of RO PUF improves when ROs are enabled for longer duration. Additionally if ROs are placed and compared in a chain like mode then the quality metrics improves. It is also shown that surrounding logic badly affects

the frequency of ROs. We have also discovered this phenomenon in our investigation of RO PUF.

e) In [65], composite PUF has been proposed. The main advantage is the higher number of CRPs.

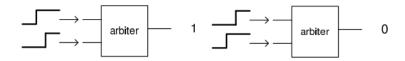

#### g) Arbiter PUF

In Arbiter PUF two path are applied a low to high signal as shown in the Fig. 6. At the end of these paths there is an arbiter which decides the fastest path. A corresponding binary value is generated as an output by the arbiter. The challenge is the select line for multiplexers. Therefore if n multiplexers are employed then the total CRPs are  $2^n$ . Arbiter is usually a D-flip flop. The two inputs for this flip flop are connected to the clock and data signal. As shown in Fig. 7, the output of an arbiter is based on the speed of input signals.

In [47], it has been shown that arbiter PUF has very low entropy when implemented on ASIC. Additionally it is prone to model building attacks [49].

Figure 6: Arbiter PUF: Arbiter detects faster signal

Figure 7: Arbiter output is based on the speed of two signals

#### h) Time-bounded PUF

It was introduced by Majzoobi et al., the time-bounded PUF relies on three flip-flops placed around the circuit under test (CUT): The Launch FF, the Sample FF, and the Capture FF. Initially, the flip-flops are set to zero. Then, the Launch FF is set to one on the rising edge of the clock. This signal propagates through the CUT and is sampled by the Sample FF on the falling edge of the clock. The CUT adds a challenge-dependent delay which may be greater than the half of the clock period. Hence, the sampled value depends on it and is xor-ed with the true launched value to be captured by the Capture FF.

#### i) Current based PUF

Proposed in 2011 by Majzoobi et al [40], it uses CMOS transistor leakage currents instead of delays and a sense amplifier instead of arbiter to implement a linear Strong PUF structure.

#### 2.2. Properties of PUF

For the evaluation of PUF, certain properties have been devised. These properties are based on statistical measures.

Table 1: Different PUF parameters

|                    | Uniformity                       |

|--------------------|----------------------------------|

| Moiti at al [50]   | Bit-aliasing                     |

| Maiti et al [58]   | Uniqueness                       |

|                    | Reliability                      |

|                    | Randomness                       |

|                    | Steadiness                       |

| Hori et al [26]    | Correctness                      |

|                    | Diffuseness                      |

|                    | Uniqueness                       |

| Habib et al [73]   | Worse case Uniqueness            |

| Tradio et ar [73]  | Worse case Reliability           |

| Su et al [13]      | Probability of Misidentification |

| Majaabi at al[15]  | Single-bit Probability           |

| Majoobi et al[15]  | Conditional Probability          |

| Yamamoto et al[44] | Variety                          |

## 2.3. Target Applications

PUF structure is incorporated in the silicon devices for targeting two major applications. First one is the *identification* of silicon devices and another one is secure key generation for cryptographic functions. In the case of identification, the silicon devices go through the process of enrolment. In this step, challenge response pairs (CRP) are generated and then stored in the database. This step is carried out at room temperature and nominal voltage. Once these devices reach the users in the field, the device PUF response is again generated. It is like a fingerprint used for human identification. If this PUF response is equivalent to the response stored in the database, the devices are identical, otherwise they are different. Since we do not know the operational conditions in the field, therefore a PUF is said to be reliable if it can generate the same response even if the operating conditions, namely

voltage and temperature, are changed. Similarly, the response of PUF should be unique, so that the responses of any two devices are substantially different. Additionally the number of CRPs should be huge for this application. Another major application of PUF is the generation of *keys* for cryptographic functions. The minimal requirements for a secure key generation and storage are: A) a source of randomness to ensure that generated keys are unique and unpredictable, and B) Keys are secure and reproducible. A PUF-based key generator tries to take care of both requirements at the same time by using a PUF to harvest static but device-unique randomness, and by processing it into a cryptographic key. It also avoids the need for a protected non-volatile memory to store the key. Since we know that key must be reproducible, therefore error correction schemes are employed to regenerate the key reliably in the field.

#### 2.4. Attacks

PUF prevents the attacker from revealing the underlying device specific secrets associated with FPGAs. There are several types of attacks that can be carried out against PUF circuits.

#### Replay attack

If the adversary has physical access to PUF device and records the challenge Response pairs, then the adversary can fake the PUF by using the known CRPs. It can be thwarted by employing a PUF that has unlimited number of Challenge Response Pairs and using a new CRP every time. However, FPGAs have limited resources and it is impossible to build a circuit that has unlimited number of CRPs.

#### Active attack

This attack can be invasive or non-Invasive. In case of Invasive attack an adversary tries to use Laser beams or ion beam to study the physical structure of PUF. It may permanently damage the PUF. Therefore the PUF secrets are not tempered. Till now, there has been no invasive attack reported in literature.

In case of non-Invasive attack the adversary tries to disrupt the challenge response behavior of PUF. For this purposes, the temperature or voltage are varied.

#### Passive attack

The adversary uses the side-channel analysis to determine the relationship between the PUF circuit and the voltage variation or power consumption.

#### Modeling attack

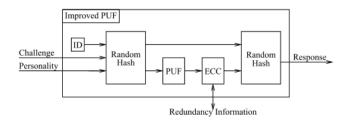

In modeling attack the adversary develops a mathematical model for the underlying PUF. This can be done by knowing the challenge response pairs of a PUF. Successful modeling attacks have been reported for Arbiter PUF [49]. It can be prevented by employing a PUF circuit that has true random outputs for corresponding inputs. It implies that there is no relationship between two challenge response pairs.

#### Chosen Challenge Attack

In this attack an adversary can select the desired challenges and model the relationship between challenges and responses. To thwart this attack Controlled PUF [2, 25] has been introduced. In these designs hash functions are employed at the input

and output of PUF. Thus breaking the link between input and output of a PUF as shown in the Fig. 8.

Figure 8: Controlled PUF [2]

#### • Cloning attack

In this attack an adversary will make the exact copy or clone of a PUF. It is assumed that the clone and the original circuit will have same Challenge Response Pairs (CRPs). Recently, Helfmeier et al. [52] demonstrated the first successful physical cloning of an SRAM PUF based on the fact that SRAM cells emit near infrared light when it is read and the cell's power-up value can be obtained from the emitted light. Hence, SRAM PUFs are not well suited as secure PUFs. Cloning other PUFs such as RO PUFs or SR-Latch PUFs have not been reported to this date. Therefore, both PUFs are still considered unclonable.

## • Reverse Engineering attack

It is like a passive attack. In [60] Gate-level characterization (GLC) technique has been used to measure and extract the gate-level physical properties, such as threshold voltage and effective channel length.

## 2.5. Challenges

### Portability

When PUF design is implemented on different FPGA platforms, the results are not always similar. The robustness and efficiency metrics vary depending on the FPGA technology used. Currently there is no literature available to describe the effects of FPGA technology on the final PUF output. We observed this behavior when similar Ring Oscillator (RO) PUF was implemented on Spartan-3e (90 nm) devices and then on Spartan-6 (45 nm) devices. The uniqueness and reliability were found to be significantly different. However, care must be taken to ensure that this comparison is not affected by the external FPGA circuit like the noise present in the voltage regulator or the variations due to temperature. In addition, aging affects must also be considered during this evaluation.

In this research we implemented same type of PUF on different FPGA families. We presented our results to demonstrate the extent of portability.

### Aging effect

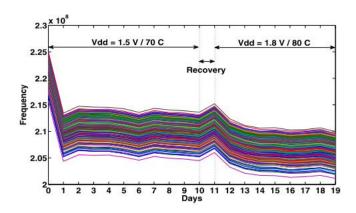

The PUF circuit behaves differently on the similar devices due to the aging effect. This phenomenon has been investigated in [36] for RO PUF. In Fig. 9, the affect of aging on RO frequency has been shown. This problem has been addressed in [59] for RO PUF.

Figure 9: RO Frequency variation with aging under T+V stress [36]

However, in depth analysis and investigation needs to be carried out for other PUF designs especially the memory based PUF.

# Weak points of different PUF designs

Apart from the Ageing and Portability, there are other pros and cons of PUFs. These are based on the individual type or subtype of PUF design. They are listed in the Table below.

Table 2: PUF advantages and disadvantages

| PUF    | Subcategory | Diag desaute and    |  |

|--------|-------------|---------------------|--|

| Туре   | PUF Type    | Disadvantages       |  |

|        | SRAM        | Cannot be used in   |  |

|        |             | Altera and Xilinx   |  |

|        |             | FPGAs, because      |  |

|        |             | start-up values are |  |

|        |             | controlled.         |  |

| Memory | D flip flop | Cannot be used in   |  |

| Based  |             | Altera and Xilinx   |  |

|        |             | FPGAs, because      |  |

|        |             | start-up values are |  |

|        |             | controlled.         |  |

|        | Butterfly   | Not recommended     |  |

|        |             | for FPGAs           |  |

|                |                    | Design has not      |

|----------------|--------------------|---------------------|

|                | Mecca              | been reported to be |

|                |                    | implemented in      |

|                |                    | practice yet, which |

|                |                    | presents a further  |

|                |                    | risk in developing  |

|                |                    | a solution          |

| Delay<br>Based | Arbiter            | Prone to modeling   |

|                |                    | attacks             |

|                | Ring<br>oscillator | Expensive, since    |

|                |                    | the number of rings |

|                |                    | required is large.  |

|                | S-ArbRO            | Systematic          |

|                |                    | variation can       |

|                |                    | influence PUF       |

|                |                    | output, if          |

|                |                    | physically farther  |

|                |                    | rings are compared  |

#### 2.6. General Error Correction

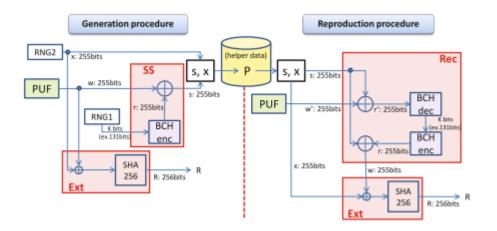

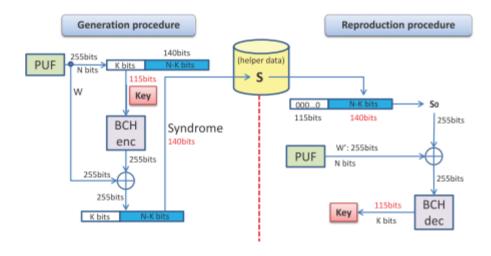

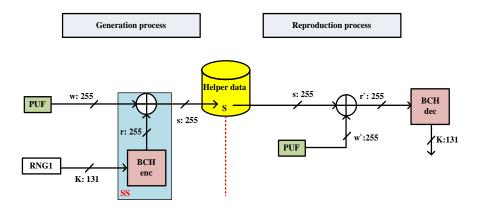

The output of PUF in the field is affected by noise. For reliability purposes the noisy bits have to be corrected. For this purpose error correction schemes are employed. One of the well known schemes used for this purpose is called Fuzzy extraction. It was proposed by Dodis et al in [17]. More recently Kang et al proposed error correction schemes for PUF in [61, 69]. This scheme consists of two steps: Generation and Reproduction as shown in the Fig. 10.

In the generation, PUF bits are generated at the room temperature and nominal voltage. These bits are then encoded using BCH encoder. The encoded bits are stored in a database as helper data. In the reproduction step, the noisy PUF bits are generated in the field. The same helper data is used to correct the noisy bits. It is done using BCH decoder. In this process, some information is leaked to the adversary in the form of helper data.

A more efficient implementation scheme for PUF error correction has been proposed in [61]. It is shown in Fig. 11,

Figure 10: Implementation diagram for fuzzy extractor [69]

Figure 11: Efficient Implementation diagram for fuzzy extractor [61]

As shown in the above figure, hash function is removed. It results into considerable improvement in area and speed of error correction scheme.

## 3. Goals and Contributions

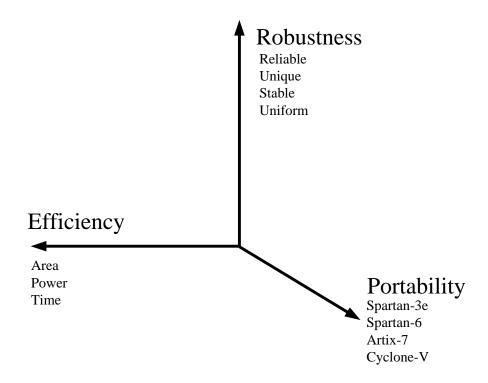

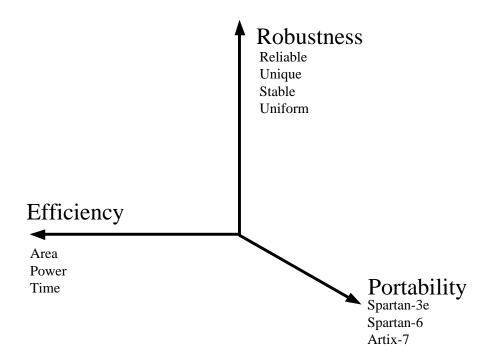

My research goal was primarily focused on three areas of PUF space. These areas are shown below in Fig. 12.

Figure 12: Dimensions of my proposed research

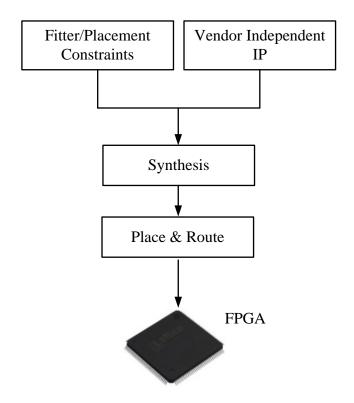

As evident from the above figure the three main areas of PUF space are: Robustness, Efficiency and Portability. My research goal was to develop a PUF that is Robust, Efficient and Portable at the same time. Robustness means that it should be able to generate a response that is unique, uniform and highly reliable. Portable means that it should be easily ported to FPGAs of different families and types. Efficiency means that our design should consume less power, area and time. We have to integrate all three dimensions while developing a PUF based system. Ignoring any one of them will seriously affect the quality of PUF. To comprehensively cover the PUF space we planned to develop two new types of PUFs. One is memory based and the other is delay based PUF. In the memory based PUF we planned to investigate an SR-Latch design. Similarly in the delay based PUF the goal was to develop a new RO-PUF design. Both designs are briefly explained in section 3.1 and 3.2 respectively. The dimensions of PUF space namely Robustness, Efficiency and Portability are covered in section 3.3 to 3.5.

### 3.1. Development of new SR-Latch PUF

The state of the art SR-Latch PUF [44, 53] is very expensive from area point of view. It requires 2 CLBs of an FPGA to generate a single bit of PUF response. It is prone to the affect of nearby logic. Thus the reliability of PUF bit is severely affected if the tool configures the same CLB with external logic. In our proposed design we solved this problem by utilizing all the logic resources of a latch CLBs. Thus latch is not affected by the nearby logic.

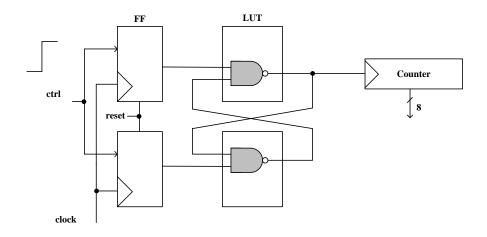

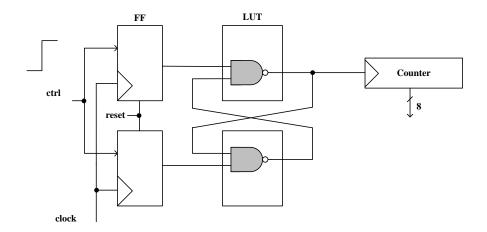

Our design approach is based on determining the length of metastable state. We trigger the latch into a metastable state. During the metastable state, oscillations are generated by the latch and the counter counts it. The duration of metastable state of a latch is based on the inherent manufacturing variation. Thus entropy harvested is based on the manufacturing variation. Strong latches are selected for bit generation, the remaining latches are discarded. A latch is regarded as a strong one, if it repeats for the same duration of oscillation during metastable state. Once strong latches are determined, then PUF response bits are generated by comparing the number of oscillations of strong latches.

To achieve area efficiency we configured more latches per CLB. With our design we utilized all the LUTs available inside a CLB, thus achieving a 100% LUTs efficiency. We compared our design with the state of the art [53]. In depth details of SR-Latch PUF have been covered in chapter 5.

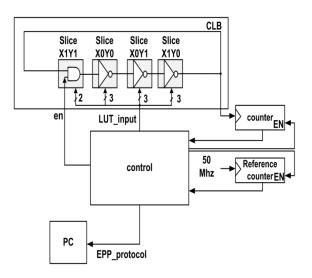

## 3.2. Development of new RO-PUF

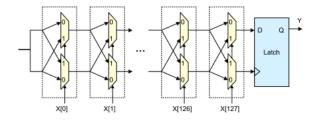

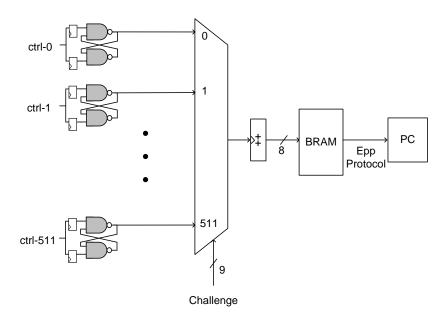

We developed a novel FPGA friendly Ring Oscillator (RO) based Physical Unclonable Function (PUF). In this design the internal variations of FPGA Look-Up Tables (LUTs) are exploited to generate a PUF response. Statistical tests were performed to study the strength of this PUF. Moreover, stability is compared with the state of the art reported in literature to date. Our design has been tested on 31 Spartan-3e devices and the results are promising. Furthermore, we also analyzed the frequencies to extract the random variation offered by our design.

In our design each RO is made from a single AND gate and three inverters. It uses one LUT for an AND gate and three LUTs for inverters. We used one LUT-input to connect in a ring, while the remaining LUT-inputs are varied in order to generate programmable delays. We compare our design with the state of the art design [34]. In depth details of our RO-PUF design are covered in chapter 6.

#### 3.3. Robustness

Robustness deals with the ability of the PUF to exhibit 'reliable', 'unique' and 'uniform' responses. In our experiments, we compared our results with the state of the art.

We developed a reliable and efficient SR-latch PUF in this work and compared the results to the state of the art implementation. A novel method of mode calculation is used to determine strong latches. The derived design has been verified on 25 Xilinx Spartan-6 FPGAs (XC6SLX16) and 10 Xilinx Zynq SoC (XC7Z010) devices. The uniqueness is close to the ideal value of 50%. We also did the entropy analysis. We calculated bit-dependent bias entropy bound based on PUF responses of 25 Spartan-6 FPGAs. We proposed two error correcting schemes for our PUF design. It was shown that the bit flips at extreme voltage and temperature were in the range of our proposed error correction schemes.

Additionally, we developed new matrices to analyze the quality of PUF. Software based Python scripts were developed to generate the PUF IDs using different schemes and then

analyze the result. This software tool can be used for any type of PUF. Furthermore, the tool has been made available for research community. It is freely available at [74].

## 3.4. Portability

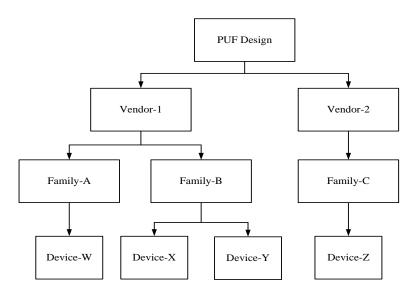

Portability of PUF design means that different FPGA devices can be configured with the same design. These devices may belong to different FPGA vendors. Similarly devices may belong to same vendor but different families. Lastly devices may belong to the same family of a particular vendor. These three levels of portability can be explained with the following figure,

Figure 12: Types of Portability

As shown above, the three types of portability are,

## 1) Intra-Family portability

In this case devices belong to the same family of a particular vendor. As shown above XY shows this type of portability.

### 2) Inter-Family portability

In this case devices from same vendor are used. In the above figure WX shows this type of portability. These devices belong to two different families of Xilinx. We chose Spartan-6 and Zynq devices for this experiment.

#### 3) Inter-Vendor portability

In this case devices belong to two different vendors. As shown above YZ shows this type of portability. We chose Zynq devices from Xilinx and Cyclone devices from Altera for this experiment.

The goal of this study will be to determine the challenges faced to achieve the three types of portability.

## 3.5. Efficiency

Efficiency deals with the area consumption of the design, the total power consumed by it and finally the time to calculate the PUF response.

Actual Power is equal to the power consumed by the FPGA device during the generation of PUF response bits. Area is calculated by the tool and this information can be easily extracted from the mapping report generated by tools. It is determined in terms of slice counts in FPGAs. Characterization time for RO PUF is calculated from the following equation,

The total characterization time = (# of components · enable\_time)/ (board\_frequency)

Where enable\_time is the duration in which each component is allowed to run freely.

Changing the efficiency metrics severely affects the quality of PUF. For example, in order to save the PUF area, if two rings oscillators are implemented inside a single CLB (Configurable Logic Block). Then due to the proximity of a neighboring ring, the frequency of two rings might lock with each other. It means that two rings will oscillate with same frequency. Similarly, in order to generate the PUF response quicker, if the characterization time of a ring is reduced, then the frequency of rings is severely affected. It will result into a very unreliable PUF response bit.

In case of SR-latch PUF when external logic is allowed to configure the latch CLB then the number of counts are badly affected by the external logic. It implies that care need to be taken while reducing the area of a SR-latch PUF.

We developed SR-Latch PUF that is 2x smaller and is more reliable than the state of the art design. To conserve less power, we enable the PUF components only when the PUF-

ID is required. There are no free running, ROs or SR-Latches. Our design generates the PUF-ID in a reasonable time of ~5sec.

#### 3.6. List of Contribution

- Design of a novel memory based PUF for FPGAs.

- SR-Latch PUF is 2x smaller in area than the state of art.

- SR-Latch PUF is more reliable than the state of art.

- SR-Latch uniqueness measure is comparable to the state of the art.

- Validated on Spartan-6 and Zynq FPGAs.

- Design of a novel delay based PUF for FPGAs.

- Due to the programmable nature of our RO-PUF, we can generate 2x more bits than the traditional RO-PUF. It implies our PUF requires less chip area to generate the same number of PUF response bits.

- The uniqueness and uniformity measures of our RO-PUF responses are comparable to the ideal case.

- The design has been validated on Spartan-3 FPGAs.

- Frequency analysis of RO components.

- Determination of systematic and manufacturing variations.

- Implementation and evaluation of PUF architectures on multiple FPGA and SoC platforms.

- Characterization of SR-Latch PUF over 10 Zynq devices and 25 Spartan-6 devices.

- Characterization of RO-PUF over 31 Spartan-3 devices.

- Comprehensive analysis of PUF response generation schemes.

- Development of post processing schemes and their software implementations for analysis and evaluation of various PUF designs.

- Evaluation of the PUF for 'Key generation' application.

- Selection and integration of the most suitable error correcting schemes.

- Development of a final product that generates the PUF response and does all calculations on-chip in real time.

## 4. Methodology

Our methodology is based on the following steps,

### 4.1. Collection of Raw Results

The unprocessed data we collect from FPGA device is called a raw result. This result consists of frequencies of ring oscillators or counts of metastable latches. These components (latches and oscillators) constitute the PUF design. We implemented RO PUF on Spartan-3 devices. Similarly, SR-latch based PUFs have been implemented on Spartan-6 and Zynq [71] devices. We collected data from these devices at room temperature and at nominal voltage. For reliability purposes the data is also collected at varied temperature and voltage. The nominal voltage of Spartan-6 device is 1.2V and for Zynq devices, it is equal to 1V. We varied the voltage by ±5%. Similarly, the temperature was varied from -5°C to 85°C. We tested our devices at -5°C, 0°C, 20°C, 45°C, 65°C and 85°C. It was made sure that devices are heated or cooled down for at least one hour in the heating chamber before the data is collected from it. Furthermore, when results were analyzed, the corner cases were also tested to see the result of worse case operating conditions on the PUF quality. It must be noted that the Spartan-6 boards were tested, while they were new. This was done to prevent the negative effect of ageing on the PUF results.

In the next stage we plan to implement PUF designs on Artix-7 and collect raw PUF data.

This data collection will be done at rated operational condition of temperature and voltage allowed by the manufacturer of these devices.

## 4.2. Converting Raw Results into PUF IDs

In this process, software scripts are employed to convert the raw data collected from the devices into a binary PUF response. The frequency of two components (latches or oscillators) is compared with each other and a response bit is generated. Different schemes can be used to select these two components. We describe these schemes below. It must be mentioned that python script is used for PUF response generation in each scheme.

## 4.3. Mathematical description of PUF properties

We briefly explained the PUF properties in section 2.2. Here they are explained with mathematical equations and illustrations.

#### • Inter-chip Hamming Distance

It is equivalent to the hamming distance between the responses of any two FPGA devices at the room temperature and nominal voltage. It shows the difference between the responses of any two devices. It is defined as ,

Inter – chip Hamming distance =

$$\frac{\text{HD}(R_i,R_j)}{L} \times 100\%$$

(1)

Where L is the length of response bits. Ri and Rj are the responses of two FPGA devices.

The following figure explains it,

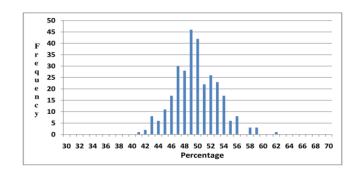

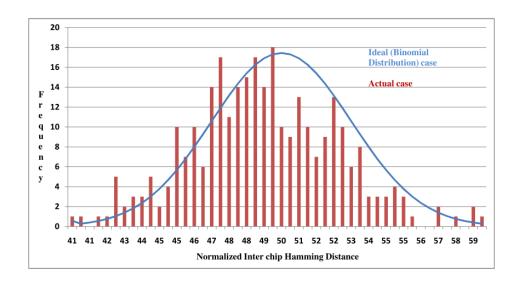

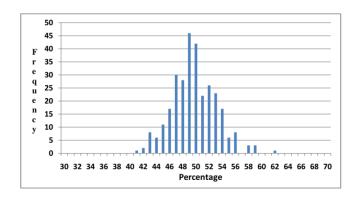

Figure 13: Normalized Inter-chip Hamming Distance

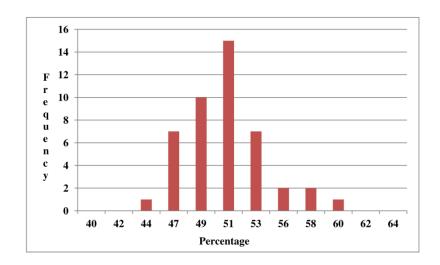

In the above figure, the x-axis shows the normalized Hamming Distance. While the y-axis (denoted frequency) shows the total number of times a given normalized inter-chip Hamming distance was obtained. In the above figure 25 devices have been used, the total number of combinations (i.e., the total number of board pairs  $\{i,j\}$ ) is  $\binom{25}{2}$ = 300. In ideal case, the normalized inter-chip HD should be 50% and will follow the binomial distribution. It means that 50% PUF output bits are different between PUF A and PUF B? If the PUF produces uniformly distributed independent random bits, the inter-chip variation should be 50% on average. Below in Fig. 14 it is shown how an actual PUF data compares with ideal case.

Figure 14: Normalized Inter chip HD (Average = 49%)

## • Intra-chip Hamming Distance

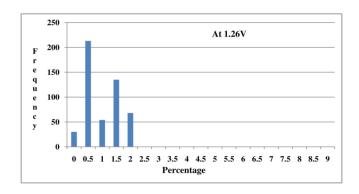

The Normalized intra-chip Hamming distance is defined as (HD  $(R_i, R'_{i,t})/L$ ) •100%. Where Ri is the response of a device at room temperature and  $R'_{i,t}$  is the response of the same device when either temperature or voltage is changed. Ideally the response should not change and the device output should be similar to what we get at a room temperature. However, in actual case, both the voltage and temperature affects the response.

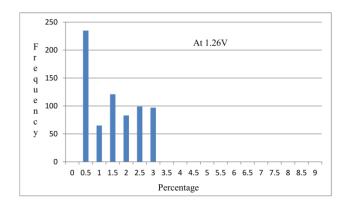

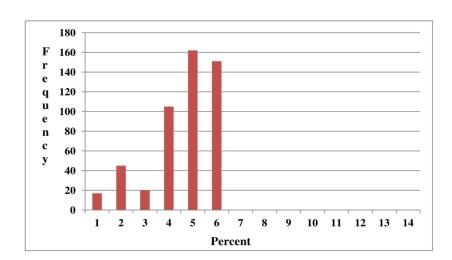

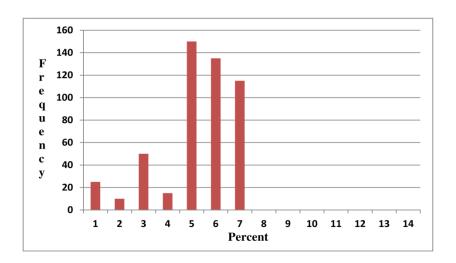

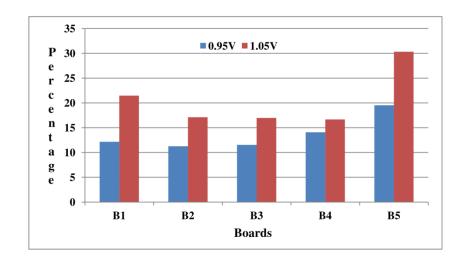

Figure 15: Normalized Intra-chip Hamming Distance

The histogram of normalized intra-chip Hamming Distance at 1.26V is shown above in Fig. 19. In this figure the x-axis shows the Hamming Distance in terms of percentage. While the y-axis (denoted frequency) shows the total number of times a given normalized intra-chip Hamming distance was obtained. In the above figure PUF response is generated 100 times for five boards at 25°C. Therefore, the total number of combinations is 500. In ideal case all 500 readings at 1.26V should have 0% HD. However, from the figure it is evident that a 2% change occurs in the HD at 1.26V. It must be mentioned that the nominal voltage for the devices used in this experiment was 1.2V.

In literature, intra-chip HD is sometimes referred to reliability.

### Uniqueness

Uniqueness represents the ability of a PUF to uniquely distinguish a particular chip among a set of devices of the same type. Hamming distance (HD) between a pair of PUF identifiers

is used to evaluate uniqueness. If two devices, i and j ( $i \neq j$ ), have n-bit responses, Ri and Rj, respectively, for the same challenge, the average inter-chip HD among N devices is defined as,

Uniqueness =

$$\frac{2}{N(N-1)} \sum_{i=1}^{N-1} \sum_{j=i+1}^{N} \frac{HD(R_i, R_j)}{L} \times 100\%$$

(2)

It is an estimate of the inter-chip variation in terms of the PUF responses and not the actual probability of the inter-chip process variation.

## Worse case Uniqueness

It is equal to the minimum HD between any two chips.

$$Worse \ case \ Uniqueness = Min_{i=1,j=i+1}^{i=N-1,j=N} \left( \frac{\text{Min}(\text{HD}(\text{Ri},\text{Rj}),\text{L}-\text{HD}(\text{Ri},\text{Rj}))}{\text{L}} * 100\% \right) \eqno(3)$$

In ideal case, it should be 50%.

### Uniformity

Uniformity of a PUF estimates how uniform the proportion of '0's and '1's are in the PUF response.

Uniformity (i) =

$$\frac{1}{L} \sum_{l=1}^{L} r_{i,l} \times 100\%$$

(4)

Where  $r_{i,l}$  is the lth binary bit in the response of a chip i.

### Reliability

Reliability measures how accurately the PUF responses are reproduced under different operating conditions. These conditions include temperature, voltage or radiation. Intra-chip HD among several samples of PUF response bits are used to evaluate it. To estimate the

intra-chip HD, L-bit reference response (Ri) from the chip i at normal operating condition (at room temperature using the normal supply voltage) is extracted. The same L-bit response is extracted at a different operating condition

(different ambient temperature or different supply voltage) with a value  $R_i$ . T samples of Ri are collected. For the chip i, the average intra-chip HD is estimated as follows:

HD Intra (i)=

$$\frac{1}{T}\sum_{t=1}^{T} \frac{\text{HD}(R_{i},R_{i,t})}{L} \times 100\%$$

(5)

where  $R_{i,t}$  is the tth sample of a device i.  $HD_{INTRA}$  indicates the average number of noisy PUF response bits. In other words, the reliability of a PUF can be defined as

Reliability =

$$100\%$$

– HD Intra (i) (6)

Fig. 8 shows how the reliability of a PUF is evaluated using the time dimension of PUF measurement.

## • Worse Case Reliability

It is based on the maximum number of noisy bits under any set of conditions. Normally the corner cases of temperature and voltage are evaluated to see the number of noisy bits at the extreme level. We believe that for error correction purposes we need to consider the worse case reliability. Worse case reliability for chip i can be calculate as,

Worse case Reliability(i) =

$$Min_{i=1}^{N} \left( 1 - \frac{\frac{C}{Max \, HD(R_i, \, R_{i,c})}}{L} \right) \times 100\%$$

(7)

Where C shows all possible conditions.

## Bit-aliasing

If bit-aliasing happens, different devices may produce nearly identical PUF responses, which is an undesirable effect. It gives us the information about the presence of systematic and spatial effect across devices. We estimate bit-aliasing of the lth bit in the PUF identifier as the percentage Hamming weight (HW) of the lth bit of the identifier across N devices:

Bit aliasing (l) =

$$\frac{1}{N} \sum_{i=1}^{N} r_{i,l} \times 100\%$$

(8)

Where  $r_{i,l}$  is the response of chip i at lth location.

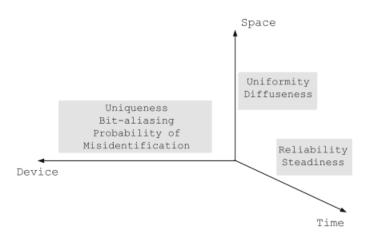

Figure 16: Parameters mapped on the PUF measurement dimension [58]

The properties of PUF are distributed along the device, space and time dimensions as shown above in the figure.

Notations used in the properties are:

Table 2: Notations used in equations

| N = Number of FPGA devices                                   |  |  |

|--------------------------------------------------------------|--|--|

| $n = index \ of \ an \ ID \ in \ a \ chip \ (1 \le n \le N)$ |  |  |

| M = Number of ROs or Latches                                 |  |  |

| L = Size of ID in bits                                       |  |  |

| $l = index of a response bit ( 1 \le l \le L )$              |  |  |

| Ri = Response of chip i, at normal operating                 |  |  |

| Rj = Response of chip j, at normal operating                 |  |  |

| HD= Hamming distance                                         |  |  |

| T = total number of samples measured per ID                  |  |  |

| $t = index of a sample (1 \le t \le T)$                      |  |  |

| $R_{i,C}$ = Response of chip i, at condition C.              |  |  |

## 4.4. Entropy

Actual entropy of a PUF is a function of complex physical processes. Therefore, it is close to impossible to calculate the actual entropy of a PUF response. Normally, only the estimated upper bounds on the underlying entropy can be calculated. These bounds can be calculated using at least the following two methods.

1) Based on the analysis of single bits

### 2) Based on the analysis of pairs of bits

Both these methods have been explained in [48]. The first method assumes that an adversary knows a bias for each position of a PUF response. In this method every bit position in a PUF response vector will have its own bias. An adversary knowing these individual bit-dependent biases can make a more accurate prediction by guessing individual bits in favor of these biases. This upper bound, called the bit-dependent bias entropy bound, can be calculated by using

$$H(Y^n) = \sum_{i=1}^n h(p_i) \tag{9}$$

In the above equation, h(pi) is the binary entropy function, it is calculated for n bit positions. The second method is based on the analysis of a pair of PUF response bits. This method assumes that an adversary knows pairwise joint distributions for pairs of consecutive bits i and i+1. This bound is tighter than the bound given by (9). It is called pairwise joint distribution entropy bound. It can be calculated using equations (10) and (11).

$$H(Y^{n}) = \sum_{i=1}^{n} h(p_{i}) - \sum_{i=1}^{n-1} I(Y_{i}, Y_{i+1})$$

(10)

Where,

$$I((Y_1, Y_2) = \sum_{y_1 \in y_1} \sum_{y_2 \in y_2} p(y_1, y_2) \cdot \log_2 \frac{p(y_1, y_2)}{p(y_1)p(y_2)}$$

(11)

In equation (10), h(pi) is the binary entropy function, while I(Yi,Yi+1) is the mutual information between two random variables Yi and Yi+1. The mutual information between two random variables is a measure for the amount of information which is shared by both variables. We estimate the pairwise joint distributions of all possible pairs of the considered response bits, by counting the occurrences of each of the four possible pairs ('00', '01', '10', and '11') in the n bit response of all devices.

## 5. Efficient SR-PUF design

In this chapter we present a reliable and efficient SR-Latch based PUF design, with two times improvement in area over the state of the art, thus making it very attractive for low-area designs. This PUF is able to reliably generate a 128-bit cryptographic key. The PUF response is generated by quantifying the number of oscillations during the metastability state for preselected latches. The derived design has been verified on 25 Xilinx Spartan-6 FPGAs (XC6SLX16) and 10 Xilinx Zynq SoC (XC7Z010) devices. The design exhibited ~49% uniqueness figures when tested on both types of FPGAs. The reliability figures were > 94% for temperature variation (0-85°C) and  $\pm$  5% of core voltage variation. We also propose two error correcting schemes that assure that a key generated in the field is similar to the one generated under nominal conditions. This chapter is based on the work presented at [70, 75].

#### Contents

| <u>5. Eff</u> | ficient SR-PUF design      | 46 |

|---------------|----------------------------|----|

| <u>5.1.</u>   | <u>Introduction</u>        | 47 |

| <u>5.2.</u>   | Motivation                 | 49 |

| <u>5.3.</u>   | Related Work               | 49 |

| <u>5.4.</u>   | Design Methodology         | 51 |

| <u>5.5.</u>   | Bit Generation             | 61 |

| <u>5.6.</u>   | Results                    | 63 |

| <u>5.7.</u>   | Implementation on Zynq SoC | 79 |

#### 5.1. Introduction

In the last couple of decades there has been an exponential increase in the digital information processing and communication systems. With this phenomenal increase, security challenges are becoming significant. Recent research has led to an increased interest in security measures, especially in solutions that are physically unique and unclonable. In this regard, different structures of Physical Unclonable Functions (PUFs) have been developed and investigated to efficiently meet the requirements of these solutions. PUFs are physical primitives which produce unclonable and device-specific measurements of silicon Integrated Circuits (ICs). These measurements are then processed to generate either responses in challenge-response schemes or secure keys for cryptographic functions. Manufacturing process variations give physical uniqueness, but many physical unclonable functions (PUFs) are noisy and exhibit low circuit efficiency. Therefore, while designing new PUF structures, we need to focus on the efficiency besides the unclonability, uniqueness, and reliability, because expensive designs cannot fulfill the requirements of low-area applications.

PUF structure is incorporated in the silicon devices for targeting two major applications. First one is the identification of silicon devices and another one is secure key generation for cryptographic functions. In the case of identification, the silicon devices go through the

process of enrollment. In this step, challenge response pairs (CRP) are generated and then stored in the database. This step is carried out at room temperature and nominal voltage. Once these devices reach the users in the field, the device PUF response is again generated. It is like a fingerprint used for human identification. If this PUF response is equivalent to the response stored in the database, the devices are identical, otherwise they are different. Since we do not know the operational conditions in the field, therefore a PUF is said to be reliable if it can generate the same response even if the operating conditions, namely voltage and temperature, are changed. Similarly, the response of PUF should be unique, so that the responses of any two devices are substantially different. Another major application of PUF is the generation of keys for cryptographic functions. The minimal requirements for a secure key generation and storage are: A) a source of randomness to ensure that generated keys are unique and unpredictable, and B) Keys are secure and shielded from unauthorized access. A PUF-based key generator tries to take care of both requirements at the same time by using a PUF to harvest static but device-unique randomness, and by processing it into a cryptographic key. It also avoids the need for a protected non-volatile memory to store the key. Since we know that key must be reproducible, therefore error correction schemes are employed to regenerate the key reliably in the field. In this paper we are targeting the secure key generation application using SR-latch PUF.

Part of this paper has been published in [70], we extended that work by implementing the design on Zynq devices. We tested Zynq devices at  $\pm$  5% of core voltage and (0-85°C) temperature. In Section 5.2, we explain the motivation for our PUF design. In Section 5.3 we describe the related work for a better understanding of our study on PUF. Section 5.4

explains the design methodology. In Section 5.5, we explain the bit-string generation. Results and analysis are covered in Section 5.6. Implementation on Zynq based SoC devices is described in Section 5.7. Conclusions are given in Section 5.8.

#### 5.2. Motivation

State of the art SR-latch PUF designs are very expensive in terms of chip area. These designs are not suitable for area constrained applications. We need to develop PUF designs that have small area footprint. Additionally these designs have to be reliable at different environmental conditions, i.e., the response of PUF at different voltage and temperature should match closely the response generated at the nominal voltage and room temperature. Furthermore, the PUF responses should be unique so that one PUF-ID can be easily differentiated from another ID. Apart from the reliability and uniqueness measure, the design should not be affected by the neighboring logic. These motivations lead us to propose a PUF design that is very efficient from the area consumption point of view and highly reliable at different voltages and temperatures. The effect of nearby logic inside the same CLB is negligible. The uniqueness measure is close to the ideal case.

### 5.3. Related Work

Since 2002, silicon based PUFs have been extensively investigated. There are two categories of silicon based PUF circuits: Delay based PUFs and Memory based PUFs. In delay based PUF, the propagation delay of a signal is used to generate a PUF response. Delay based PUFs include Arbiter PUF, Ring-Oscillator (RO) PUF and S-ArbRO PUF. In [30] and [39], the concept of programmable delay lines is presented, in which the LUT delays are used to create a metastable condition, which is further used to develop a PUF

and TRNG, respectively. Similarly, in [56], a PUF is developed using the programmable delay lines of LUT.