# $\underline{ \text{A MODEL-BASED TESTING TECHNIQUE FOR} } \\ \text{COMPONENT-BASED REAL-TIME EMBEDDED SYSTEMS}$

by

Jing Guan

A Dissertation

Submitted to the

Graduate Faculty

of

George Mason University

In Partial Fulfillment of

The Requirements for the Degree

of

Doctor of Philosophy

Information Technology

| Committee: |                                                           |

|------------|-----------------------------------------------------------|

|            | Dr. Jeff Offutt, Dissertation Director                    |

|            | Dr. Daniel A. Menasce, Committee Member                   |

|            | Dr. Sam Malek, Committee Member                           |

|            | Dr. Kris Gaj, Committee Member                            |

|            | Dr. Stephen Nash, Senior Associate Dean                   |

|            | Dr. Kenneth S. Ball, Dean, Volgenau School of Engineering |

| Date:      | Summer Semester 2015 George Mason University Fairfax, VA  |

# A Model-Based Testing Technique for Component-Based Real-Time Embedded Systems

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

By

Jing Guan Master of Science University of Maryland at College Park, 1999 Bachelor of Science Northwestern Polytechnical University, 1997

> Director: Dr. Jeff Offutt, Professor Department of Computer Science

> > Summer Semester 2015 George Mason University Fairfax, VA

Copyright © 2015 by Jing Guan All Rights Reserved

### Dedication

I dedicate this dissertation to my dearest children William Wang and Patrick Wang for your understanding. You both have grown up along with my PhD study. Your sweetness makes everyday filled with sunshine. I dedicate this dissertation to my loving parents Fengqin Wang and Decai Guan for your encouragement, trust and support. Your unconditional love gives me strength to work hard and always try my best endeavor on everything. I dedicate this dissertation to my husband Tao Wang for your patience. Your optimistic character helped me through many difficult times in this journey. You motivated me to start, continue and finish my PhD study.

#### Acknowledgments

My biggeset thanks goes to my dear advisor, Dr. Jeff Offutt. This dessertation could not have been started and completed without him. At my very first class in George Mason, he told me "You are in the right place!". That sentence changed my whole life. He not only taught me how to do a research and write research papers but also helped me find the best of myself. He always believes in me and gives me confidence when I feel I am not good enough to move forward. I would like to thank him for his patience and his encouragement to guide me through every gloomy moment. You are the person who truly understands how hard it's been for me and offers your support at any times.

I would like to thank all my other committee members for offering their time and for delivering valuable knowledge and insight. I would like express my greatest respect to Dr. Daniel Menasce for not only providing me valuable suggestions on my research and dissertation, but also guiding me through the darkest time. I will never be able to describe how much your encouragement meant to me. Your profound knowledge and noble character will influnce and benefit me forever! I sincerely thank Dr. Sam Malek for challenging me so I can come to a whole new level of the research. Your suggestions not only opened my eyes on the academic area but also made me a stonger person. As a result, this journey becomes more unforgettable and worthy. I truely appreciated Dr. Kris Gaj for stepping up to serve as my committee member at the time when I needed it the most.

I would also like to thank my company Lockheed Martin for providing me all the valuable resources and financial support. I have the best colleague I could ask for. They've shown their support for my PhD study in all kinds of ways.

# Table of Contents

|     |        | Page                                                                                                                        | ;      |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------|--------|

| Lis | t of T | bles vii                                                                                                                    | Ŀ      |

| Lis | t of F | gures                                                                                                                       |        |

| Ab  | stract |                                                                                                                             |        |

| 1   | Intr   | duction $\dots \dots \dots$ |        |

|     | 1.1    | General Introduction                                                                                                        |        |

|     | 1.2    | Goals and Scope of This Research                                                                                            | :      |

|     |        | 1.2.1 Problem Statement                                                                                                     | 1      |

|     |        | 1.2.2 Thesis Statement                                                                                                      |        |

|     |        | 1.2.3 Scope of Research                                                                                                     | ı      |

|     | 1.3    | Solution Strategy                                                                                                           |        |

|     | 1.4    | Unique Contributions of the Research                                                                                        |        |

|     | 1.5    | Dissertation Organization                                                                                                   |        |

| 2   | Bac    | ground                                                                                                                      | ı      |

|     | 2.1    | Real-Time Embedded System                                                                                                   |        |

|     | 2.2    | Testing Embedded Software                                                                                                   |        |

|     | 2.3    | Component-based Real-time Embedded Software                                                                                 | !      |

|     | 2.4    | Component-based Real-time Embedded Software Architecture                                                                    | :      |

|     | 2.5    | Component-based Real-time Embedded Software Design Models 18                                                                | i      |

| 3   | Issu   | s and Related Work                                                                                                          | J      |

|     | 3.1    | Related Work                                                                                                                |        |

| 4   | A C    | mponent-based Real-time Embedded Software Architecture and Design Based                                                     |        |

|     | Testi  | g Technique                                                                                                                 | ı      |

|     | 4.1    | The CREATEG Model                                                                                                           | 1      |

|     |        | 4.1.1 Component Interface Interaction Graph (CIIG)                                                                          | :      |

|     |        | 4.1.2 Component State-based Interaction Behavior Graph (CSIBG) 40                                                           | ı      |

|     |        | 4.1.3 Component State-based Event-driven Interaction Behavior Graph (CSIEDB                                                 | (G) 52 |

|     | 4.2    | Constructing the CREATEG                                                                                                    | ;      |

|     | 4.3    | Generating Test Paths from the CREATEG                                                                                      | ,      |

|     | 4.4     | Coverage Criteria for Test Paths          |

|-----|---------|-------------------------------------------|

|     |         | 4.4.1 All-Interface coverage              |

|     |         | 4.4.2 All-Interface-Transition Coverage   |

|     |         | 4.4.3 All-Interface-Event Coverage        |

|     | 4.5     | Executing the Test Cases                  |

| 5   | Exp     | perimental Tool                           |

|     | 5.1     | The CREATEG Constructor                   |

|     | 5.2     | Test Path Generator                       |

|     | 5.3     | Test Executor                             |

|     | 5.4     | Results Evaluator                         |

| 6   | Vali    | dation on a Large Scale Industrial System |

|     | 6.1     | Experimental Design                       |

|     |         | 6.1.1 Experimental Procedure              |

|     |         | 6.1.2 The Subject Program                 |

|     |         | 6.1.3 Test Adequacy Criteria              |

|     |         | 6.1.4 Test Data                           |

|     |         | 6.1.5 Fault Sets                          |

|     | 6.2     | Experimental Results                      |

|     | 6.3     | Threats to Validity                       |

|     | 6.4     | Conclusion                                |

| 7   | Con     | clusion and Future Work                   |

|     | 7.1     | Conclusion                                |

|     | 7.2     | Future Work                               |

| Bib | oliogra | aphy                                      |

# List of Tables

| Table |                                                                 | Page |

|-------|-----------------------------------------------------------------|------|

| 4.1   | Partial truth table for a CACC example                          | 85   |

| 6.1   | Number and types of faults seeded                               | 110  |

| 6.2   | Number of faults detected for each test method in each test set | 120  |

| 6.3   | Number of faults detected for each test method in each test set | 122  |

| 6.4   | Number of test case for each test method in each test set       | 123  |

| 6.5   | Quantitative Analysis of Mutants Score for each test method     | 123  |

| 6.6   | Statistic Analysis of Mutant Scores Comparison                  | 125  |

| 6.7   | Code coverage ratio                                             | 126  |

# List of Figures

| Figure |                                                                         | Page |

|--------|-------------------------------------------------------------------------|------|

| 2.1    | Structure of an embedded system                                         | 10   |

| 2.2    | SCA software architecture detailed view                                 | 15   |

| 2.3    | Relationship between SCA components                                     | 16   |

| 2.4    | Connection of components via ports                                      | 17   |

| 4.1    | A simple state diagram                                                  | 28   |

| 4.2    | Flowchart for the proposed testing technique                            | 30   |

| 4.3    | A component level sequence diagram                                      | 32   |

| 4.4    | Component interaction scenario 1                                        | 33   |

| 4.5    | Component interaction scenario 2                                        | 33   |

| 4.6    | Component interaction scenario 3                                        | 34   |

| 4.7    | A software system that consists of multiple components<br>e             | 38   |

| 4.8    | State dependent message paths                                           | 41   |

| 4.9    | State dependent transition paths                                        | 43   |

| 4.10   | A CSIBG example                                                         | 47   |

| 4.11   | A CSIEDBG example                                                       | 53   |

| 4.12   | Sequence diagram for receiving data from ethernet device                | 55   |

| 4.13   | An algorithm to generate the CIIG                                       | 58   |

| 4.14   | The CIIG of the system                                                  | 59   |

| 4.15   | State diagram for ethernet device                                       | 61   |

| 4.16   | State diagram for SCA ethernet adapter                                  | 62   |

| 4.17   | State diagram for IP interface adapter                                  | 63   |

| 4.18   | State diagram for IP core                                               | 64   |

| 4.19   | The CSIBG of the system                                                 | 65   |

| 4.20   | An algorithm to generate the CSIBG                                      | 67   |

| 4.21   | A complete CSIBG                                                        | 69   |

| 4.22   | An algorithm to generate the CSEDIBG                                    | 72   |

| 4.23   | An algorithm to generate test paths for the All-path coverage criterion | 74   |

| 4.24 | Sequences of test path for all the component subnets                          | 76  |

|------|-------------------------------------------------------------------------------|-----|

| 4.25 | Message expression for a message sequence                                     | 77  |

| 4.26 | An algorithm to generate test paths for the All-Interface Coverage criterion  | 79  |

| 4.27 | An algorithm to generate test paths for the All-Interface-Transition coverage |     |

|      | criterion                                                                     | 82  |

| 4.28 | State diagram for component C                                                 | 84  |

| 4.29 | An algorithm to generate test paths for the All-Interface-Event coverage cri- |     |

|      | terion                                                                        | 87  |

| 5.1  | Structure of AM2TM experimental tool                                          | 90  |

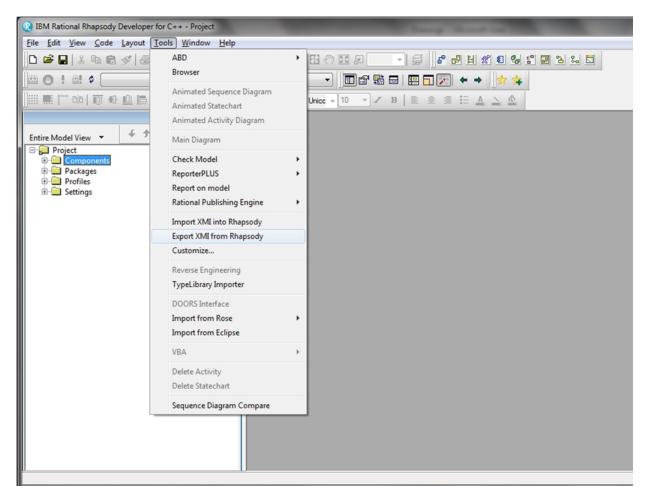

| 5.2  | XMI generation in Rational Rhapsody                                           | 91  |

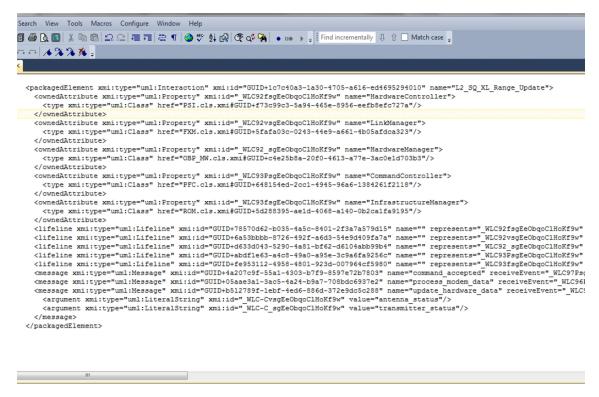

| 5.3  | XMI file generated from a Rational Rhapsody UML sequence diagram $\ .$        | 92  |

| 5.4  | A Java XML parser via DOM interface                                           | 93  |

| 5.5  | Spawning a test task                                                          | 95  |

| 5.6  | Test code example                                                             | 97  |

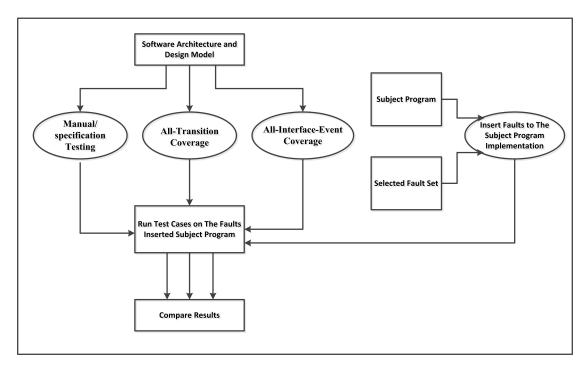

| 6.1  | Experiment procedure                                                          | 102 |

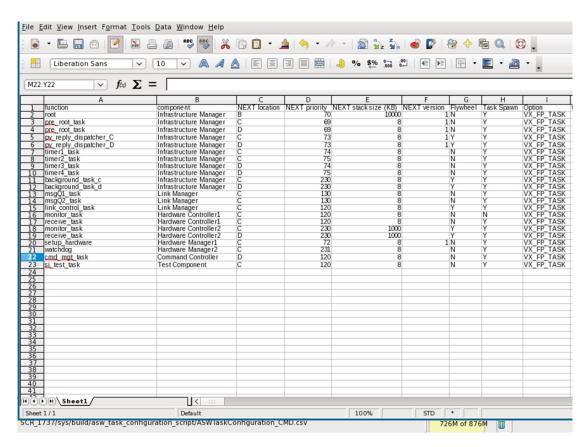

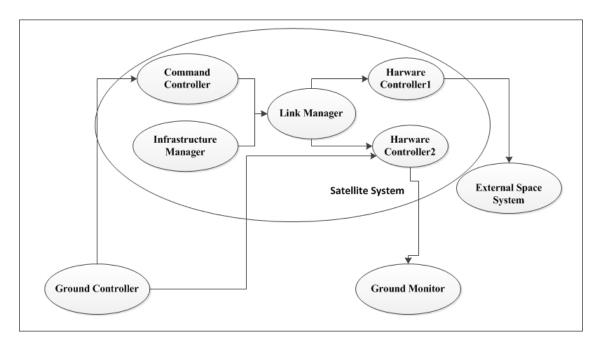

| 6.2  | The subject program                                                           | 103 |

| 6.3  | Test case example                                                             | 105 |

| 6.4  | Test log example                                                              | 106 |

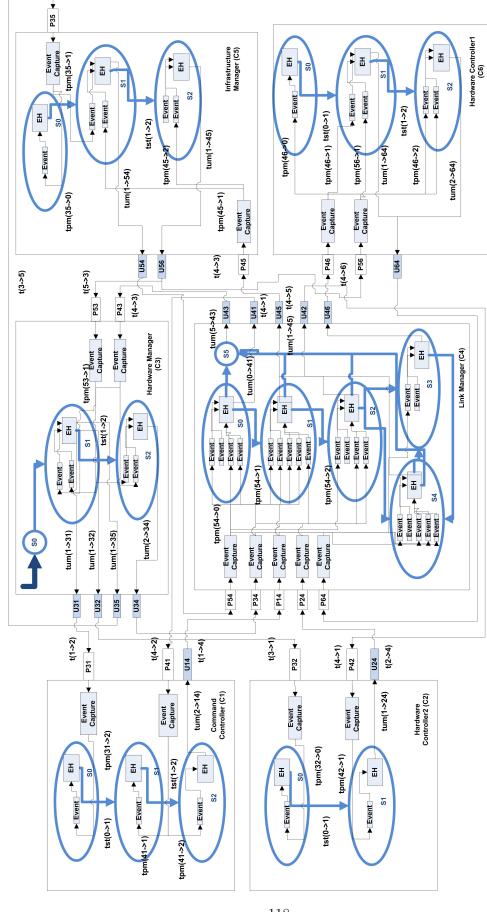

| 6.5  | The CSIEDBG of the subject program                                            | 118 |

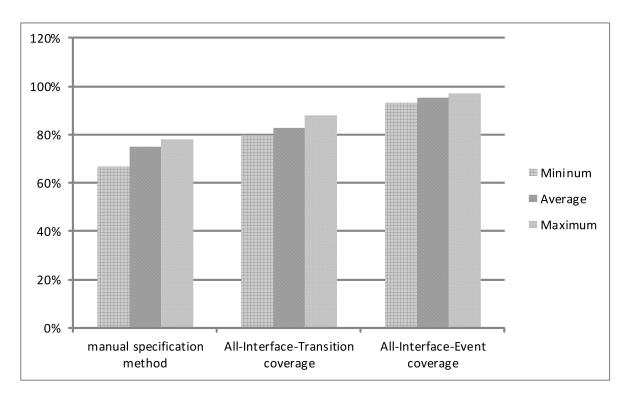

| 6 6  | The graph of mutant score                                                     | 124 |

Abstract

A MODEL-BASED TESTING TECHNIQUE FOR COMPONENT-BASED REAL-TIME EMBEDDED SYSTEMS

Jing Guan, Ph.D.

George Mason University, 2015

real-time embedded software.

Dissertation Director: Dr. Jeff Offutt

The growing complexity of modern real-time embedded systems makes component-based software engineering (CBSE) technology more desirable. Although many ideas have been proposed for building component-based real-time embedded software, techniques for testing component-based real-time systems have not been well developed. A typical componentbased embedded system consists of multiple user tasks, as well as hardware, middleware and software layers. Interaction problems between different components can cause system failures in field applications. The challenges not only come from the integration of multiple components through their interfaces, but also include the composition of extra-functional properties. In an embedded system, extra-functional requirements are as important as functional requirements. A real-time embedded system needs to achieve its functionality under the constraints caused by its extra-functional properties. Since the time at which the system actions take place is important, correct functional behavior with regard to timing properties is essential to real-time embedded systems. Therefore, this research is intended to help detect both functional and temporal faults during the integration of component-based

This dissertation presents a test model that depicts both inter-component and intracomponent relationships in component-based real-time embedded software and indentifies key test elements. The test model is realized using a family of graph-based test models in which not only are the functional interactions and the dependence relationships illustrated, but also the time-dependent interaction among components, are illustrated. Time dependednt behavior is modelled by means of timers and clocks. A notion of timed events define constraints in timed scenarios. I use the graph-based test model to develop a novel family of test adequacy criteria that help generate effective test cases. In this test model, I use timing-constraint to specify the duration and execution cost of inter-component and intra-component interactions as well as state transitions and activities. I also present new algorithms to facilitate automate generation of the test cases. To increase the observability of system behavior, I instrument related operations to generate trace data including task id, operation, time stamp, and execution state from program execution, where the dynamic information gathered is used to check against the expected results. The experiments showed that the proposed approach effectively detected various kinds of integration faults and optimized the balance between budget and quality in an industrial product software testing.

#### **Chapter 1: Introduction**

#### 1.1 General Introduction

The increased complexity of real-time embedded systems leads to increasing demands with respect to software engineering. This complexity makes the development of such systems very expensive. To reduce development costs, component-based modeling is increasingly being used to develop for embedded systems. It is expected to bring several advantages to embedded systems, such as rapid development time, the ability to re-use existing components, and the ability to compose sophisticated software [28].

Component-based technology has been extensively used for many years to develop software systems in desktop environments, office applications, and web-based distributed application [8]. The advantages are achieved by facilitating the reuse of components and their architecture, raising the level of abstraction for software construction, and sharing standardized services. Real-time embedded systems have requirements not found in most desktop systems such as timeliness requirements and resource efficiency. So, it is more difficult to adapt component-based software engineering (CBSE) to real-time embedded system than desktop systems [35].

The components may have been written in different programming languages, execute in various operational platforms, and be distributed across vast geographic distances. Some components may be developed in-house, while others may be third party or commercial off-the-shelf components (COTS) [86]. A benefit of this kind of design is that software components can be analyzed and tested independently. At the same time, this independence of components means that significant issues cannot be addressed until full system integration testing. As a result, complex behaviors are observed when components are integrated and several kinds of faults may arise during integration. Thus, testing each component

independently does not eliminate the need for system integration testing. Many possible interactions between components need to be tested to ensure the correct functionality of the system [36].

As the size and complexity of software systems increase, problems stemming from the design and specification of overall real-time embedded system structure become more significant. The result is that the way groups of components are arranged, connected, and structured is crucial to the success of software projects. Problems in the interactions can affect the overall system development and the cost and consequences could be severe [45].

Testability for real-time embedded software is a challenging problem due to the low observability and controllability of embedded systems [80]. Embedded software often gets its inputs from hardware and generates outputs for hardware rather than for users, so it is more difficult to control and observe. CBSE increases the complexity, which affects the observability and controllability.

Real-time embedded platforms are also complex integrated systems where multiple real-time tasks execute in multi-tasking environments. In a component-based embedded system, each individual component may run several tasks, so the number of messages between tasks across components is dramatically increased [57]. When integrating these components together, unexpected results may occur if interactions between components are not fully tested. Interactions between components may give rise to subtle errors that could be hard to detect.

Additionally, any component in a system can be updated at any time, so the dependencies between the existing and the modified components can change dynamically. Therefore, adequate and extendable testing methods for continuous validation of integrated component systems is essential to the success of a component-based real-time embedded system. Despite its value, component-based modeling introduces new problems when testing real-time embedded software systems [50]. This dissertation describes research to develop a new systematic software testing technique to thoroughly examine the component interaction behavior during system integration testing activities. The technique is based on models

created from the software architectures and design specification, which specify the primary components, interfaces, dependences, and behaviors of software systems.

The faults that occur during component integration are different from those found during unit and component testing [14]. Faults that cannot be detected during unit, module, and component testing are often faults in the way the software components are structured or in how they communicate. Correctly implementing interactions can be difficult because, unlike the components of a software system, the interactions are rarely isolated in a single, independent runtime structure. Instead, interaction is typically spread across the components involved in the interaction. To make matters more difficult, this interaction code is often tightly integrated with the code associated with the component's functionality.

A fundamental problem of test data generation is that the only way to ensure complete correctness is to test with all possible inputs [64]. However, the number of possible inputs to a given program is effectively infinite, so testers must accept partial results by finding a finite number of test cases that will provide a high level of confidence that the program's behavior is satisfactory. Software architecture can provide a framework for understanding system components and their interrelationships, especially those attributes that are consistent across time and implementations. At the software architecture level, software systems are presented at a high level of abstraction where a software system is viewed as a set of compositional components, interactions among these components, and the configuration of the system. Implementation details are suppressed and the independence of system components is increased. The software architecture specifications provide a description of the software system that could be used to generate tests at the integration level. This lets developers abstract away unnecessary details and focus on the assignment of software components, interfaces to hardware components, and how they model their important aspects throughout and especially early in development.

A software architecture design specification captures the system level details of components, interactions and context. For example, the Unified Modeling Language (UML) provides a variety of diagramming notations for capturing architecture and design information from different perspectives [6] [38]. In a component level sequence diagram, the interaction between components is defined explicitly. In recent years, researchers have invented ways to use UML models as a source of information in software testing [54] [86] [66] [12]. Many UML design artifacts have been used in different ways to perform different kinds of testing. For instance, UML statecharts have been used to perform unit testing [78] [67] [20], and interaction diagrams (collaboration and sequence diagrams) have been used to test class interactions [76] [59] [10] [34].

A software architecture design specification precisely describes how the software is expected to behave in a high level way that can easily be used by automated methods.

Evaluating and testing software systems based on software architecture and design specifications can allow tests to be created earlier in the development process, therefore substantially reducing the costs of any problems and errors. Currently, there is a lack of testing techniques for testing component-based real-time embedded system at the software architecture level. In this dissertation, I present research in the area of software architecture and design based testing to create a general testing technique at this level.

# 1.2 Goals and Scope of This Research

Testing integration of components becomes an important activity in CBSE [69]. Testing methods for component-based embedded real-time software is a relatively new research field [60]. The informality of the usual testing methods makes it difficult to measure the quality of testing, leads to a lack of repeatability in the process and results, and means that the tester cannot be confident in the efficiency of the testing. As a result, errors may severely impact the software in ways that are costly to fix and causes delays and failures when deploying systems in the real world. To improve both functional and real-time testing of component-based real-time embedded software, tester need a time-dependent interaction model between the embedded real-time components.

The objective of this research is to provide a new model-based testing approach to help component-based real-time embedded software testing become more structured. In turn, this will lead to software systems that have fewer faults.

#### 1.2.1 Problem Statement

Component-based real-time embedded system development brings new challenges to traditional embedded engineering. In particular, the current method of testing this type of software is inadequate. We need stronger techniques to test this type of component-based real-time embedded systems.

Manual and specification testing techniques do not work effectively for component-based real-time embedded systems since they cannot detect many of the faults that are novel to this type of software system.

To solve the problem, we need to consider the unique characteristics of this type of software. This research project has addressed the problem of finding a better way to test component-based real-time embedded software.

#### 1.2.2 Thesis Statement

This thesis addresses the problem of testing component-based real-time embedded software by inventing formal test criteria for software architecture level integration testing in component-based real-time embedded systems. The research includes techniques to design effective test cases based on a novel family of test adequacy criteria and analyze results to detect both functional and temporal faults during the integration of component-based real-time embedded software.

#### 1.2.3 Scope of Research

This research focuses on studying efficient and practical solutions for modeling and deriving integration tests for component-based real-time embedded software. Due to the tight relationships between its functionality and the constraints caused by its extra-functional properties, component integration testing in an embedded system cannot be solely achieved by examining components' behavior through their interfaces. Among extra-functional properties, this dissertation only focuses on the timing requirements and software/hardware dependencies. In this research, periodic tasks are limited to periodic events triggered by periodic timers controlled by components; Aperiodic tasks are activated by external events. Other embedded constrained resources, such as resource allocation, amount of memory, processor speed and power consumption, are not in the scope of this research. Task scheduling, tsk priorities that change over time and clock-based deadlines are also out of scope of this research.

This dissertation makes the following contributions:

- 1. A technique that enhances the integration testing of components by accounting for states of collaborating components in an interaction. This is important as interactions may trigger correct behavior for certain states and not for others. To achieve such an objective the proposed technique includes a novel intermediate test model called the Component-based Real-time Embedded Architecture-based Test Graph (CREATEG) model from component level sequence diagrams and state diagrams of the components involved in the component interactions.

- 2. Timing notations to specify the duration and execution cost of inter-component and intra-component interactions as well as state transitions and activities. Timing characteristics of the execution infrastructure are taken into account in the test model. A functional behavior determinism with regard to time is realized.

- 3. Test criteria for generating integration tests from the CREATEG models. The CREATEG models all possible paths for component state transitions that a message sequence may trigger. These criteria can be used both to guide the architecture designers and to help the testers generate meaningful and effective test cases.

- 4. Timed input values and timed output results to utilize timed message sequence. Trace information is unified in the program instrumentation to include task id, operation,

time stamp, and execution state. Non-deterministic outputs, caused by real-time and concurrency features in embedded systems, are better observed and analyzed.

- 5. Algorithms to automatically create test requirements. These algorithms are based on CREATEG models.

- 6. An experimental tool to generate test cases automatically from CREATEG models. The test generator uses CREATEG to generate test paths whose test cases attempt to detect faults that may arise due to invalid component states during interactions.

- 7. Empirical validation of the ideas. This dissertation reports on an empirical study to assess the effectiveness and cost of the test adequacy criteria based on the CREATEG test model. The architecture-based testing technique was applied to an industrial software system. The results are compared with results from using two other testing methods. The goal of this process is to determine whether the new testing technique can effectively detect faults.

## 1.3 Solution Strategy

To find solutions to our research problems, I first discuss issues of testing component-based real-time embedded systems, then list a set of properties to test based on software architecture design artifacts and models. This helps us decide what to test when testing at the integration level. Then we define architecture relations at the architectural level, and formally define these relations. Three graphical representations are introduced for testers to visualize the testing technique and for possible analysis and simulations. Test criteria based on the architecture relations are then presented. These criteria are formally defined. We then apply the technique to an industrial system, and develop algorithms to transform the architecture and design models to graphical representations. An empirical evaluation of the technique is carried out using an industrial software system, and its results are discussed.

#### 1.4 Unique Contributions of the Research

Major contributions of this dissertation are:

- 1. New test criteria for testing component-based real-time embedded software systems

- 2. A novel formal model of architecture relations in component-based real-time embedded software systems

- 3. A new architecture modeling technique based on UML

- 4. A timed model with timing notations and constraints

- 5. Formal definitions of transformation rules for translating UML models to architecture models

- 6. A unified form of timed instrumentation for increasing observability of component interactions

- 7. A prototype tool for generating test cases based on architecture models

## 1.5 Dissertation Organization

Chapter 2 describes background. Chapter 3 reviews issues and related research. Chapter 4 discusses the architecture based testing technique for general component-based real-time embedded software. Chapter 5 presents a proof-of-concept-tool. Chapter 6 discusses an empirical validation of the technique. Finally, Chapter 7 concludes the dissertation research and discusses future research directions.

#### Chapter 2: Background

This chapter provides background information and concepts required to understand the work in this dissertation. Section 2.1 describes background on embedded systems, including its architecture and properties. Section 2.2 discusses embedded software testing. Section 2.3 describes component-based real-time embedded software. Section 2.4 and Section 2.5 discuss component-based embedded software architecture and design.

#### 2.1 Real-Time Embedded System

An embedded system is a special-purpose computer system built into a larger device [71]. Usually there is no disk drive, keyboard or screen. Brockman and Notenboom [22] define embedded systems as a generic term for a broad range of systems covering, for example, cellular phones, railway signal systems, hearing aids, and missile tracking systems. They specify that all embedded systems have a common feature in that they interact with the real physical world, controlling hardware. The term embedded system can encompass a variety of devices and systems.

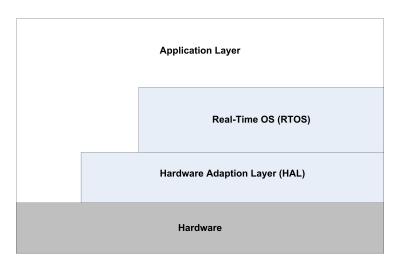

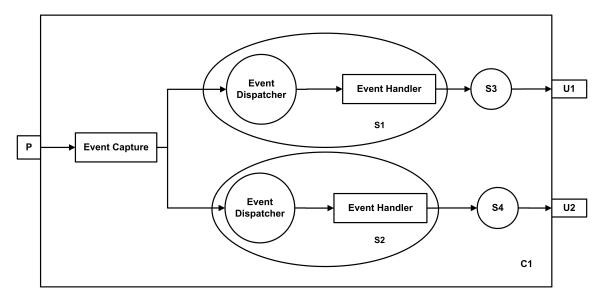

Figure 2.1: Structure of an embedded system

Embedded systems are designed to perform specific tasks in a particular computational environment consisting of software and hardware components. Figure 2.1 illustrates the typical structure of such a system in terms of four layers.

An application layer consists of software that satisfies application requirements; applications layers that use services from underlying layers, including the Real-Time Operating System (RTOS) and Hardware Adaptation Layer (HAL).

An RTOS consists of task management, interrupt handling, inter-task communication, and memory management facilities [71] that allow developers to create embedded system applications that meet functional requirements and deadlines using provided libraries and APIs.

The hardware adaptation layer is a runtime system that manages device drivers and provides hardware interfaces to higher level software systems—applications and RTOSs.

Interactions between different layers play an essential role in embedded system application execution. An application layer consists of multiple user tasks that execute in parallel, sharing common resources like CPU, bus, memory, device, and global variables. Interactions between application layers and lower layers, and interactions among the various user tasks that are initiated by the application layer, flow the information created in one layer to others for processing. Faults in such interactions could result in execution anomalies.

Multitasking is one of the most important aspects in embedded system design, and is managed by the RTOS. Due to thread inter-leaving, embedded systems employing multiple tasks can have non-deterministic output, which complicates the determination of expected outputs for a given input.

Embedded system often functions under real-time constraints, what means the request need be completed within a required time interval from the triggering event [25]. In the real-time domain, the temporal behavior [48] is as important as the functional behavior. Embedded systems can be classified into hard real-time and soft real-time depending on their requirements. Their main difference lies in the cost or penalty for missing their deadlines. Hard real-time embedded systems have strict temporal requirements, in which failure to meet a single deadline may lead to catastrophic outcomes. On the other hand, soft real-time embedded systems are not required to satisfy hard real-time constraints; missing deadlines lead to performance degradation.

## 2.2 Testing Embedded Software

According to statistical studies [37], software accounts for as much as 80% of the functionalities in embedded real-time systems such as home appliances, information appliances, personal assistants, telecommunication gadgets, and transportation facilities. Software is also much more complex than hardware due to its inherent flexibility. It is often found that an on-market real-time embedded system fails due to some simple software glitches, which could have been avoided if the software was thoroughly verified. All these facts show that verifying the correctness of software is a demanding and important issue in the design phase of an embedded real-time system [44].

These features greatly affect software testability and measurability in embedded systems. The term *testability* in software testing can be considered from various viewpoints [12] [17] [23]. While some consider the architectural viewpoints [47] [51], few describe techniques for

more effective design for testability at the architectural level [11] [13]. However, increasing testability is commonly identified as an important goal in software testing research [27].

In embedded software systems, two main viewpoints of testability are considered from the architectural viewpoint: controllability and observability [17]. To test a component, we must be able to control its input, behavior and internal state. To see how this input has been processed, we must be able to observe the components output, behavior and internal states. Finally, the system control mechanisms and observed data must be combined to form meaningful test cases.

Embedded software often generates outputs for hardware to function rather than for users to interact with, so the observability is significantly low. It is easy to control software input values that are entered from a keyboard. But an embedded program that gets its inputs from hardware is more difficult to control. Testability is an important factor in embedded real-time systems, especially when the systems have additional properties that increase the complexity.

Faults in embedded systems can produce effects on program behavior or state that, in the context of particular test executions, do not propagate to output, but do surface later in the field. To detect internal program faults when testing embedded systems is the primary focus of this work.

# 2.3 Component-based Real-time Embedded Software

The embedded systems industry is under competitive pressure to continually shorten its time-to-market, increase product differentiation, and at the same time offer more customer value. As a result, (i) embedded systems are becoming increasingly software intensive, and (ii) individual components integrate increasing functionality over different projects and reuse cycles. Integrating more functions into a single component gives rise to increasingly varying behavior.

During the last decade advances have been made in component-based development for desktop and internet applications. Embedded and real-time systems have requirements not found in desktop systems, including real-time requirements and resource efficiency. This is one reason why embedded and real-time systems have more difficulties adapting to component-based software engineering (CBSE) than desktop systems [35]. A few defacto standards have completely transformed the way such software is developed. These standards are mainly Microsoft's .NET [1], SUN's Enterprise Java Beans [2] and OMG's CORBA Component Model (CCM) [3]. Component models for embedded systems are usually designed with very domain specific requirements in mind [63]. There is a large set of different component technologies that approach different problems in different ways such as the SCA-based Component Framework for Software Defined Radio [50] and many more. For embedded systems it seems difficult to define de-facto standards due to highly diverging requirements in different industrial segments [27].

Software Defined Radio (SDR), developed with the Software Communications Architecture (SCA), is an example of such an effort. SDR refers to reconfigurable or reprogrammable radios that can have different functionality with the same hardware. Because the functionality is defined in software, a new technology can easily be implemented on a radio by updating its software. So a radio can be built to meet the need for continuously changing technology. In an SDR, multiple waveforms can be implemented in software using the same hardware. One software defined radio can communicate with many different radios, with only a change in software parameters. This increases interoperability among different military units, emergency units, and coalition forces. Also new technologies can be adapted to quickly, easily, and with a much lower cost than with the traditional method.

SCA is a common, well-defined open architecture. It is used to build radios that support operations in a wide variety of domains without losing the ability to communicate with each other. It can help radio vendors improve interoperability by providing the ability to share waveform software between radios, and reduce development time through software reuse. This architecture also facilitates scalability and technology insertion.

As an emerging technology in embedded software development, the SCA presents a new paradigm, and it affects the entire embedded software development cycle including analysis, specification, design, implementation, verification, validation and maintenance. However, it introduces a new environment to embedded communication engineers, filled with system software concepts such as object oriented programming, portable operating system interfaces, and middleware using the Common Object Request Broker Architecture (CORBA) [4].

# 2.4 Component-based Real-time Embedded Software Architecture

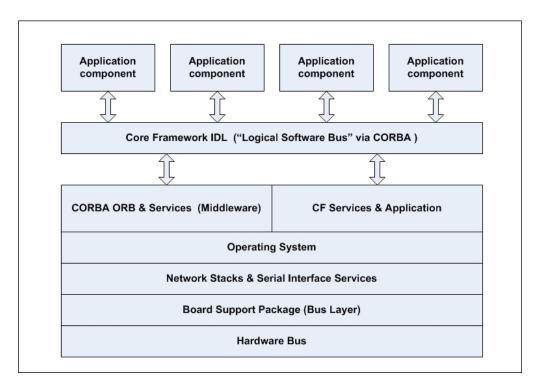

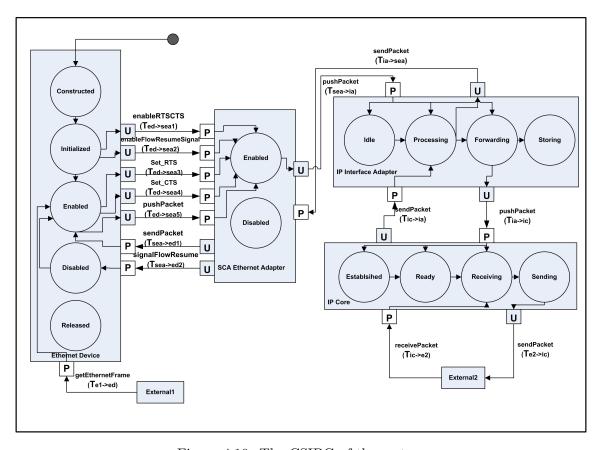

Software Communications Architecture (SCA) [7] is a component-based software architecture specifically designed for real-time embedded communications devices. The SCA structure is composed of an application layer and an operation environment (OE) layer. The software architecture detailed view is shown in Figure 2.2.

Figure 2.2: SCA software architecture detailed view

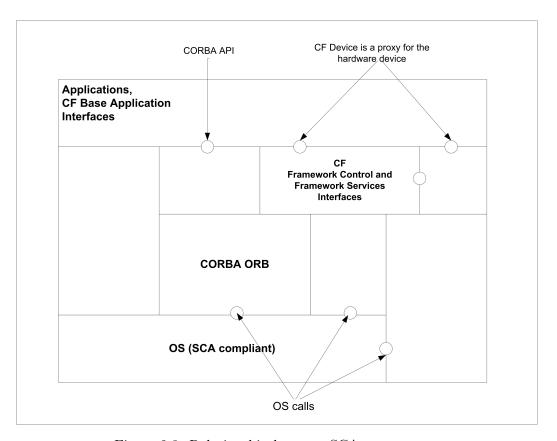

The OE consists of a Core Framework (CF), a CORBA middleware and a POSIX-based Operating System (OS). Since the SCA uses the CORBA middleware, application programs are basically composed of CORBA objects that conform to the SCA core framework. The SCA core framework is composed of the specification of interfaces and a domain profile. A domain profile is composed of XML descriptor files that describe the hardware and software configuration information of a SCA system domain. The OE specifies the services and interfaces that the applications use from the environment. The interfaces are defined by using the CORBA Interface Definition Language (IDL), and graphical representations are made by using UML [38]. Figure 2.3 shows the relationships between the OS, the application, and the OE.

Figure 2.3: Relationship between SCA components

Any component on a radio can be replaced or upgraded, and the download process can be made transparent to the user. In the SCA context, a radio application is known as a waveform, which is defined as the set of transformations applied to information that is transmitted over the air and the corresponding set of transformations to convert received signals back to their information content. The core framework defines a common mechanism to manage and control waveforms and their components. Therefore, components can come from different sources and still use the same mechanisms to be deployed, connected, and managed.

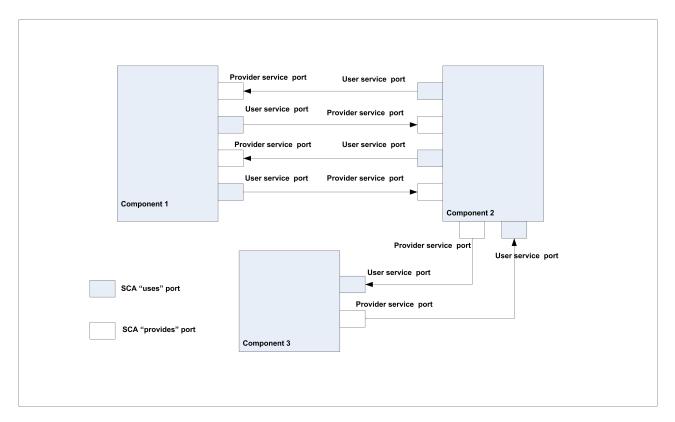

Port provides a specialized connectivity to a component. It is used to set up and tear down connections between application components in the CF domain. Port is a logical element that enables components to exchange data. Ports are classified into Uses ports

(clients) and *Provides* ports (servers). Provides port of a component is used to retrieve an object reference for a server object contained in the component. *Uses* port of a component is used to retrieve an object reference for a proxy object connected with a server object contained in another component. *Port* interface also provides components with connect and disconnect functionalities, which are necessary to assemble waveforms. Figure 2.4 illustrates the connection of components via ports in SCA model.

Figure 2.4: Connection of components via ports

Significant efforts are being carried out to facilitate SCA-based SDR software development on integrated development environments, reusable software modules, and implementations of software architectures. For example, the Open-Source SCA Implementation::Embedded (OSSIE) [82], developed at Virginia Tech for research and education, is an open SCA implementation that can reduce the entry cost of SCA development and training.

But less attention has been brought to finding effective and efficient testing strategies to make such systems more robust and reliable.

# 2.5 Component-based Real-time Embedded Software Design Models

The Unified Modeling Language (UML 2.0) [6] [38] offers a great opportunity to describe component-based embedded systems. It provides constructs to deal with varying levels of modeling abstraction to visualize and specify both the static and dynamic aspects of systems. And with the stereotypes, tagged values, and constraints, the semantics of model elements can be customized and extended. The Object Management Group (OMG) has proposed the Model Driven Architecture (MDA) approach, which aims to allow developers to create systems entirely with models. It provides a set of guidelines to structure specifications expressed as models. Therefore, it is useful and significant to combine the MDA approach and UML models with the component technique to develop software for embedded systems [59].

A model is a formal specification of the function, structure and behavior of a system within a given context, and from a specific point of view (or reference point). A model is often represented by a combination of drawings and text, typically using a formal notation such as UML, augmented where appropriate with natural language expressions.

MDA itself is not a new OMG specification but rather an approach to software development that is enabled by existing OMG specifications such as the Unified Modeling Language (UML), the Meta Object Facility (MOF), and the Common Warehouse Metamodel (CWM).

#### Chapter 3: Related Work

#### 3.1 Related Work

Although a great deal of research has addressed the overall process of component-based software engineering (CBSE) on requirements engineering, design and evaluations, we do not have as much reserach on testing CBSE. Testing CBS is a challenging area of research. Existing knowledge in this field shows that CBSE introduces new problems for testing and maintaining software systems and we need new ways to validate software components, especially when they are integrated into new environments [42] [83] [87].

There are a number of component-based testing methods and techniques which have different paradigms, characteristics and perspectives. This section comprehensively reviews research work related, to provide a key foundation of the literature review. It also identifies the important problems and limitations in the existing component-based integration testing techniques.

Liang et al. [42] proposed a testing technique that is based on analysis of component-based systems from component-provider and component-user perspectives. The technique makes use of complete information from components for which source code is available and partial information from those for which source code is not available. Their approach separated the testing of the component-provider from the testing of the component-user, so it presented two different techniques for each category. Valentini et al. [79] developed a framework based on contract-checkers. It verifies the information between the component producer and the user. This technique was leveraged by Zheng and Bundell [90] with UML-based testing at the modeling level to design model-level test contracts.

Machado et al. [61] presented a UML based approach to integration testing using UML diagrams including the Object Constraint Language. Zheng and Bundel [89] further

extended the work to develop a model-based approach using three techniques, scenario-based, contract-based and component test mapping. Hartmann [43] presented a design-based testing approach to generate test inputs from UML state machines. It models the behavior of each component, specifies component interactions, and annotates the state machines with test requirements to construct a global behavioral model of the composed statecharts. Then, test cases are automatically derived from the annotated statecharts and global behavioral model, and executed to verify component conformance behavior. State machines of individual components are combined and then used to design tests.

Briand et al. have published several research papers on state-base testing with UML statechart diagrams [20] [21] [70]. They proposed to use class diagrams, collaboration diagrams, or OCL to derive test requirements [20]. They also proposed a methodology to automate the derivation of test cases from UML statechart diagrams for a given set of transition test sequences [21]. Their results show that, in most cases, state-based testing techniques are not likely to be sufficient by themselves to detect most of the faults present in the code, and they need to be complemented with other testing methods.

The above approaches use only one kind of behavioral UML model for test generation, either sequence diagrams or state machines. The approach in this dissertation is novel in that it combines the information from component level UML sequence diagrams and statecharts to derive a graph-based test model for the purposes of test input generation.

Wu et al. [87] investigated faults that can be identified at the integration of components. They presented a test model that depicts a generic infrastructure of component based systems and identified key test elements. A Component Interaction Graph is generated from the implementation, in which the interactions and the dependence relationships among components are illustrated. Test adequacy criteria were developed to cover context dependence relationship and content dependence relationship.

While Wu's test elements and test criteria are useful to test component-based software, their work is in the stage of approach development. This paper does not discuss and give practical ways on how to use their approach to generate actual test cases for component-based testing. Their test model mainly illustrates the context/content-dependence relationships defined in the paper. Additional work is required to effectively drive test generation from the test model.

In addition, the authors made several assumptions in their work, including: (i) assuming that each individual component has been adequately tested by the component providers when testing component-based software; (ii) assuming that each interface only includes one operation, and the references to the interfaces and to the operation are identical. These assumptions imply that their work considers only some simplified situations, which could have limitations in applying their approach to actual component-based testing practice.

From the above survey, we note that different kinds of UML diagrams have been used for software testing from different perspectives. UML state charts have been widely used to test the state-based behavior of software. Similarly, UML interaction diagrams have been used for integration testing. However, existing approaches do not focus on exercising the composition behavior of interacting components. More specifically, none of the above papers discuss testing by integrating UML interaction and statechart diagrams to uncover component interaction faults.

The approach in this dissertation uses UML statecharts and sequence diagrams from software architecture and design models to generate an intermediate model, the Component-based Real-time Embedded Architecture-based Test Model (CREATEG), and applies different coverage criteria based on the CREATEG graph representation. We use sequence diagrams to determine the order of messages between components.

There has been a great deal of work on using dataflow-based testing approaches to test interactions among system components [86] [56] [45] [68]. However, none of this work has addressed problems in testing embedded systems or studied the use of such algorithms on these systems. While we employ analyses similar to those used in these papers, we direct them at specific interactions within embedded systems.

Integration testing based on scenarios using finite state machines is discussed by Li

et al. [55]. The work was furthered extende by Bouaziz and Berrada to test real time component-based systems [18].

In an embedded system, extra-functional requirements are as important as functional requirements. A real-time embedded system needs to achieve its functionality under the constraints caused by its extra-functional properties. Therefore, they should be considered while testing embedded software behavior. Due to this specialty, the adoption of the component-based testing approach to the embedded system has encountered difficulties. For example, an important part of extra-functional characteristics of many embedded systems is timing requirements. It is difficult to describe timing requirements in models traditionally used in component-based design. Also, the tight integration between hardware and software makes it hard to model and implement software separately from hardware. Component integration testing in an embedded system cannot be solely achieved by examining components' behaviors through their interfaces. When modeling real-time systems, timing aspects and constraints become essential. Testing component-based real-time embedded systems is even more challenging than testing untimed reactive systems.

Few component-based testing models incorporate component extra-functional behavioral aspects in their frameworks.

Bouaziz and Berrada [19] proposed an aproach to model and test component-based real-time systems. To avoid constructing an entire system, they seperate the individual behavior of components from their interactions. They use a particular component called the assembly controller to model intra-component interactions, and only test relevant behaviors related to intra-component synchronizations. An assembly controller is a particular type of Timed Inout/Output Automata (TIOA) used to restrict the overall behavior of the composite system to ensure a correct interaction between components.

The most popular approaches for specifying real-time systems are based on Timed Automata [60]. It is a graph containing a finite set of nodes and a finite set of labelled edges extended with clocks. UPPAAL is a commonly used automatic verification tool for timed automata [46]. It is very good at modelling by providing a simulator and a well-developed

GUI, but the tool provides only binary synchronization between processes and can only verify reachability properties. Larsen et al. [53] created a number of small academic specifications and implementations to evaluate an online testing tool named UPPAAL-TRON for real-time systems [52]. An embedded system industrial case has been evaluated by Mikucionis et al. [62]. They found that real-time online testing is an effective way to detect discrepancies between the model and the implementation in practice. However, large and very non-deterministic models can run into state explosions, making it problematic to update the state-set in real-time. This may limit the granularity of time constraints that can be checked in real-time. All the above approaches are formal verification methods to prove conformance with a predefined specification. The goal is to check whether an extracted model satisfies a certain specification. My test method, in contrast, defines input data to the object program and observes the reactions of the program. The goal of my testing is to find cases where the software reactions do not meet its expected results.

There has also been research on component-based software engineering for embedded systems such as [26], which focused on embedded software. There has been work on using informal specifications to test embedded systems focusing on the application layer. Tsai et al. [75] presented an approach to test embedded applications using class diagrams and state machines. Cunning and Rozenblit [29] generated test cases from finite state machine models built from specifications. Sung et al. [72] tested interfaces to the kernel via the kernel API and global variables that are visible in the application layer. All of these papers focused on the application layer, while my approach applies the technique on the components across all the layers: application layer, hardware adaption layer, and operating system infrastructure layer.

To consider extra-functional requirements impact into the component integration level testing, I introduce additional notations in my testing model to integrate timing requirements. The generated test cases are annotated with real-time constraints. In contrast with the above models, my approach tests both functional and non-functional behavior.

Even though the empirical study of testing techniques has made some progress in recent

years, studies of embedded systems have not. Many of the papers cited in this section on testing embedded systems include no empirical evaluation at all. My research work described in this dissertation goes beyond most of this prior work by examining fault detection capabilities relative to the use of techniques in an industrial real-time embedded system.

In UML, the notion of time is not clearly defined for the design of RTE systems. The UML profile for modeling and analysis of real-time and embedded systems (MARTE) has been proposed and was adopted as an Object Management Group (OMG) specification [40] [15] [88]. In comparison, MARTE presents time in a more precise and clear manner. A new clock constraint language (CCSL) is used in MARTE to specify chronometric and logical time constraints. A chronometric clock implicitly refers to physical time and a logical clock mainly addresses concrete instant ordering [73] [31] [16]. Although MARTE is capable of modelling logical and chronometric time, it does not specify the dynamic behavior of integration systems [58].

Kanstren [49] presented a study on design for testability in component-based embedded software based on two large-scale companies in the European telecom industry. He discussed Design for Testability (DFT) solutions to support test automation from two European telecommunications companies, working on similar large scale component-based embedded systems. Their techniques to support effective test automation were discussed. A common communication protocol provides support for implementing reusable test components. Especially in the case of embedded systems, a good host test environment enables efficient software testing. When this environment matches the target system as much as possible, efficient host testing is possible. One way to support testing is to use an operating system that is supported on both the target hardware and in a host-testing environment, as simulated on a desktop. Including support for test automation as a first-class feature allows more effective analysis of the system, including analysis of long running tests and deployed systems, and enables efficient field-testing. Effectively implementing this requires possibilities for dynamic configuration of test functionality during execution. Abstracting test cases from the implementation minimizes the effects of internal system changes to the

test cases. This mostly applies at the system testing level, as in earlier testing phases it is often necessary to observe more detailed properties of the system.

Kanstren's methods addressed test automation and the different techniques to make this more effective at the architectural level. But they were still limited to regular functional testing to fulfill system requirements instead of designing a formalized and abstract structured testing model.

## Chapter 4: A Component-based Real-time Embedded Software Architecture and Design Based Testing Technique

The Object Management Group (OMG) has proposed the Model Driven Architecture (MDA) approach, which allows developers to create systems entirely with models. It provides a set of guidelines to structure specifications expressed as models [81]. MDA itself is not a new OMG specification but rather an approach to software development that is enabled by existing OMG specifications such as the Unified Modeling Language (UML), the Meta Object Facility (MOF), and the Common Warehouse Metamodel (CWM). The Unified Modeling Language (UML 2.0) [6] [38] allows designers to describe component-based embedded systems. It provides constructs to deal with varying levels of modeling abstraction to visualize and specify both the static and dynamic aspects of systems. And with the mechanisms of stereotypes, tagged values, and constraints, the semantics of model elements can be customized and extended. Therefore, it is useful and significant to combine the MDA approach and UML models to develop software testing technique for component-based embedded systems.

Component-based modeling supports the representation of substantial aspects of the software architecture views as structural models, which consist of components and their relationships. It represents the static configuration of a system through the dependencies and connections between components. It includes details of the interface, such as data structures, services, and physical characteristics, on different abstraction levels. Behavioral models are used to describe the dynamic aspects of the components, component interaction, and resource constraints. It can be divided into component-interaction parts, which show the messages (behavior name and message parameters) sent between components, and state

transition parts, which present the state transitions inside each component or the interactions between the components. It also shows dynamic aspects such as tasks, services, and operating conditions to provide scheduling information.

Functional models specify functionality of a component such as data flows, control flows and functional relations. The run-time interaction of a component-based real-time embedded system is modeled by well-defined sequences of messages passed among component level sequence diagrams. Component level sequence diagrams are interaction diagrams consisting of a set of components and their relationships, including the messages that may be dispatched among them, as well as interactions with external system. Sequence diagrams address the dynamic view of a system by emphasizing the time-ordering of messages.

In many cases, the states of the components sending and receiving a message at the time of message passing strongly influence their behavior:

- A component receiving a message can provide different functionalities from different states

- Certain functionalities may not be available if the receiving component is not in the right state

- The functionalities provided by a component may depend on the states of other components including the sending component of a message

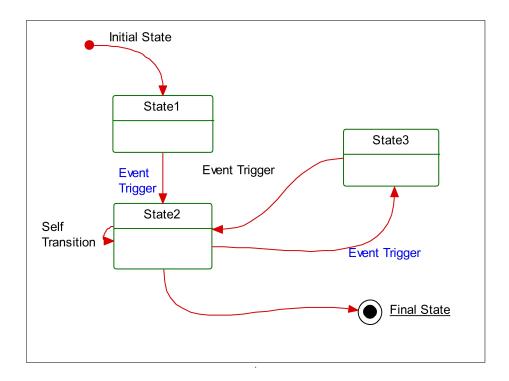

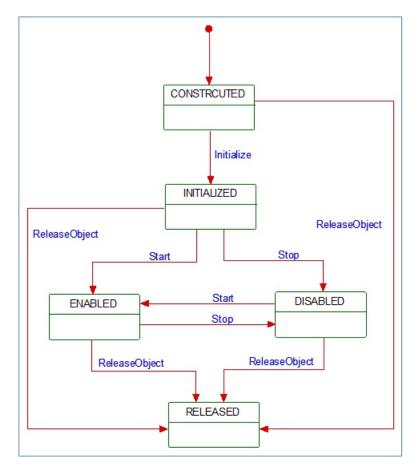

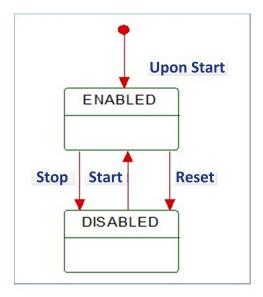

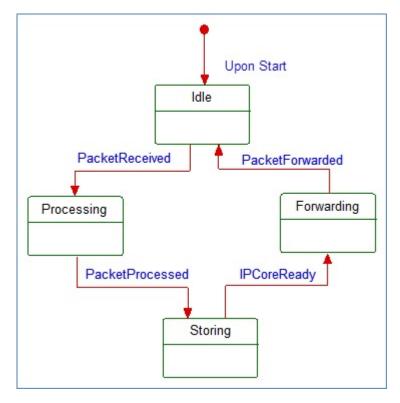

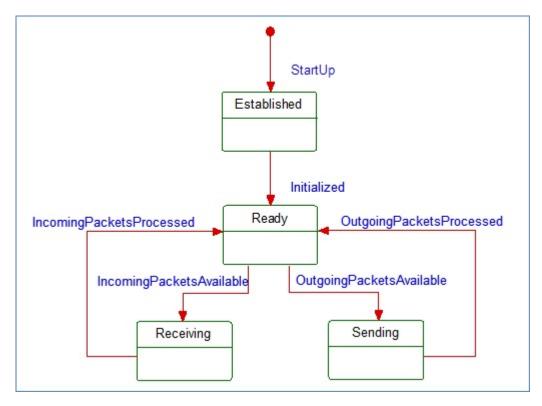

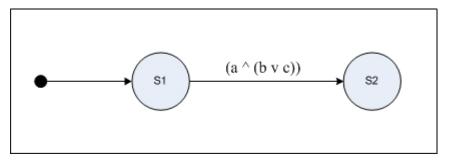

UML state diagrams are useful modeling tools in certain domains, such as embedded software development. State diagrams are the de-facto accepted industry standard for modeling the behavior of distributed reactive systems [30]. The UML state machine diagram is used to model discrete behavior of a component through finite state transition. A system that is described by a UML state machine contains states at a particular time. A state machine is a behavior that specifies the sequence of states an object visits during its lifetime in response to events, together with its responses to those events. A state is a condition that satisfies some condition, performs some activity, or waits for some external event. They are connected by transitions. System states can be changed if the system receives a trigger

associated with the current states. An event is the occurrence of a stimulus that can trigger a state transition. The trigger will activate a transition that is adjacent to the current states. If the trigger fires a transition, the current state will move to the next state. A transition is an edge that connects states. It is a relationship between two states indicating that an object in the current state will, when a specified set of events and conditions are satisfied, perform certain actions and enter the next state. Each transition has four components: transition name, trigger, guard condition, and action expression [6] [38]. Figure 4.1 presents a simple state diagram.

Figure 4.1: A simple state diagram

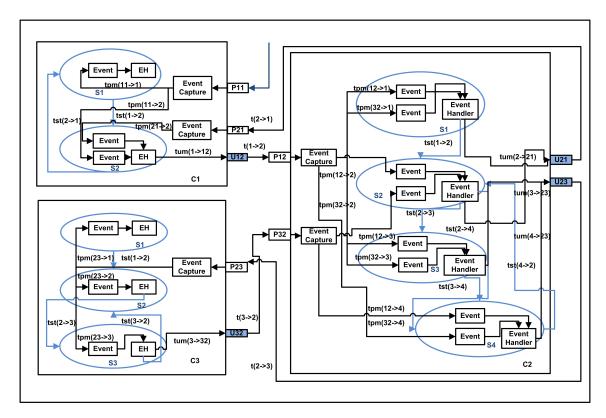

This research proposes an integration testing technique that is based on the idea that the interactions between components should ideally be exercised for all possible states of the components involved. This is of particular importance for component-based real-time embedded software as many components exhibit state-dependent behavior. This testing research objective is achieved by generating a graph-based test model called Component-based Real-time Embedded Architecture-based TEst Graph (CREATEG) and by covering paths in the model.

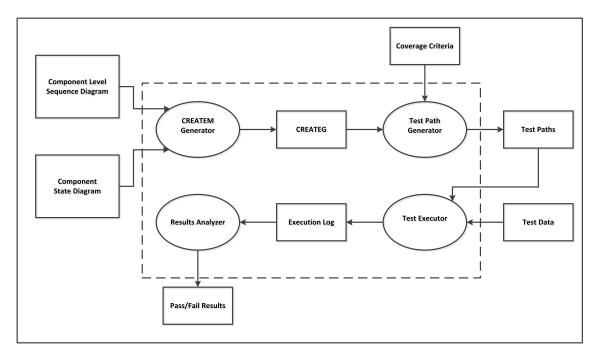

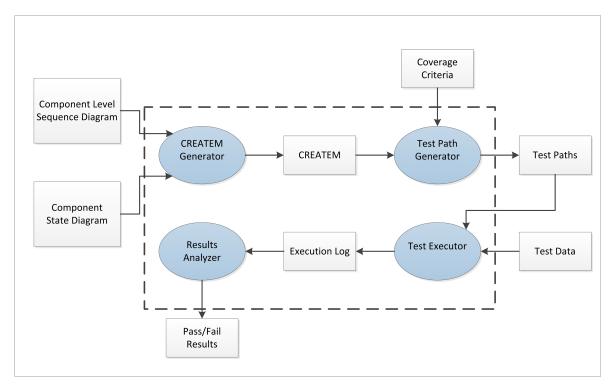

The proposed technique can be applied during the integration test phase, after the completion of component testing. It consists of the following four steps:

- 1. CREATEG Generation: The intermediate test model CREATEG is constructed from a component interaction sequence diagram and its corresponding state diagrams.

- 2. Test Paths Generation: Test paths are generated from the CREATEG based on several possible alternative coverage criteria.

- 3. Test Execution: All selected test paths are executed by using manually-generated test data and an execution log is created, which records component states before and after execution of each message in a test path.

- 4. Result Evaluation: The object states in the execution log are compared with the expected object states in the test paths generated from CREATEG. If a test path does not generates the required resultant state, then the corresponding test case is considered to have failed.

Figure 4.2: Flowchart for the proposed testing technique

Figure 4.2 presents a flowchart for the proposed technique, which shows the above four phases and their relationships with various artifacts. The following sub-sections describe the proposed testing technique in greater detail with the help of a simple example.

### 4.1 The CREATEG Model

The CREATEG is a test model used to automatically generate test specifications for component integration testing. In this sub-section, we describe how this test model is constructed from a given UML sequence diagram and its corresponding state diagrams. We have, however, made some assumptions about these UML models:

- Sequence diagrams are available that show critical scenarios of system operation.

- State diagrams are available that specify states and transitions for each component.

- Sequence diagrams may contain synchronous call messages or asynchronous signal messages.

- States in the component that are relevant to the selected sequence diagram are specified.

- All guards and conditions are evaluated together with events for generating state transitions.

In a component-based embedded system, applications are built as a collection of interconnected components, which are transformed into executable units such as tasks that can be managed by the underlying real-time operating system. The execution time of a component does not only depend on the component behavior but also on the time-constraint and platform characteristics. For example, each task is assigned with a priority. Higher priorities are assigned to tasks that have real-time deadlines. The impact of the extra-functional characteristics to a component integration test can be illustrated in the following example:

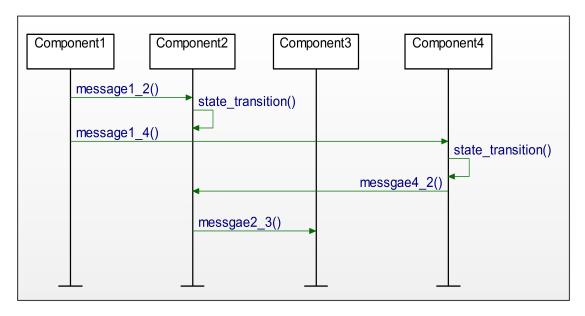

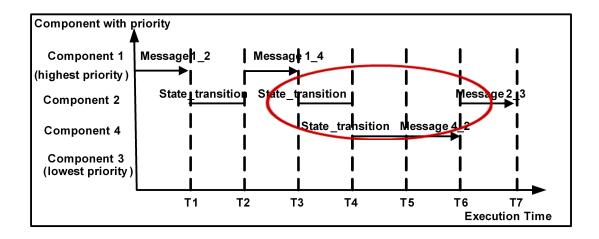

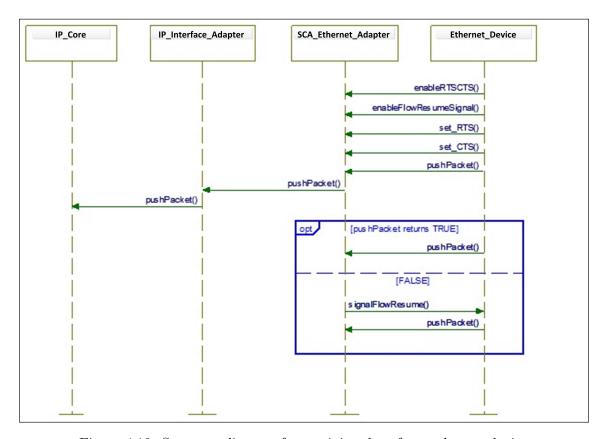

Sequence diagram 4.3 shows four components that interact through messages. Upon receiving a message, each component reacts with a sequence of events, changing states and sending messages to other components. Each component maps to a task and gets its computing resource based on its task's priority.

Figure 4.3: A component level sequence diagram

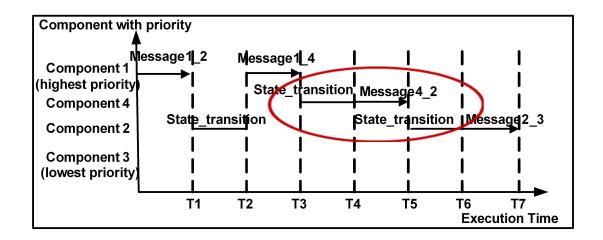

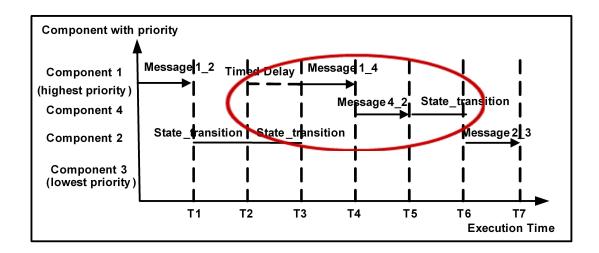

Figures 4.4, 4.5, and 4.6 demonstrate three different senarios. In all three figures, Component1's task is assigned the highest priority while Component3's task is assigned the lowest priority. In Figure 4.4, when Component4's task's priority is higher than Component2's, Component2 may not complete its state transition before Component4 finishes its state transition and calls Message4\_2(). On the other hand, in Figure 4.5, when Component4's task's priority is lower than Component2's, Component2 will complete its state transition before Component4 starts its state transition and calls Message4\_2(). In Figure 4.6, a timed delay is added between Message1\_2() and Message1\_4(), even through Component2's task has lower priority than Component4's task. Thus, Component2 will complete its state transition before Component4 starts its task.

Figure 4.4: Component interaction scenario 1

Figure 4.5: Component interaction scenario 2

Figure 4.6: Component interaction scenario 3

To consider how extra-functional requirements impact component integration level testing, this test model introduces additional timing notations. They are placed onto the graphs that are defined in the next section.

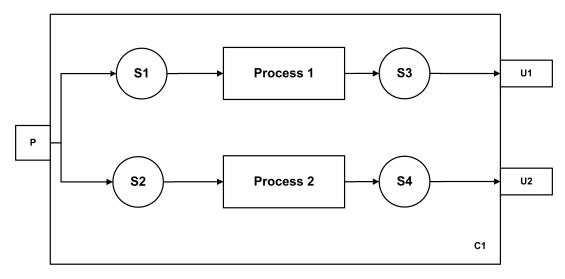

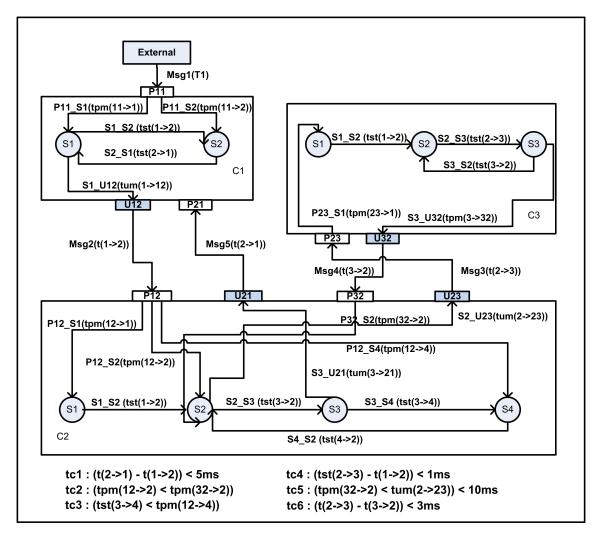

The CREATEG is a multi-graph structure composed of the Component Interface Interaction Graph (CIIG), the Component State-based Interaction Behavior Graph (CSIBG), and the Component State-based Event-driven Interaction Behavior Graph (CSEDIBG), each of which is described below.

### 4.1.1 Component Interface Interaction Graph (CIIG)

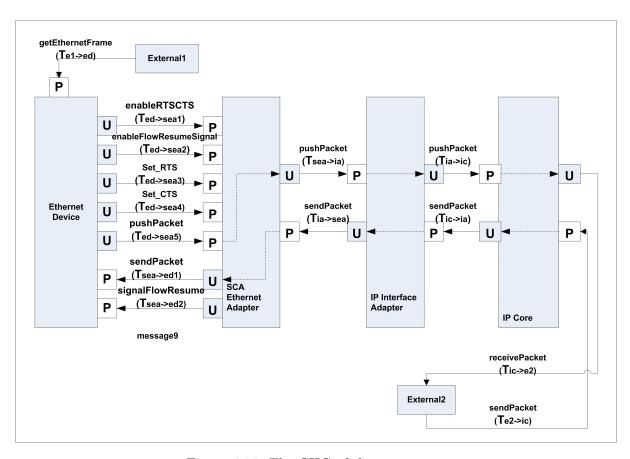

Here I first introduce a graphical representation of the interactions between real-time embedded system components. Components in this graph not only include application layer components but also hardware adaption layer and infrastructure layer components. Interactions involve message exchanges occur at specific times.

A CIIG represents the time-dependent connectivity relationships between these components as well as time-dependent relations inside a component and a component interface. A

CIIG is composed of a set of components (visually as rectangular boxes), component interfaces (small rectangular boxes on the edge of the component boxes), connections between components (solid arrows), connections inside components (dash-line arrows), and times when connections happen.

Definition 1 (Correlated Components). If two components are connected through an interface message, these two components are correlated. The component that initiates the interface message is the sending component, while the component that accepts the interface message is the receiving component. A component has to provide at least one interface to specify the dependencies between the services provided by the component and the services required to fulfill its task. Two components can interact during execution if their provided and required interfaces are associated by exchanging data. Component interfaces can be categorized into two groups: provider interfaces and user interfaces.

In real-time embedded software, a layered architecture of basic software modules comprises communication modules, an operating system, and modules that access microcontroller peripheral devices as well as a component based infrastructure for application components.

**Definition 2** (**Provider/Callee Interfaces**). A provider interface in a component provides a function service for the other components to call and to transfer information to this component. A provider interface specifies the same types of elements as a user interface that it provides to the systems.

**Definition 3** (User/Caller Interfaces). A user interface specifies variables, messages, services, calibration parameters, and other software elements required for the component to execute. A user interface in a component connects the other components by calling their provider services.

**Definition 4** (Message Edges). A message edge represents a connection between two interfaces. The message edges in the CHG are of two types: internal message edges and external message edges.

- 1. An **external message edge** represents a call action between two components. It is a connection from the sending component's user interface to the receiving component's provider interface.

- 2. An **internal message edge** represents a direct or indirect interface relationship within a component. It is a connection from the receiving component's provider interface to its own user interface. Component internal flow refers to a message sequence within a software component. This information helps to identify the dependencies of an output of a component on its input values.

**Definition 5** (**Time Instants**). A time instant is an observation point when a specific event happens. It is an instant of a physical time or logical clock. A physical clock is a chronometric clock. A logical clock is a finite set of instants, which are ordered for discrete time clocks and indexed by natual numbers. For example, a logical clock can be represented as the number of frames passed since the start up of the systems. Time duration represents distances between time points.

**Definition 6** (Message Sequences). A message sequence is a sequence of message edges representing a system operation. External message edges and internal message edges together comprise a message sequence.

In a message sequence, message edges can represent synchronous (blocking) or asynchronous (non-blocking) method calls.

During a synchronous method call the thread of execution changes from the component with the required interface to the component with the provided interface until the latter has finished its task. The synchronous method call completes and the thread of execution returns to the first calling component.

When a component sends an asynchronous message, it can continue processing and does not have to wait for a response. Asynchronous calls are commonly seen in multithreaded applications and in message-oriented middleware. Asynchrony gives better responsiveness and reduces the temporal coupling but is harder to design and test. **Definition 7** (Component Interface Interaction Graph (CIIG)). Given a software architecture defined by a specific UML sequence diagram, the Component Interface Interaction Graph (CIIG) is defined as:

$CIIG = (C, C\_P\_Interf, C\_U\_Interf, C\_In\_edge, C\_Ex\_edge, T\_Ex\_edge, TC)$

- $C = \{C_1, C_2, \ldots, C_m\}$ , a finite set of components

- $C\_P\_Interf = \{C_i.P_1, C_i.P_2, \ldots, C_i.P_n\}$ , a finite set of provider interfaces in component  $C_i, i \in \{1, 2, ..., m\}$

- $C\_U\_Interf = \{C_i.U_1, C_i.U_2, \ldots, C_i.U_n\}$ , a finite set of user interfaces in component  $Ci, i \in \{1, 2, ..., m\}$

- $C\_In\_edge = \{C_i.P \rightarrow C_i.U\}$ , a finite set of internal component message edges  $i \in \{1, 2, ..., m\}$

- $C\_Ex\_edge = \{C_i.U \rightarrow C_{i+1}.P\}$ , a finite set of external component message edges  $i \in \{1, 2, ..., m\}$

- $T\_Ex\_edge = \{t(i \rightarrow_j)\}$ , a finite set of time stamps at external component message edges  $i \in \{1, 2, ..., m\}$ ,  $j \in \{1, 2, ..., m\}$

- $TC = \{tc_i\}$  is a finite set of time constraints on components internal messages  $i \in \{1, 2, ..., n\}$ ,  $j \in \{1, 2, ..., m\}$ ,  $tc_i = (tst_i \lor tpm_i \lor tum_i) (tst_j \lor tpm_j \lor tum_j)$  rop  $c, c \in Integer$ , rop  $\in \{<, \leq, =, >, \geq\}$

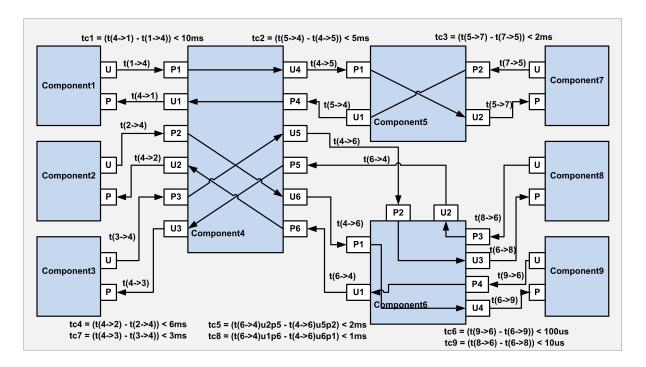

As an example, consider a software system that consists of nine components.

Figure 4.7: A software system that consists of multiple componentse