# $\frac{\text{A TECHNICAL REPORT ON}}{\text{KEY MANAGEMENT AND VULNERABILITY ASSESSMENT}} \\ \frac{\text{OF LOGIC OBFUSCATION}}{\text{OF LOGIC OBFUSCATION}}$

Kimia Zamiri Azar

Department of Electrical and Computer Engineering (ECE) George Mason University, Fairfax, VA

Copyright © 2019 by Kimia Zamiri Azar All Rights Reserved

# Table of Contents

|                                        |        |                           |                                                   | Page |  |  |  |  |  |  |

|----------------------------------------|--------|---------------------------|---------------------------------------------------|------|--|--|--|--|--|--|

| Lis                                    | t of T | ables                     |                                                   | . v  |  |  |  |  |  |  |

| Lis                                    | t of F | igures .                  |                                                   | . 0  |  |  |  |  |  |  |

| 1 Introduction to Hardware Obfuscation |        |                           |                                                   |      |  |  |  |  |  |  |

| 2                                      | Thr    | eats on                   | Logic Locking: A Decade Later                     | . 7  |  |  |  |  |  |  |

|                                        | 2.1    | Stage                     | 1: Test-Based Attacks                             | . 8  |  |  |  |  |  |  |

|                                        |        | 2.1.1                     | Brute Force Attack                                | . 8  |  |  |  |  |  |  |

|                                        |        | 2.1.2                     | Sensitization Attack                              | . 8  |  |  |  |  |  |  |

|                                        |        | 2.1.3                     | Random-based Hill-Climbing Attack                 | . 9  |  |  |  |  |  |  |

|                                        | 2.2    | Stage                     | 2: SAT Attack                                     | . 10 |  |  |  |  |  |  |

|                                        | 2.3    | Stage                     | 3: Post-SAT Attacks                               | . 11 |  |  |  |  |  |  |

|                                        |        | 2.3.1                     | Removal Attack                                    | . 12 |  |  |  |  |  |  |

|                                        |        | 2.3.2                     | Signal Probability Skew (SPS) Attack              | . 12 |  |  |  |  |  |  |

|                                        |        | 2.3.3                     | Bypass Attack                                     | . 13 |  |  |  |  |  |  |

|                                        |        | 2.3.4                     | AppSAT Attack                                     | . 14 |  |  |  |  |  |  |

|                                        |        | 2.3.5                     | Double-DIP Attack                                 | . 14 |  |  |  |  |  |  |

|                                        |        | 2.3.6                     | Bit-Flipping Attack                               | . 14 |  |  |  |  |  |  |

|                                        |        | 2.3.7                     | AppSAT Guided Removal Attack                      | . 15 |  |  |  |  |  |  |

|                                        |        | 2.3.8                     | Sensitization Guided SAT Attack                   | . 16 |  |  |  |  |  |  |

|                                        |        | 2.3.9                     | Functional Analysis Attack                        | . 17 |  |  |  |  |  |  |

|                                        |        | 2.3.10                    | CycSAT Attack                                     | . 18 |  |  |  |  |  |  |

|                                        |        | 2.3.11                    | Behavioral SAT (BeSAT) Attack                     | . 20 |  |  |  |  |  |  |

|                                        | 2.4    | Stage                     | 4: SMT Attack                                     | . 20 |  |  |  |  |  |  |

|                                        | 2.5    | Discus                    | ssion & Opportunities                             | . 23 |  |  |  |  |  |  |

| 3                                      | SM'    |                           | ek: Next Generation Attack on Obfuscated Circuits |      |  |  |  |  |  |  |

|                                        | 3.1    | Boolean Logic Obfuscation |                                                   |      |  |  |  |  |  |  |

|                                        | 3.2    |                           | ioral logical obfuscation                         |      |  |  |  |  |  |  |

|                                        | 3.3    |                           | x Model                                           |      |  |  |  |  |  |  |

|                                        | 3.4    |                           | ation of SAT Attack                               | 30   |  |  |  |  |  |  |

|    | 3.5    |         | olver                                                                            |

|----|--------|---------|----------------------------------------------------------------------------------|

|    |        |         | SMT Usage and Capabilities                                                       |

|    | 3.6    |         | attack                                                                           |

|    |        |         | Attack Mode 1: SMT reduced to SAT Attack                                         |

|    |        |         | Attack Mode 2: Eager SMT Attack                                                  |

|    |        |         | Attack Mode 3: Lazy SMT Attack                                                   |

|    |        |         | Attack Mode 4: Accelerated Lazy SMT Attack (AccSMT) 46                           |

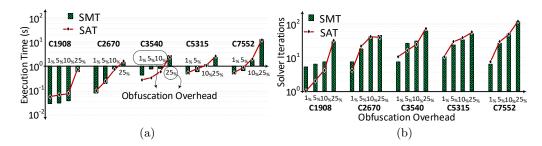

|    | 3.7    | •       | mental Results                                                                   |

|    |        |         | Evaluation of SMT reduced to SAT Attack                                          |

|    |        |         | Evaluation of Eager SMT Attack                                                   |

|    |        | 3.7.3   | Evaluation of Lazy SMT Attack                                                    |

|    |        | 3.7.4   | Evaluation of Lazy AccSMT Attack                                                 |

| 4  | CO     | MA: Coi | mmunication and Obfuscation Management Architecture 61                           |

|    | 4.1    | Backgr  | ound                                                                             |

|    | 4.2    | Propos  | ed COMA Architecture                                                             |

|    |        | 4.2.1   | 2.5 D-COMA: Protecting $2.5 D$ package integrated system solutions $$ . $$ $$ 64 |

|    |        | 4.2.2   | R-COMA: Protecting IoT devices                                                   |

|    | 4.3    | Implem  | nentation Detail of COMA                                                         |

|    |        | 4.3.1   | Configurable Switching Network (CSN)                                             |

|    |        | 4.3.2   | Authenticated Encryption with Associated Data                                    |

|    |        | 4.3.3   | Random Number Generator (RNG)                                                    |

|    |        | 4.3.4   | PUF and Secure PUF Readout                                                       |

|    | 4.4    | COMA    | Resistance against various Attacks                                               |

|    |        | 4.4.1   | Assumed Attacker Capabilities                                                    |

|    |        | 4.4.2   | Reverse Engineering                                                              |

|    |        | 4.4.3   | Algebraic Attacks                                                                |

|    |        |         | Counterfeiting and Overproduction                                                |

|    |        |         | Removal attacks                                                                  |

|    | 4.5    |         | Implementation Results                                                           |

|    |        | 4.5.1   | COMA Area Overhead                                                               |

|    |        | 4.5.2   | COMA Performance                                                                 |

|    |        | 4.5.3   | COMA performance in LCC mode                                                     |

|    | 4.6    | Compa   | ring COMA with Prior Work                                                        |

| Pi | hliogr | anhv    | 90                                                                               |

# List of Tables

| Table |                                                                                       | Page |

|-------|---------------------------------------------------------------------------------------|------|

| 2.1   | Classification of KGs in Sensitization Attack                                         | 9    |

| 2.2   | Comparison of proposed attacks/defenses                                               | 24   |

| 3.1   | ISCAS-85 Benchmarks and their Characteristics                                         | 52   |

| 3.2   | Execution Time of SAT vs SMT (Attack Mode 1)                                          | 53   |

| 3.3   | Execution Time of SMT Attack in the Eager Mode (Attack Mode 2)                        | 54   |

| 3.4   | Execution Time of SMT Attack in the Lazy Mode (Attack Mode 3)                         | 56   |

| 3.5   | Comparing the AccSMT (Attack Mode 4) with the Original SAT Attack                     | 56   |

| 3.6   | Execution Time and the Number of Iterations of AccSMT (Attack Mode 4).                | 59   |

| 4.1   | Main features of the two proposed COMA variants                                       | 80   |

| 4.2   | Resource Utilization of the COMA Architecture                                         | 81   |

| 4.3   | Resource Utilization for ASIC implementation of COMA                                  | 82   |

| 4.4   | Optimized results of COMA Architecture                                                | 82   |

| 4.5   | $\operatorname{SAT}$ Execution Time on Blocking CSN and a Close to Non-blocking CSN . | 84   |

| 4.6   | COMA vs. FORTIS.                                                                      | 86   |

| 4.7   | Area Overhead of COMA vs. FORTIS                                                      | 86   |

# List of Figures

| Figure |                                                                               | Page |

|--------|-------------------------------------------------------------------------------|------|

| 2.1    | Categorization of attacks against logic locking schemes                       | 7    |

| 2.2    | SAT Attack Iterative Flow                                                     | 11   |

| 2.3    | Flipping Structure of SARLock and Anti-SAT                                    | 12   |

| 2.4    | SFLL-HD while $h = 0. \dots \dots \dots \dots \dots$                          | 19   |

| 3.1    | 10-Year History of Logic Obfuscation                                          | 27   |

| 3.2    | ASIC Design Flow Integrated with Obfuscation/Activation                       | 30   |

| 3.3    | Overall Structure of Tunable Delay Key-Gate (TDK)                             | 31   |

| 3.4    | Overall Architecture of SMT Attack for Circuit Deobfuscation                  | 35   |

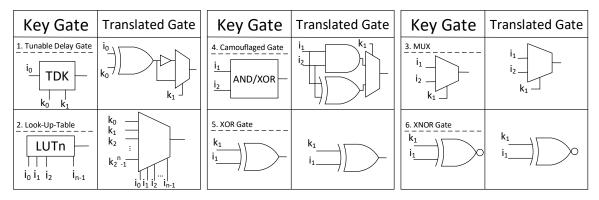

| 3.5    | Translation Table to Key Programmable Gates (KPG)                             | 35   |

| 3.6    | From Obfuscated Circuit to SAT Circuit                                        | 37   |

| 3.7    | SMT Execution Flow                                                            | 38   |

| 3.8    | Conversion Flow in SMT using Graph Theory Solver                              | 39   |

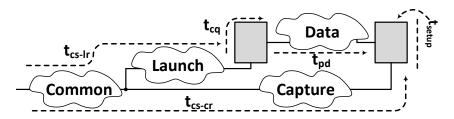

| 3.9    | Various Delay Components of a Timing Path                                     | 40   |

| 3.10   | A Hybrid Obfuscation Scheme                                                   | 49   |

| 3.11   | Comparing the Performance of SMT-attack with that of original SAT-attack.     | . 53 |

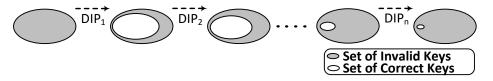

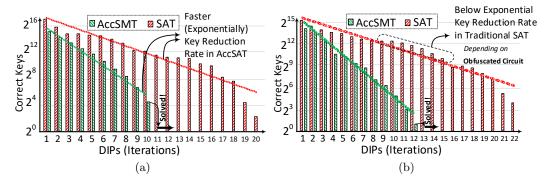

| 3.12   | Set of potentially valid keys reduces in each iteration of SMT or SAT attack. | 58   |

| 3.13   | Key Reduction Rate of the Original SAT Attack and the AccSMT Attack.          | 58   |

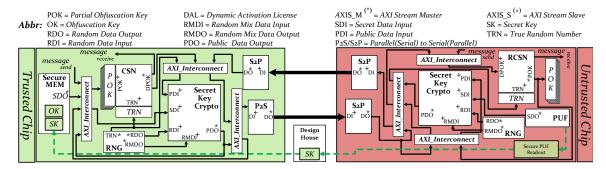

| 4.1    | FORTIS: Overall Architecture                                                  | 63   |

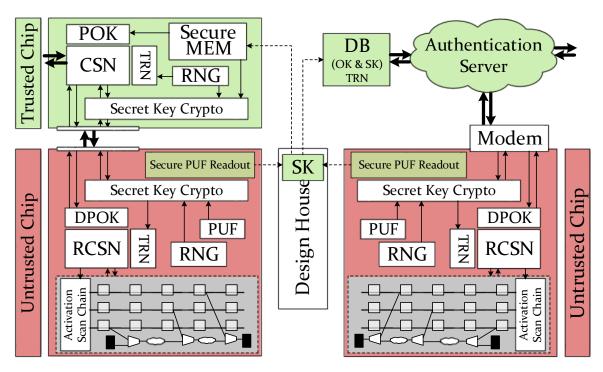

| 4.2    | Proposed COMAs for (left) 2.5D and (right) IoT-based/remote devices. $$       | 65   |

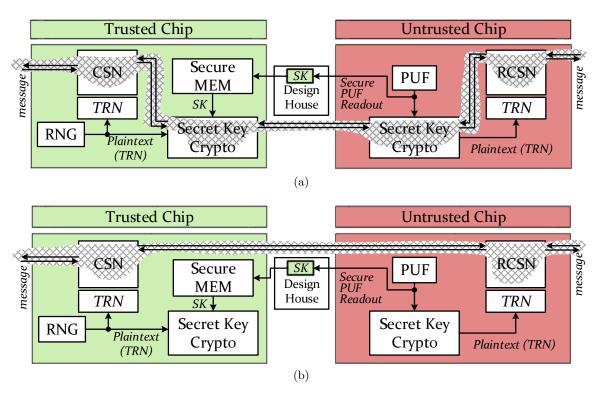

| 4.3    | Modes of Encrypted Communication in COMA: (a) DCC, (b) LCC                    | 68   |

| 4.4    | 2.5D-COMA Architecture                                                        | 69   |

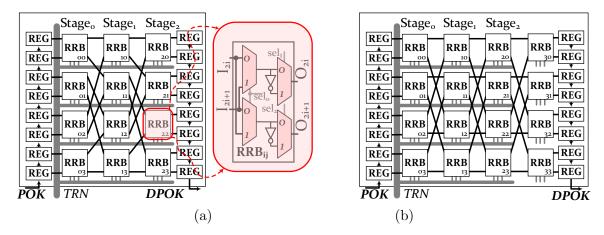

| 4.5    | Logarithmic Network (a) Omega-based Blocking, (b) near Non-blocking           | 71   |

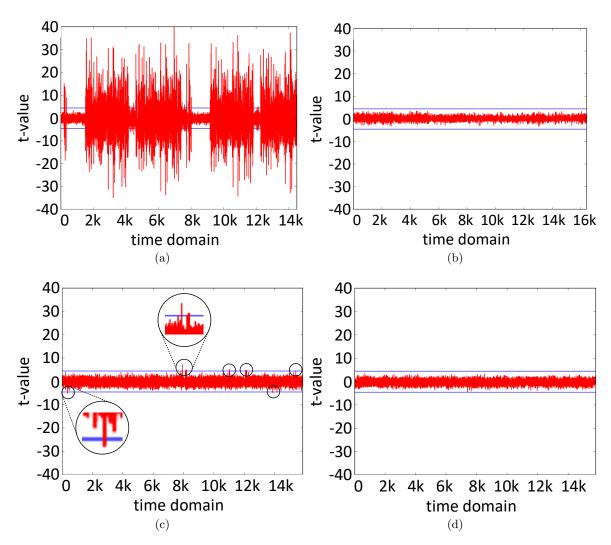

| 4.6    | The t-test Results for Pr and UnPr version of AES-GCM and ACORN. $$           | 77   |

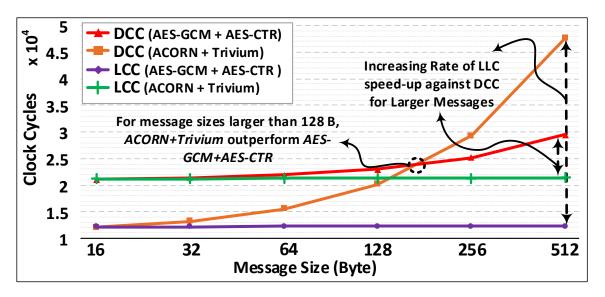

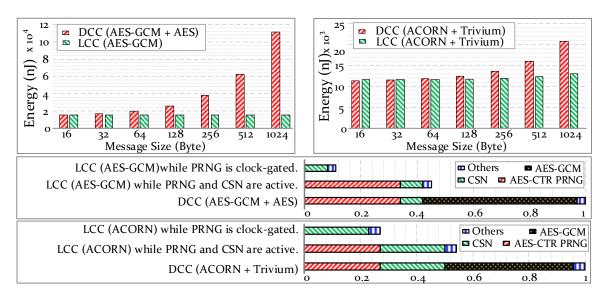

| 4.7    | Total Execution Time for AES-GCM $+$ AES-CTR and ACORN $+$ Trivium.           | 83   |

| 4.8    | Energy Breakdown in COMA                                                      | 85   |

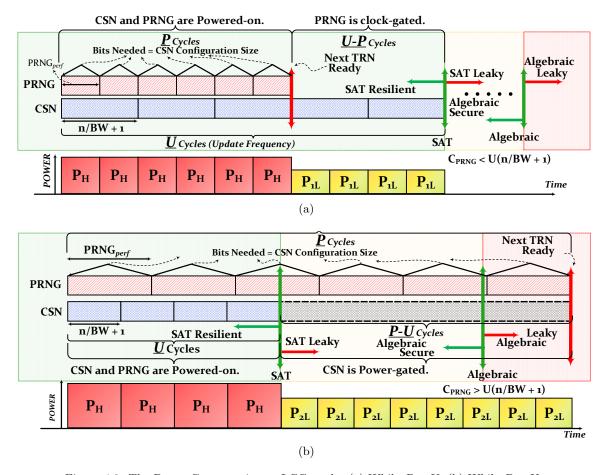

| 4.9    | The Power Consumption at LCC mode: (a) While $P < U$ , (b) While $P > U$ .    | 87   |

## Chapter 1: Introduction to Hardware Obfuscation

The cost of building a new semiconductor fab was estimated to be \$5.0 billion in 2015, with large recurring maintenance costs [1][2], and sharply increases as technology migrates to smaller nodes. To reduce the fabrication cost, most of the manufacturing and fabrication is pushed offshore [1]. However, many of the offshore fabrication facilities are considered to be untrusted. Manufacturing in untrusted foundries has raised concern over potential attacks in the manufacturing supply chain, with an intimate knowledge of the fabrication process, the ability to modify and expand the design prior to production, and an unavoidable access to the fabricated chips during testing. Accordingly, fabrication in untrusted foundries has introduced multiple forms of security threats from supply chain including that of overproduction, Trojan insertion, Reverse Engineering (RE), Intellectual Property (IP) theft, and counterfeiting [2].

To counter these threats, various hardware design-for-trust techniques have been proposed, including watermarking, IC metering, split manufacturing, IC camouflaging, and logic locking [3–7]. The watermarking and IC metering techniques are passive protection models that could be used to detect overproduction or illegal copies, however, they cannot prevent IP theft or overproduction. The Camouflaging techniques use logic gates (or other physical structures such as dummy vias) with high structural similarity, that are indistinguishable from one another to protect against reverse engineering. However, camouflaging is only effective against post-manufacturing attempt(s) of reverse engineering, while it provides no limitations against a foundry's attempt at reverse engineering, as a foundry has access to all masking layers and is not trapped by structural ambiguity for being able to logically extract a netlist. The obfuscation (logic locking) [7] on the other hand, introduce limited programmability by inserting key programmable gates to hide or lock the functionality. By using obfuscation, the target chip produces the correct output only when the key

inputs are correct. The purpose of obfuscation is to protect against RE at an untrusted foundry. By using obfuscation, even by having all mask information, the attacker cannot generate the correct functionality of a circuit without the correct key values, and such key values are not shared with the manufacturer.

logic locking techniques, however did not end the threat against IP piracy (or other related concerns), as these solutions that were proposed over the last decade were broken using various carefully crafted attacks. A decade of research in this area, has resulted in a wide range of defense and attack solutions. Shortly after the introduction of first published obfuscation schemes, a new and powerful attack based on Boolean Satisfiability (SAT) was formulated and revealed [9, 10]. In this attack model, the attacker has access to a reverse engineered but obfuscated netlist, and a functional and unlocked chip. Using this attack model, the formulated Boolean Satisfiability Attack (SAT Attack) can effectively break all previously proposed logic encryption techniques, including random insertion (RLL), faultanalysis (FLL), interference-based logic locking (SLL), and logic barriers [7, 11–17]. The SAT solver iteratively eliminates sets of incorrect keys and finds the correct key within a small time, and unlike Brute force attack that requires attack time exponential with respect to the number of inputs, its execution time grows almost polynomially. Existing SAT attack, which can be modeled with query-by-disagreement (QBD) or uncertaintysampling, minimizes the number of queries (inputs) required to learn (deobfuscate) the target function (obfuscated logic). Also, SAT attack terminates when no more disagreeing inputs can be found, at which time the attack guarantees to find the correct key. However, to defend against powerful SAT attacks, different obfuscation schemes have been proposed, such as SARLock and Anti-SAT [15,18,19]. However, further research illustrated that some of these locking schemes are vulnerable to other types of attacks such as Signal Probability Skew (SPS) and removal attacks [20].

In addition, introducing approximate-based attacks, such as AppSAT [21] or Double-DIP [22] worsens the problem. Unlike the existing SAT attack, which needs exact learning model, approximate-based attacks can be modeled using approximate learning problems,

such as the probably-approximately-correct (PAC) setting [23]. Based on the PAC model, an attack A, with a probability of  $\lambda$ , will provide an  $\epsilon$ -approximation (approximately correct) of the target function (obfuscated logic). Note that, an  $\epsilon$ -approximation of the target function is a function with only  $\%\epsilon$  ( $\epsilon \in O(\frac{1}{2^n})$ ) disagreement with correctly unlocked circuit. Accordingly, the approximate SAT attacks can find an approximate key which produces a very small error ( $\%\epsilon$ ) in the behavior of the unlocked circuit in comparison with a correctly unlocked circuit. The approximate attacks are shown to effectively find an approximate key for SAT-resilient defenses including SARLock [18], and Anti-SAT [19]. Furthermore, Bypass attack [24] is also proposed for creating an auxiliary circuit that recovers the flipped output(s) while approximate key is applied. Then it adds a bypass circuit to correct the wrong output(s) when input pattern(s) cause incorrect output(s). Consequently, it is able to eliminate even small error in the behavior of the unlocked circuit by approximate key, and behave completely the same compared to correctly unlocked chip. In Section 2 we review many of the obfuscation solutions and attack mechanisms in more details, summarize and compare the effectiveness of obfuscation solutions against these attacks, and describe the strength and weaknesses of various obfuscation and attack solutions [25].

In general, the SAT attack benefits from the Directed Acyclic Graph (DAG) based nature of input netlist and the ability of SAT-attack to logically model the obfuscation into a satisfiability problem. To counter the SAT attack, recently some design obfuscation schemes have been proposed to violate these assumptions. For instance, in the approach adopted in [26], the DAG nature of netlist is altered by introducing cycles into the netlist for the purpose of trapping a SAT attack. Another example is the approach adopted in [27], where the obfuscation, in addition to logical properties of the netlist, targets the setup and hold properties (timing properties) of the circuit as a locking mechanism. Considering that setup and hold time are not logical properties, they cannot be translated into CNF statements for formulating a SAT attack. However, in section 3 by proposing the Satisfiability Modulo Theory (SMT)-based attack, we illustrate that even using these non-logical properties for obfuscation, does not increase the security of an obfuscated netlist, indicating the need for

further study and exploration in this domain to generate obfuscation schemes with provable security.

In addition, to remain hidden, apart from being resistant to different attack models on obfuscated circuits, the IC should also resist passive, active, or destructive attacks that could be deployed to read the key values. Hence, neither the activation of such devices nor the storage of key values in them should expose or leak the key information. Activation of an obfuscated IC requires storing the activation key in a secure and tamper-proof memory. [28, 29]. However, there exist a group of applications that could use an alternative key storage. This alternative solution is to store the key outside the IC, where the IC is activated every time it is needed. This option requires constant connectivity to the key management source and a secure communication for key exchange to prevent any leakage of the key. This solution allows an IC designer to store the chip unlock key outside of an untrusted chip. So, no secure and tamper-proof memory is needed. Since the key is stored outside the untrusted chip, a constant connectivity to an obfuscation key-management solution is an indispensable requirement for this category of devices. This requirement could be easily met for two prevalent groups of architectures: (1) 2.5D package-stack devices where a single trusted chip is used for key management and activation of multiple obfuscated ICs manufactured in untrusted foundries, and (2) IoT devices with constant connectivity to the cloud/internet.

In 2.5D package-integrated ICs, similar to DARPA SPADE architecture [30], a chip which is fabricated in a trusted foundry, but in a larger technology node, is packaged with an untrusted chip fabricated in an untrusted foundry in a smaller technology node. The resulting solution benefits from the best features of both technologies: The untrusted chip may be used as an accelerator, providing the resulting hybrid solution with the much-needed scalability (higher speed and lower power), while the trusted chip provides the means of trust and security. The untrusted chip is isolated from the outside world and any exchange of information to/from untrusted chip passes through the trusted chip.

The second group of devices in this category are IoT devices, where constant connectivity

is their characterizing features. In these solutions the obfuscation key could be stored in the cloud, and activation of an IoT device could be done remotely. This model allows custom, monitored, and service oriented activation (Activation As A Service). An additional advantage is removing the possibility of extracting an unlock key from a non-volatile memory that otherwise would have to be used for storing the obfuscation unlock key. Examples of which are IoT devices used for providing various services, military drones activated for a specific mission, video decryption services for paid pay-per-view transactions, etc., where a device has to operate in an unsafe environment and is at risk of capture and reverse engineering. In these applications, the IC fabricated in an untrusted foundry is activated either every time it is powered up, or for certain time intervals. The key vanishes after the service is performed, or when the device is powered down. The activation of such devices is performed using a remote key management service (in the cloud or at a trusted base-station), and the key exchange to/from these devices should be secured.

In both 2.5D system solutions and IoT devices, the need for implementation of a tamperproof memory, for storage of IC activation key, in an untrusted process is removed. Some reasons why implementing a secure memory in an untrusted foundry may be undesired, or practically unfeasible include:

Availability: The targeted foundry may not offer the required process for implementing a secure memory with the desired features. An example could be the requirement for storing sensitive information in magnetic tunnel junction (MTJ) memories to prevent probing and attacks that could be deployed against flash-based NVMs. Fabricating such ICs requires a hybrid process that supports both CMOS and MTJ devices, which may be unsupported by the targeted foundry.

Verified Security: The secure memory may be available in the targeted technology, however not be fully tested and verified in terms of its resistance against different attacks.

Cost: Implementing secure memory requires additional fabrication layers and processing steps, increasing the cost of manufacturing. Increasing the silicon area is a far cheaper solution than increasing the number of fabrication layers.

Reusability: In 2.5D system solutions, a trusted chip could be shared by multiple untrusted chips, manufactured in different foundries. Moving the secure memory to the trusted chip removes the need for implementing the secure memory in all utilized processes. The trusted chip could be designed once with utmost security for protection and integrity of data. This also reduce the cost of manufacturing untrusted chips by removing the need for additional processing steps for implementing secure memory.

Ease of Design: Implementing secure memory requires pushing the design through non-standard physical design flow to implement the tamper-proof layers in silicon and package. In addition, the non-volatile nature of tamper-proof memory requires read and write at elevated voltages, increasing the burden on the power-delivery network design. Reuse of a trusted chip with a tamper proof memory that could manage activation of other obfuscated ICs, relaxes the design requirement of ICs to standard physical design and fabrication process.

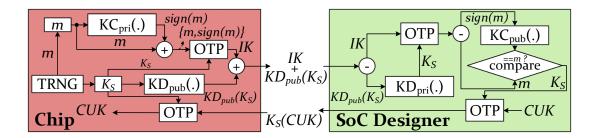

In section 4, we propose the COMA key-management and communication architecture for secure activation of obfuscated circuits that are manufactured in untrusted foundries and meet the constant connectivity requirement, namely ICs that belong to a) 2.5 package-integrated and b) IoT solutions. We describe two variants of our proposed solutions: The first variant of COMA is used for secure activation of IPs within 2.5D package-integrated devices (similar to DARPA SPADE). The second variant of COMA is used for secure activation of connected IoT devices. The proposed COMA allows us to (1) push the obfuscation key and obfuscation unlock mechanism off of an untrusted chip, (2) make the key a moving target by changing it for each unlock attempt, (3) uniquely identify each IC, (4) remove the need to implementing a secure memory in an untrusted foundry, and (5) utilize two novel mechanisms for ultra-secure or ultra-fast encrypted communication [31].

## Chapter 2: Threats on Logic Locking: A Decade Later

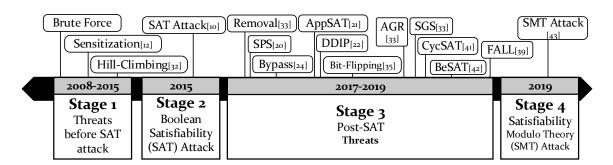

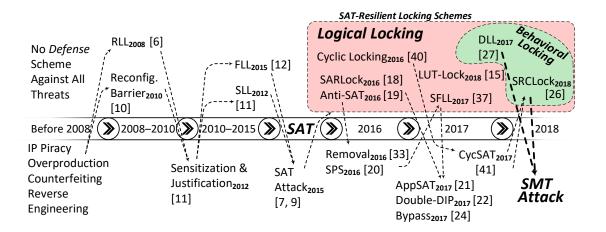

As illustrated in Fig. 2.1, the defense and attack solutions related to hardware obfuscation, based on functionality, capability, effectiveness and time-line are categorized into four categories: (1) Test-Inspired Attacks that were mostly inspired from test concepts and attempted to discover the obfuscation key value based on the location of KGs, described in Section 2.1. (2) SAT Attack, formulation and revelation of which significantly affected the direction and presumed assumptions of the hardware obfuscation research community, explained in Section 2.2. (3) Post-SAT Attacks where the focus of hardware security researchers changed to the design of an attack against obfuscation solutions that resist the SAT attack, explained in 2.3. And (4) SMT Attack as a universal attack platform capable of instantiating many theory solvers to act as pre- post- or co- processors to the SAT solver, described in Section 2.4.

Figure 2.1: Categorization of attacks against logic locking schemes.

## 2.1 Stage 1: Test-Based Attacks

#### 2.1.1 Brute Force Attack

The brute force attack is the most intuitive attack against obfuscated circuits. This attack exhaustively search for the correct key by testing all key and input values. For instance, assuming that adversary has access to the reverse-engineered netlist, and considering that the circuit has four PIs ( $i_{0..4}$ ) and two KIs ( $k_{0..1}$ ), an exhaustive search may result in applying of  $2^{2+4} = 64$  test patterns (in the worst case) and checking the output against an activated (functionally correct) chip to verify correctness. Based on the number of primary inputs (|PI|) and the number of key bits (|KI|), the number of possible test patterns is  $(2^{|PI|+|KI|})$ . Hence, the search space for a brute force attack is extremely large, making the attack even for small circuits and small number of keys unfeasible in a reasonable amount of time. For example, a small circuit with 20 input pins, which is obfuscated with 80 key gates poses  $2^{100}$  possible test pattern. An attacker can reduce the number of test patterns using functional test or random test, in which the exponential impact of |PI|s will be eliminated, and only  $2^{|KI|} \times (func\_test\_patterns)$  is required for brute force attack. But even with this change, the attack time is exponential with respect to the number of key gates. EPIC [7] used a random KG insertion policy referred to as random logic locking (RLL). Using RLL, EPIC reasoned that by replacing a small percentage of gates (or insertion of KGs), the obfuscation can resist brute force attacks.

#### 2.1.2 Sensitization Attack

After introducing EPIC [7], Rajendran et al. [12] proposed a sensitization attack, which determines individual key values, in a time linear to the |KI|, by applying patterns that sensitize key values to the output. As its name implies, sensitization of an internal wire (key bit)  $\mathbf{L}$  to an output  $\mathbf{O}$  means that the value of  $\mathbf{L}$  can be propagated to  $\mathbf{O}$  and thus any change on  $\mathbf{L}$  is observable on  $\mathbf{O}$ . After determining an input pattern that propagates the value of the key-bit to the output, the attacker applies the input pattern to a functional

Table 2.1: Classification of KGs in Sensitization Attack.

| Term                 | Description                     | Strategy used by attacker       |  |  |  |

|----------------------|---------------------------------|---------------------------------|--|--|--|

| Runs of KGs          | Back-to-Back KGs                | Replacing by a Single KG        |  |  |  |

| Isolated KGs         | No Path between KGs             | Finding Unique Pattern per      |  |  |  |

| Isolated KGs         | No Fath between KGs             | KG (Golden Pattern (GP))        |  |  |  |

| Dominating KGs       | k1 is on Every Path             | Muting $k0$ ,                   |  |  |  |

| Dominating KGs       | between $k0$ and $PO$ s         | Sensitizing $k1$                |  |  |  |

| Concurrently Mutable | Convergent at a Third Gate      | Muting $k0/k1$ ,                |  |  |  |

| Convergent KGs       | Both can be Propagated to $POs$ | POs Sensitizing $k1/k0$         |  |  |  |

| Sequentially Mutable | Convergent at a Third Gate      | Determining $k1$ by GP,         |  |  |  |

| Convergent KGs       | One can be Propagated to $PO$ s | Update the Netlist, Target $k0$ |  |  |  |

| Non-Mutable          | Convergent at a Third Gate      | Brute Force Attack              |  |  |  |

| Convergent KGs       | None can be Propagated to $POs$ | S Trute Porce Attack            |  |  |  |

IC (An IC activated and programmed with the correct key that could be obtained from market). The correct key value will be propagated to an output by applying this pattern to the functional IC. The attacker observe and record this output as the value of the sensitized key-bit. The propagation of a key-bit to the output is heavily depending on the location of the KGs, hence, they classify KGs based on their location and discuss corresponding attack strategies for each case. The summary of strategies and techniques used in the sensitization attack is reflected in Table 2.1. To prevent sensitization attack they proposed SLL, in which the KGs are inserted in locations with maximum mutual interference. In SLL the attacker cannot sensitize the key-bit values to a primary output. Similar to SLL, several prior-art methods in the literature, including fault-analysis (FLL), LUT-based locking, etc. [11–15], tried to maximize the complexity of obfuscation using different KGs replacement strategies.

#### 2.1.3 Random-based Hill-Climbing Attack

Plaza et al. [32] developed a new algorithmic attack that uses test patterns and observe responses. Unlike sensitization attack [12], their proposed approach does not require netlist access. They propose a randomized local key-searching algorithm to search the key that can satisfy a subset of correct input/output patterns. The algorithm proposed in [32] is iterative in nature. At first, it selects random value for key bits and then at each iteration, the key bits, which are selected randomly, are toggled one by one. The target is to minimize the

frequency of differences between the observed and expected responses. Hence, a random key candidate is gradually improved based on observed test responses. If no solution is found in one iteration, the algorithm resets the key to a new random key value. However, the complexity of this attack quickly increases with increasing number of KGs.

## 2.2 Stage 2: SAT Attack

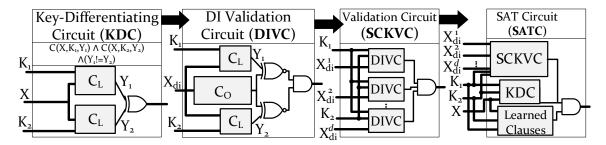

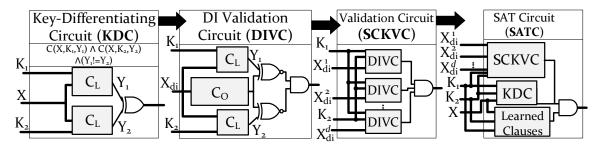

In 2015, Subramanyan et al. [10] proposed a new and powerful attack using Boolean satisfiability (SAT) solver, called SAT attack, that effectively and quickly broke all previously proposed logic locking techniques. As an "oracle-guided" attack, SAT attack requires a reverse-engineered but locked netlist  $(C_L)$ , and a functionally activated chip  $(C_O)$ . A circuit view of steps taken in a SAT attack is shown in Fig. 2.2. For this attack, the attacker first replicate the obfuscated circuit and builds a double circuit which is used for finding an input  $(X_d|i|)$  that for two different key values generates two different outputs. Such input is referred to as Discriminating Input Pattern(DIP). Each  $X_d[i]$  is used to create a DI validation circuit (DIVC). The validation circuit, as shown in Fig. 2.2 assures that for a previously found  $X_d[i]$ , two different keys generate the same output value. Each iteration of the SAT attack finds a new  $(X_d[i])$ , and add a new DI validation circuit. The DIVCs are ANDed together to form a Set of Correct Key Validation Circuit (SCKVC). In each iteration, the SAT solver try to find a new  $X_d[i]$  and two key values that satisfy the double circuit (KDC) and the Validation Circuit (SCKVC). The key values and the  $X_d[i]$ , as illustrated in Alg. 1, is found by a SAT query. This means the new key generate two different values for the new  $X_d[i]$ , but generate the same value for all previously found  $X_d$ s for both key values. This process continues until the SAT solver cannot find a new  $X_d[i]$ . At this point any key that generates the correct output for the set of found  $X_d$ s is the correct key.

For all prior obfuscation schemes, even those resistant to sensitization attack, the SAT attack was able to rule out a significant number of key values at each iterations (by finding each DIP). Hence, In order to thwart SAT attack, the first attempted approach was to weaken the strength of the DIPs to reduce its pruning power. SARLock [18] and Anti-SAT

Figure 2.2: SAT Attack Iterative Flow.

#### Algorithm 1 SAT-based Attack Algorithm [10]

```

1: function SAT_ATTACK(Circuit C_L, Circuit C_O)

2: i \leftarrow 0; F_0 \leftarrow C_L(X, K_1, Y_1) \wedge C_L(X, K_2, Y_2);

3: while SAT(F_i \wedge (Y_1 \neq Y_2)) do

4: X_d[i] \leftarrow \text{sat\_assignment} (F_i \wedge (Y_1 \neq Y_2)); Y_d[i] \leftarrow C_O(X_d[i]);

5: F_{i+1} \leftarrow F_i \wedge C_L(X_d[i], K_1, Y_d[i]) \wedge C_L(X_d[i], K_2, Y_d[i]); i \leftarrow i+1;

6: K^* \leftarrow \text{sat\_assignment}_{K_1}(F_i);

```

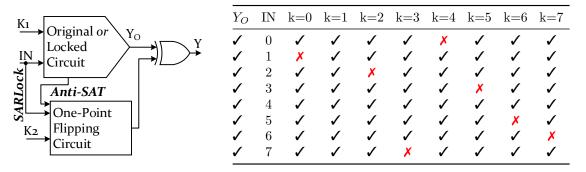

[19] were the first prior-art methods that accomplished this. Both SARLock and Anti-SAT engaged one-point flipping function, demonstrated in Fig. 2.3. Using this obfuscation scheme, each DIP is able to rule out only one incorrect key. Hence, the SAT attack requires to apply all  $2^{|KI|}$  to retrieve the correct functionality. However, this method results in obfuscation circuits that for all but one output work as the original circuit, and the output corruption upon application of a wrong key is quite low.

## 2.3 Stage 3: Post-SAT Attacks

As discussed, the proposed SAT-resilient solutions suffered from low output corruption. This however could have been addressed by combining a SAT-hard solution with a traditional obfuscation solution, such as RLL or SLL, that exhibits high level of output corruption. Although SAT-resilient logic locking schemes provided a defense against SAT attack, researchers found new vulnerabilities associated with this class of obfuscation techniques resulting in the development of many new attacks on the presumed SAT-hard logic locking schemes described in this section.

Figure 2.3: Flipping Structure of SARLock and Anti-SAT.

#### 2.3.1 Removal Attack

As shown in Fig 2.3, in bare implementation of one-point flipping circuit, the locking circuitry is completely decoupled from the original circuit. A removal attack identifies and removes/bypasses the locking circuitry to retrieve the original circuit and to remove dependence on key values [33]. The removal attack, presented in [33], was used to detect and remove SARLock [18]. In presence of removal attack, researchers investigated SAT-hard solutions that are hard to detect (preventing removal by pure structural analysis), an example of which was Anti-SAT [19].

#### 2.3.2 Signal Probability Skew (SPS) Attack

The Signal Probability Skew (SPS) attack [20] leverages the structural traces in Anti-SAT block to identify and isolate the Anti-SAT block [19]. Signal probability skew (SPS) of a signal x is defined as  $s = P_r[x = 1] - 0.5$ , where  $P_r[x = 1]$  indicates the probability that signal x is 1. The range of s is [-0.5, 0.5]. If the SPS of signal x is closer to zero, an attacker have lower chance of guessing the signal value by random. For a 2-input gate, the signal probability skew is the difference between the signal probability of its input wires. The flipping-circuit in the Anti-SAT is constructed using two complementary circuits, g and g, in which the number of input vectors that make the function g equal to 1 g is either close to 1 or g and g are g in the absolute difference of the signal probability skew (ADS) of the inputs of gate g is quite large, noting that the SAT resilience is ensured by this skewed g. Algorithm

2 shows the SPS attack, which identifies the Anti-SAT block's output by computing signal probabilities and searching for the skew(s) of arriving signals to a gate in a given netlist.

#### Algorithm 2 SPS Attack Algorithm [20]

```

1: function SPS_ATTACK(Circuit C_L)

ADS_{arr} \leftarrow \{\};

2:

for each gate \in C_L do

3:

4:

ADS_{arr}(\text{gate}_i) \leftarrow \text{Compute\_ADS}(C_L, \text{gate}_i);

G \leftarrow \text{Find\_Maximum}(ADS_{arr});

5:

Y \leftarrow \text{Find\_value\_from\_skew}(G);

▷ Correct value of Anti_SAT output

6:

C_{Lock} \leftarrow remove\_\mathbf{TFI}(C_L, G, Y);

7:

\triangleright Transitive FanIn of the gate G

\triangleright C<sub>Lock</sub>: C<sub>L</sub> after removing Anti_SAT block

8:

return C_{Lock}

```

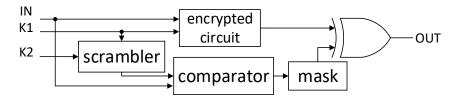

#### 2.3.3 Bypass Attack

Although SARLock and Anti-SAT break the SAT attack, their respective output corruptibility is very low if they are not mixed with traditional logic locking, such as SLL. Observing and relying on the very low level of output corruption in such SAT-hard solutions, the bypass attack [24] was introduced. The bypass attack instantiates two copies of the obfuscated netlist using two randomly selected keys, and build a miter circuit that evaluates to 1 only when the output of two circuits is different. The miter circuit is then fed to a SAT solver looking for such inputs. The SAT returns with minimum of two inputs for which the outputs are different. These input patterns are tested using an activated IC (golden IC) validating the correct output. Then a bypass circuit is constructed using a comparator that is stitched to the primary output of the netlist which is unlocked using the selected random key, to retrieve the correct functionality if that input pattern is applied. The Bypass attack works well when the SAT-hard solution is not mixed with traditional logic locking mechanism since its overhead increases very quickly as output corruption of logic locking increases. This observation motivated researchers to look at possibilities of approximate attacks to retrieve the key values associated to non SAT-hard obfuscation solutions that are mixed with SAT-hard solutions.

#### 2.3.4 AppSAT Attack

So far, defences solution to mitigate the SAT attack, are based on the assumption that the attacker needs an exact attack on logic locking. However, Shamsi et al. [21] proposed a new attack (AppSAT), which relax this constraint. AppSAT shown in Algorithm 3, is an approximate attack on logic locking based on the SAT attack and random testing. The authors use probably-approximate-correct (PAC) model for formulating approximate learning problem. The exact SAT attack continues to find DIPs until no more DIPs can be found. However, the AppSAT will be terminated in any early step in which the error falls below the certain limit. If this condition happens, the key value will be considered as an approximate key with specified error rate; otherwise, the random sampling that resulted in a disagreement will be added to a SAT formula as a new constraint. In AppSAT, heuristic methods for estimating the error is used for large functions, to avoid any computation complexity.

#### 2.3.5 Double-DIP Attack

Double-DIP [22] is another approximate attack, shown in Algorithm 4. Double-DIP is an extension of SAT attack in which during each iteration, the discriminating input should eliminate at least two wrong keys. To illustrate its effectiveness, researchers used double-DIP to target SARLock+SSL, representing a compound of SAT-hard and high output corruption obfuscation. When the double-DIP attack terminates, the key of the traditional logic locking (SSL) is guaranteed to be correct. As a result, the compound logic locking will be reduced to a single SAT attack resilient technique, that could then be attacked using bypass attack.

#### 2.3.6 Bit-Flipping Attack

The Bit-flipping attack [35] is yet another attack against compound logic locking schemes in which a SAT-hard solution such as SARLock is combined with a traditional logic locking to guarantee both high error rates and resilience to the SAT-based attack. In Bit-flipping

#### **Algorithm 3** AppSAT Attack Algorithm [21]

```

1: function APPSAT_ATTACK(Circuit C_L, Circuit C_O)

i \leftarrow 0; F_0 \leftarrow C_L(X, K_1, Y_1) \wedge C_L(X, K_2, Y_2);

2:

3:

while SAT(F_i \wedge (Y_1 \neq Y_2)) do

X_d[i] \leftarrow \text{sat\_assignment } (F_i \land (Y_1 \neq Y_2)); Y_d[i] \leftarrow C_O(X_d[i]);

4:

F_{i+1} \leftarrow F_i \wedge C_L(X_d[i], K_1, Y_d[i]) \wedge C_L(X_d[i], K_2, Y_d[i]); i \leftarrow i+1;

5:

every n rounds do

6:

for each (x \in \text{Random Patterns}) do

7:

if C_L(X, K_1, Y) \neq C_O(X) then

8:

FailedPatterns \leftarrow FailedPatterns + 1;

9:

F_{i+1} \leftarrow F_{i+1} \wedge (C_L(X, K_1, Y) = C_O(X)); i \leftarrow i+1;

10:

if error; ErrorThreshold then

11:

return K_1 as an approximate key

12:

K^* \leftarrow \operatorname{sat}_{\operatorname{assignment}}_{K_1}(F_i);

13:

```

#### Algorithm 4 Double-DIP Attack Algorithm [22]

```

1: function DOUBLEDIP_ATTACK(Circuit C_L, Circuit C_O)

2: i \leftarrow 0; F_0 \leftarrow C_L(X, K_1, Y_1) \wedge C_L(X, K_2, Y_2) \wedge C_L(X, K_3, Y_1) \wedge C_L(X, K_4, Y_2);

3: while SAT(F_i \wedge (Y_1 \neq Y_2)) \wedge (K_1 \neq K_3)) \wedge (K_2 \neq K_4)) do

4: X_d[i] \leftarrow \text{sat\_assignment} (F_i \wedge (Y_1 \neq Y_2)) \wedge (K_1 \neq K_3)) \wedge (K_2 \neq K_4));

5: Y_d[i] \leftarrow C_O(X_d[i]);

6: F_{i+1} \leftarrow F_i \bigwedge_{j=1}^4 C_L(X_d[i], K_j, Y_d[i]); i \leftarrow i+1;

7: K^* \leftarrow \text{sat\_assignment}_{K_1}(F_i);

```

attack, the keys are first separated into two groups ( $k_1$  and  $k_2$ ) by counting DIPs for two keys with hamming distance equal to one. The attack is motivated from the observation that in traditional logic locking, wrong key causes substantial wrong input-output pattern. However, the error rate of bit-flipping function is usually very small. As shown in Algorithm 5, after separation of keys, this attack fixes SAT-resilient keys,  $k_2$ , as a random number, and uses a SAT solver to find the correct key values for  $k_1$ . After finding  $k_1$ , the bypass attack is applied to retrieve the original circuit.

#### 2.3.7 AppSAT Guided Removal Attack

AppSAT Guided Removal (AGR) attack targets compound logic locking, particularly Anti-SAT + traditional logic locking [33]. This attack integrates AppSAT with a simple structural analysis of the locked netlist (a post-processing steps). Unlike AppSAT, the AGR attack recovers the correct key. In this attack, first the AppSAT is used to find the key of the

#### **Algorithm 5** Bit-flipping Attack Algorithm [35]

```

1: function BitFlipping_Attack(Circuit C_L, Circuit C_O)

for each j; Fixed-iteration do

2:

3:

K_A \leftarrow a \text{ random key};

for each bit b \in K_A do

4:

K_B \leftarrow K_A while bit b flipped;

5:

i \leftarrow 0; F_0 \leftarrow C_L(X, K_A, Y_A) \wedge C_L(X, K_B, Y_B);

6:

while SAT(F_i \wedge (Y_A \neq Y_B)) do

7:

X_d[i] \leftarrow \text{sat\_assignment } (F_i \land (Y_A \neq Y_B));

8:

F_{i+1} \leftarrow F_i \wedge (X \neq X_d[i]); i \leftarrow i+1;

9:

if i ; Threshold then

10:

11:

b is in K_1,

break:

12:

j \leftarrow j + 1;

K_2 \leftarrow \text{all key bits } / K_1;

\triangleright Separation is Done. Then, fix K_2 as a random number.

13:

K_1 \leftarrow SAT\_ATTACK (C_L, C_O);

▶ Find Traditional Keys using SAT.

14:

15:

C_L^* \leftarrow \text{update\_netlist}(C_L - K_1)

16:

return (BYPASS_ATTACK(C_L^*);

```

traditional obfuscation scheme (used as a part of compound lock). Then, AGR targets the remaining key bits belong to the SAT-resilient logic locking, such as Anti-SAT block, through a simple structural analysis. As shown in Algorithm 6, in the post-processing steps, AGR finds the gate (G) at which most of the Anti-SAT key bits converge. AGR finds G by tracing the transitive fanout of the Anti-SAT key inputs, where all the Anti-SAT key bits converge. The ratio of key bits converging at each of the inputs of the gate G, are close to 0.5, which is shown as the selected property in line 7 of Algorithm 6. AGR identifies the candidates for gate G by checking this property for all gates in the circuit, and then sort these candidate based on the number of key inputs that converge at a gate and pick the gate G from all candidates, which has the most number of key inputs converge to that gate. Then the attacker re-synthesize the design with the constant value for the output of G gate and retrieving the correct functionality.

#### 2.3.8 Sensitization Guided SAT Attack

While the one-point flipping circuit in Anti-SAT and SARLock are completely decoupled from the original netlist, Li *et al.* [36] proposed the AND-tree Insertion (ATI), as a SAT-resilient logic locking, which embeds AND trees inside the original netlist. It not only

#### Algorithm 6 AGR Attack Algorithm [33]

```

1: function AGR_ATTACK(Circuit C_L, Circuit C_O)

\#Cand \leftarrow \text{num\_gates}(C_L)

2:

while (\#Cand : 1 \text{ and } !Timeout) \text{ do}

3:

AppSAT_Attack();

\triangleright 4 times

4:

Candidates \leftarrow \{\};

5:

for each gate \in C_L do

6:

7:

if gate_i has the selected property then

Candidates \leftarrow Candidates + 1;

8:

9:

G \leftarrow \text{Find\_Max\_kev\_count}(Candidates);

C_{Lock} \leftarrow remove\_\mathbf{TFI}(C_L, G);

\triangleright remove Transitive FanIn of the gate G

10:

11:

return C_{Lock};

\triangleright C_{Lock}: C_L after removing Anti-SAT block

```

makes all aforementioned attack less effective, it also decreases the implementation overhead. Additionally, the input of AND-tree are camouflaged by inserting INV/BUF camouflaged gates, which can be replaced with the XOR/XNOR gates in order to lock the AND-tree. However, this defense was broken by a new attack that was coined as Sensitization Guided SAT (SGS) attack [33]. The SGS attack is carried out in two stages: (1) sensitization that exploits bias in input patterns which allows an attacker to apply only a subset of DIPs, i.e., those that bring unique values to the AND-tree inputs. (2) SAT attack using the patterns discovered in the first stage.

#### 2.3.9 Functional Analysis Attack

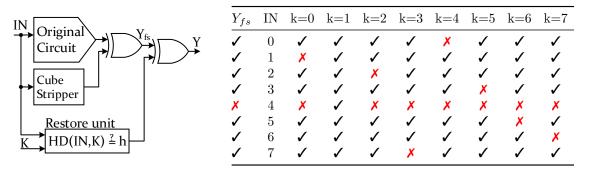

Aiming to provide a defense that resists all previously formulated attacks led to the introduction of Stripped-Functionality Logic Locking (SFLL) [37]. In SFLL the original circuit is modified for at-least one input pattern (cube) using a cube stripping unit, demonstrated in Fig. 2.4. As shown,  $Y_{fs}$  is the output of the stripped circuit, in which the output corresponding to at-least one input pattern is flipped. The restore unit not only generates the flip signal for one input pattern per each wrong key, it also restores the stripped output, (e.g. IN = 4 in Fig. 2.4) to recover the correct functionality on Y. Note that applying removal attack on restore unit recovers  $Y_{fs}$ , which is not the correct functionality. In addition, SFLL-HD is able to protect  $\binom{k}{h}$  input patterns that are of Hamming Distance (HD) hfrom the k-bit secret key, and accordingly uses Hamming Distance checker as a restore unit (e.g. h = 0 in Fig. 2.4 is also called TTLock [38]).

Although SFLL was resilient against all previously formulated attacks, it was exploited using a newly formulated attack, called Functional Analysis on Logic Locking (FALL) attack [39]. In this attack model, the adversary is assumed to be a malicious foundry that knows the locking algorithm and its parameters, e.g. h in SFLL-HD. A FALL attack is carried out in three main stages and relies on structural and functional analyses to determine potential key values of a locked circuit. First, FALL attack tries to find all nodes which are the results of comparing an input value with a key input. It is done by a comparator identification. Such nodes  $(nodes_{RU})$ , which contains these particular comparators, are very likely to be part of the functionality restoration unit. The set of all inputs that appear in these comparators, should be in the fan-in cone of the cube stripping unit. Then, it finds a set of all gates whose fan-in-cone is identical to the members of  $nodes_{RU}$ . This set of gates must contain the output of the cube stripping unit. Second, the attacker applies functional analysis on the candidate nodes suggested by and collected from the first stage to identify suspected key values. Broadly speaking, the attacker uses functional properties of the cube stripping function used in SFLL, to determine the values of the keys. Based on the author's view, this function has three specific properties. So, they have proposed three attacks algorithms on SFLL, which exploit unateness and Hamming distance properties of the cube stripping functions. The input of these algorithm is circuit node c, that computed from the first stage, and the algorithm checks if c behaves as a Hamming distance calculator in the cube stripping unit of SFLL-HD. If the attack is successful, the return value is the protected cube. Third, they have proposed a SAT-based key confirmation algorithm using a list of suspected key values and I/O oracle access, that verifies whether one of the suspected key values computed from the second stage, is correct.

#### 2.3.10 CycSAT Attack

Considering the strength of all previously formulated attacks, some of the researchers started seeking solutions that fundamentally violated the assumptions of these attacks with respect

Figure 2.4: SFLL-HD while h = 0.

to the nature of locked circuits. One of such attempts was the introduction of cyclic logic locking [40][26], was first proposed in [40]. In this obfuscation technique each deliberately established cycle is designed to have more than one way to open. The requirement for having more than one way to open each cycle assures that even if the original netlist has no cycle by itself, the cycles remains irreducible by means of structural analysis. The cyclic obfuscation resulted in an obfuscation with high level of output corruption, while it was able to break the SAT attack either by 1) trapping it in an infinite loop, or 2) forcing it to exit with a wrong key depending on weather the introduced cycles make the circuit stateful or oscillating.

The promise of secure cyclic obfuscation was shortly after broken by CycSAT attack [41]. In CycSAT, the key combinations that result in formation of cycles are found in a pre-processing step. These conditions are then translated into problem augmenting CNF formulas, denoted as cycle avoidance clauses, satisfaction of which guarantee no cycle in the netlist. The cycle avoidance clauses are then added to the original SAT circuit CNF and the SAT attack is executed. The validity of this attack, however, was challenged in [26], as researchers illustrated that the pre-processing time for CycSAT attack is linearly dependent on the number of cycles in the netlist. Hence, by building an exponential relation between the number of feedback, and the number of cycles in the design, the pre-processing step of CycSAT will face exponential runtime.

#### 2.3.11 Behavioral SAT (BeSAT) Attack

Inability to analyze all cycles in the prepossessing step of CycSAT results in missing cycles in the pre-processing step of CycSAT, leading to building a statefull or oscillating circuit, trapping the SAT stage of the CycSAT attack. BeSAT [42] remedies this shortcoming by augmenting the CycSAT attack with a run-time behavioral analysis. As shown in Algorithm 7, by performing behavioral analysis at each SAT iteration, BeSAT detects repeated DIPs when the SAT is trapped in an infinite loop. Also, when SAT cannot find any new DIP, a ternary-based SAT is used to verify the returned key as a correct one, preventing the SAT from exiting with an invalid key.

#### Algorithm 7 BeSAT Attack on Cyclic Locked Circuits [42]

```

1: function BESAT_ATTACK(Circuit C_L, Circuit C_O)

W = (w_0, w_1, ... w_m) \leftarrow \text{FindFeedback}(C_L);

3:

for each (w_i \in W) do

F(w_i, w_i') \leftarrow \text{no\_structural\_path}(w_i);

4:

i \leftarrow 0; NC(\mathbf{K}) = \bigwedge_{i=0}^{m} F(w_i, w_i')

5:

\mathbf{C}^*_L(\mathbf{X},\,\mathbf{K},\,\mathbf{Y}) \leftarrow \mathbf{C}_L(\mathbf{X},\,\mathbf{K},\,\mathbf{Y}) \,\wedge\, NC(\mathbf{K});\, F_0 \leftarrow \mathbf{C}^*_L(\mathbf{X},\,\mathbf{K}_1,\,\mathbf{Y}_1) \,\wedge\, \mathbf{C}^*_L(\mathbf{X},\,\mathbf{K}_2,\,\mathbf{Y}_2);

6:

while SAT(F_i \wedge (Y_1 \neq Y_2)) do

7:

8:

X_d[i] \leftarrow \text{sat\_assignment } (F_i \land (Y_1 \neq Y_2)); Y_d[i] \leftarrow C_O(X_d[i]);

9:

F_{i+1} \leftarrow F_i \wedge C_L(X_d[i], K_1, Y_d[i]) \wedge C_L(X_d[i], K_2, Y_d[i]);

if (X_d[i] \text{ in DIP}) and (C_L(X_d[i], K_1) \neq Y_d[i])) then

10:

F_{i+1} \leftarrow F_{i+1} \wedge (K_1 \neq K_1) \wedge (K_2 \neq K_1);

11:

else if (X_d[i] \text{ in DIP}) and (C_L(X_d[i], K_2) \neq Y_d[i]) then

12:

13:

F_{i+1} \leftarrow F_{i+1} \wedge (K_1 \neq K_2) \wedge (K_2 \neq K_2);

i \leftarrow i+1;

14:

while SAT_{K_1}(\mathbf{F}_i) do

\triangleright Correct Key: \hat{K}_c

15:

if Ternary_SAT(F_i, K_c) then

16:

F_i \leftarrow F_i \wedge (K_1 \neq \hat{K}_c)

17:

18:

else

K^* \leftarrow \hat{\mathbf{K}}_c; break;

19:

```

## 2.4 Stage 4: SMT Attack

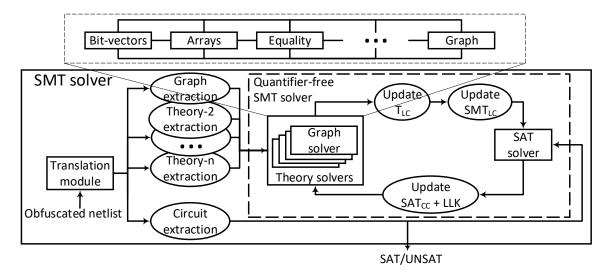

As discussed previously, many of the attacks proposed at post-SAT attack stage were formulated by adding a pre-processing step to the original SAT attack, and/or extending the SAT attack to co-process and check additional features in each iteration. In other terms, to

break many of the post-SAT era obfuscation techniques, attackers relied on compound attacks by combining SAT solvers by pre-processors (e.g. in CycSAT) and co-processors (e.g. in BeSAT) to extend its modeling reach. Motivated by this trend, the need for having pre-co- and post- processors along with a SAT solver in an attack was realized and addressed in [43] and a new and extremely powerful attack, coined as Satisfiability Module Theory (SMT) attack was introduced. The strength of SMT attack, as the superset of SAT attack, comes from its ability to combine SAT and Theory solvers. The SMT attack could be invoked with any number and combination of theory solvers, and a SAT solver, which allow the attacker to express constraints that are difficult or even impossible to express using CNF, including timing, delay, power, arithmetic, graph and many other first-order theories in general. To showcase the modeling capability of SMT attack, the authors used the SMT attack 1) to break a new breed of obfuscation that relied on locking the delay information in netlist (by generating setup and hold violations), 2) to formulate an accelerated attack (to reduce the attack time) with means of approximate exit (if trapped with SAT hard solutions).

#### Algorithm 8 SMT Attack on DLL (Lazy Approach) [43]

```

1: function SMTLAZY_ATTACK(Circuit C_L, Circuit C_O)

C_L^* \leftarrow \text{toBOOLEAN}(C_L);

▷ Replace TDK with Buffer

i \leftarrow 0; F \leftarrow C_L^*(X, K_1, Y_1) \wedge C_L^*(X, K_2, Y_2);

3:

G_L^* \leftarrow \text{toGRAPH}(C_L);

\triangleright Wires = Edges, Gates = Vertices

4:

F_T \leftarrow \operatorname{GenTCE}(G_L^*)

5:

▶ Theory Learned Clauses

F_{SMT} \leftarrow F \wedge F_T;

\triangleright SMT Clauses

6:

7:

while SMT(F_{SMT}) do

\triangleright X_d[i], K_1, K_2, CC

Y_d[i] \leftarrow C_O(X_d[i]); F \leftarrow F \wedge C_L^*(X_d[i], K_1, Y_d[i]) \wedge C_L^*(X_d[i], K_2, Y_d[i]);

8:

F_{SMT} \leftarrow F \wedge CC; i \leftarrow i+1;

9:

K^* \leftarrow \operatorname{smt}_{-\operatorname{assignment}}_{K_1}(F_{SMT});

10:

function GenTCE(Graph G_L^*)

1:

Inputs \leftarrow \text{find\_start\_points}(G_L^*); \ Outputs \leftarrow \text{find\_end\_points}(G_L^*); \ T_{CE}(K) \leftarrow [];

2:

3:

for each ((Sp, Ep) \in (Inputs, outputs) do

Upper(Sp,Ep)(K) \leftarrow !(distance\_leq(Sp, Ep, t_{cd}));

▶ Hold Violation

4:

Lower(Sp,Ep)(K) \leftarrow distance\_leq(Sp, Ep, t_p);

⊳ Setup Violation

5:

Range(Sp, Ep)(K) \leftarrow Lower(Sp, Ep)(K) \wedge Upper(Sp, Ep)(K);

6:

T_{CE}(K) \leftarrow T_{CE}(K) \cup Range(Sp, Ep)(K);

7:

return T_{CE}(K)

8:

```

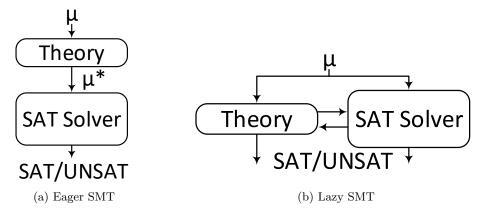

In pursuit of obfuscation schemes that could not be attacked by SAT motivated attackers, some researchers tried to extend the locking mechanism to aspects of a circuit's function that cannot be translated to CNF. For example, Xie et al. proposed a timing obfuscation scheme, denoted as delay logic locking (DLL), in [27]. The Goal of DLL obfuscation scheme is introducing setup and hold violation if the correct key is not applied. In this case, the obfuscation attempts to change both logical and behavioral (timing) properties. A functionally-correct but timing-incorrect key will result in timing violations, leading to circuit malfunctions. Considering that timing is not translatable to CNF, the SAT solver remains oblivious to the kevs used for timing obfuscation. Authors in [43], however, illustrated that the SMT attack could easily deploy a graph theory solver, provide timing constraints to the theory solver (in terms of required min and max delay to meet the hold and setup time), and use the theory solver in parallel with the internal SAT solver to break both logic and delay obfuscation. They additionally show that the theory solver could be initiated as a pre-processor (Eager SMT approach) or as a co-processor (Lazy SMT approach) to break the same problem, showcasing the strength of SMT attack. The *lazy* mode of this attack is illustrated in Algorithm 8. Although at about the same time Chakraborty proposed TimingSAT to attack the DLL [44], similar to many prior SAT-based attack, it was by deploying a pre-processor for analysis of graph timing, and generating helper clauses for the subsequent call to the SAT attack.

The ability of SMT solver to instantiate and integrate different theory solver makes it a suitable attack platform for modeling and formulating very strong attacks. As an example of the strength of SMT attack, the authors in [43] formulated and presented an accelerated SMT attack with ability of detecting the presence of SAT-hard obfuscation and switching to an accelerated approximate attack. As shown in Algorithm 9, this was done by invoking a *BitVector* theory solver to constrain the SMT solver for finding keys that result in highest output corruption first. This could be done by constraining the required HD between the output of double circuit when two different keys for the same discriminating input is being tested. The required HD starts from a large value, and every time that the

SMT solver return UNSAT, the constraint is relaxed until HD of 1 is reached. This leads to the guaranteed discovery of keys for traditional logic locking first. After N tries (Rep in Algorithm 9) for HD of 1, the SMT attack exits, notes that there exist a SAT-hard obfuscation, which now could be addressed by the Bypass attack. More details on SMT attack will be discussed in section 3.

#### Algorithm 9 Accelerated SMT Attack on Compound Locking [43]

```

1: function AccSMT_Attack(Circuit C_L, Circuit C_O)

i \leftarrow 0; HD_h \leftarrow sizeof(\text{output}); HD_l \leftarrow HD_h - 1;

TimeOut \leftarrow 20; Rep \leftarrow 20; HD_R \leftarrow 1; R_{cnt} \leftarrow 0;

3:

C_L^* \leftarrow \text{toBOOLEAN}(C_L);

▷ Everything is Boolean.

4:

F \leftarrow C_L^*(X, K_1, Y_1) \wedge C_L^*(X, K_2, Y_2);

BV_L^* \leftarrow toBITVECTOR(C_L);

▶ Define BITVECTOR on output.

6:

\mathrm{BVs}^*_L(\mathbf{X},\,\mathbf{K}_1,\,\mathbf{K}_2) \leftarrow \mathrm{ONEs}(\mathrm{BV}^*_L(\mathbf{X},\,\mathbf{K}_1) \oplus \mathrm{BV}^*_L(\mathbf{X},\,\mathbf{K}_2));

7:

F_T \leftarrow (\mathrm{BVs}_L^*(\mathrm{X}, \mathrm{K}_1, \mathrm{K}_2) \geqslant HD_l) \wedge (\mathrm{BVs}_L^*(\mathrm{X}, \mathrm{K}_1, \mathrm{K}_2) \leqslant HD_h);

8:

F_{SMT} \leftarrow F \wedge F_T;

▷ SMT Clauses

9:

while HD_l \geqslant 1 do

10:

\triangleright X_d[i], K_1, K_2, CC

while SMT(F_{SMT} - TimeOut) do

11:

12:

Y_d[i] \leftarrow C_O(X_d[i]);

13:

F \leftarrow F \wedge C_L^*(X_d[i], K_1, Y_d[i]) \wedge C_L^*(X_d[i], K_2, Y_d[i]); F_{SMT} \leftarrow F \wedge CC;

if HD_l \leqslant HD_R then

14:

if R_{cnt} == Rep then

15:

break:

16:

17:

R_{cnt}++;

HD_{l}--:

K^* \leftarrow \operatorname{smt\_assignment}_{K_1}(F_{SMT});

18:

```

## 2.5 Discussion & Opportunities

Table 2.2 compares the effectiveness of the attacks discussed in this section against most notable obfuscation schemes. As illustrated the combination of FALL, Bypass and SMT attack can break all existing solutions, pointing us to a need for a new direction for generating non-bypassable SMT hard obfuscation solutions.

The dilemma is that SAT-hard solutions have extremely low output corruption, and are prone to Bypass, FALL, Removal and SPS attack. On the other hand, the traditional logic locking schemes have high output corruption, but could be easily broken with SAT/SMT attack. The compound logic locking solutions that combine the SAT-hard solutions for

Table 2.2: Comparison of proposed attacks/defenses.

| Defenses              | RLL | FLL  | SLL  | Anti-SAT | SARLock | Compound | SFLL | Cyclic | SRCLock | DLL  |

|-----------------------|-----|------|------|----------|---------|----------|------|--------|---------|------|

| Attacks               | [7] | [13] | [12] | [19]     | [18]    | [18]     | [37] | [40]   | [26]    | [27] |

| Brute Force           | Х   | Х    | Х    | Х        | Х       | Х        | Х    | Х      | Х       | ×    |

| Sensitization[12]     | /   | ✓    | Х    | X        | X       | X        | X    | X      | ×       | X    |

| Hill-Climbing[32]     | /   | ✓    | Х    | X        | X       | X        | X    | X      | ×       | X    |

| SAT[10]               | /   | ✓    | /    | X        | X       | X        | X    | X      | ×       | X    |

| SPS+Removal[33][20]   | X   | Х    | Х    | ✓        | ✓       | X        | X    | X      | ×       | X    |

| $\mathrm{Bypass}[24]$ | X   | Х    | Х    | ✓        | ✓       | X        | X    | X      | ×       | X    |

| AppSAT[21]            | /   | /    | /    | X        | X       | P        | X    | X      | ×       | X    |

| Double-DIP[22]        | /   | /    | /    | X        | X       | P        | X    | X      | ×       | X    |

| Bit-Flipping[35]      | /   | ✓    | /    | ✓        | ✓       | ✓        | X    | X      | ×       | X    |

| AGR[33]               | /   | /    | /    | ✓        | ✓       | ✓        | X    | X      | ×       | X    |

| FALL[39]              | X   | Х    | Х    | X        | X       | X        | 1    | X      | ×       | X    |

| CycSAT[41]            | 1   | /    | /    | ×        | ×       | X        | X    | ✓      | ×       | X    |

| BeSAT[42]             | /   | ✓    | /    | X        | X       | X        | X    | ✓      | ×       | X    |

| TimingSAT[44]         | /   | /    | 1    | X        | X       | X        | X    | X      | X       | 1    |

| SMT[43]               | ✓   | ✓    | 1    | X        | X       | P        | X    | ✓      | ✓       | ✓    |

✓: Attack Success, ✗: Fail to Attack, P: Only removes the key to the traditional locking in Compound Defense.

resistance against SAT and SMT attack, and traditional logic locking for resistance against Bypass, FALL, Removal and SPS attack are also prone to approximate SAT and SMT attacks. What is really desired, is a SMT-hard logic locking scheme with high degree of output corruption. As a step in this direction, few very recent research papers have focused on increasing the execution time of each SAT/SMT iteration rather than the total execution time [45, 46]. The Full-Lock in [45] is argued that the strength of SAT/SMT solvers come from their Conflict-Driven Clause Learning (CDCL) ability, which is resulted by recursively calling Davis-Putnam-Logemann-Loveland (DPLL) algorithm. Hence, the Full-Lock creates an obfuscation method that results in very deep recursive call trees. They argue that the SAT/SMT attack execution time can be expresses by formula 2.1, in which N denotes the number of iterations (DIPs) of the SAT/SMT attack,  $T_{DPLL}(\Phi)$  is the execution time of recursive calls for DPLL algorithm on CNF  $\Phi$ , and t is the execution time of the remaining book keeping code executed at each iteration.

$$T_{Attack} = \sum_{i=1}^{N} T(i) = \sum_{i=1}^{N} (t + T_{DPLL}(\Phi)) = \sum_{i=1}^{N} \sum_{j=1}^{M} (T_{DPLL}^{Avg}) \simeq MN \times T_{DPLL}^{Avg}$$

(2.1)

Authors argue that M in formula 2.1 denotes the number of recursive DPLL calls. Accordingly, the execution time of SAT attack could also become unfeasible by building an exponential relation between the percentage gate inserted (area overhead) and M. The strong aspect of this alternative solution is that (1) the problems posed at each iteration of SAT/SMT attack is a SAT-hard problem, (2) the output corruption of this methods is significantly higher than obfuscating solution relying on increasing the N, (3) it is not susceptible to SPS, removal, bypass, approximate attack, to name a few. The hardness of SAT/SMT attack in the solution posed by Full-Lock cannot be assessed/formulated similar to that of SFLL. Moving towards this new direction for generating SAT-hard problems with high level of output corruption can be generalized more, where an obfuscation solution in this direction can engineer the number of recursive calls, pushing the number of recursive call to be an exponential function of added gates counts (area overhead).

## Chapter 3: SMT Attack: Next Generation Attack on Obfuscated Circuits

In this section, we present Satisfiability Modulo Theory (SMT)-based attack on obfuscated circuits, that expands the capabilities of previously proposed SAT attack by assigning theory solvers to monitor the behavioral and non-functional properties of the obfuscated circuit. To illustrate the capabilities of SMT attack, we use an SMT solver and invoke a graph-theory solver to break the logic and timing obfuscation scheme introduced in [27].

## 3.1 Boolean Logic Obfuscation

Logic locking and netlist obfuscation schemes introduce limited programmability into a netlist by means of inserting additional key programmable gates at design time. After fabrication, the functionality of the IC is programmed by loading the correct key-values. The key-inputs could be stored in and driven by an on-chip tamper-proof memory [28]. The purpose of inserting key-gates is protecting the IC design from untrusted foundries. Since the functionality of a design is locked with a secret key, the attacker cannot learn the functionality of the obfuscated netlist after reverse engineering. Logic locking and obfuscation schemes vary in terms of the usage of different key-gates types and key-gates insertion policies [47,48]. For combinational circuits, logic locking can be classified based on key-gates types to different categories. XOR/XNOR based logic locking [7,12], MUX based logic locking, and LUT based logic locking [14,15] are the most common mechanisms. Also, there are different algorithms for inserting the key-gates in the circuit. Some of these policies include random insertion (RLL), fault-analysis (FLL) insertion, and interference-based logic locking (SLL) algorithms, SARLock, Anti-SAT, etc. [7,12,13,18,19].

Figure 3.1: 10-Year History of Logic Obfuscation.

Fig. 3.1 captures the evolving history of obfuscation defense schemes and attack formulations since the year 2008 to the current date. After introduction of SAT attack, in 2015 in [9,10], as illustrated in this figure, researchers proposed various mechanisms for building SAT hard obfuscation solutions. However, many of such obfuscation schemes were later broken using newer attacks like as SPS, removal, bypass, and AppSAT [20–22,24,33], making the current defense schemes unreliable. After 2017, a new breed of obfuscation schemes instead of building logical obfuscation schemes has been introduced, relied on breaking the SAT assumptions for building SAT hard solutions without having the vulnerabilities of the previous SAT-Hard solution. For example, Cyclic obfuscation [40] and its improved defense, the SRCLock[26], by introducing cycles into netlist break the SAT model as the netlist can no longer be represented by a Directed Acyclic Graph (DAG). Alternatively, the Delay Logic Locking (DLL) [27] extends the reach of obfuscation beyond logic and locks the circuit using its delay and timing properties, attempting to build SAT hard solutions. In this work, we introduce the SMT attack that could break such locking and obfuscation mechanisms by means of parallel invocation of SAT and theory solvers to model the non-logical and behavioral aspects of a circuit operation.

## 3.2 Behavioral logical obfuscation

As previously discussed, the logic-based obfuscation schemes that rely on extending the Boolean behavior of a circuit can be broken by at least one of the state-of-the-art attacks, including SAT, SPS, removal, bypass, and AppSAT [9,10,20–22,24,33]. Hence, recent researches have been focused on obfuscation schemes that fundamentally violate the assumptions of these attacks with respect to the nature of obfuscated circuit, or use non-logical properties of a netlist to obfuscate its behavior [26, 27, 40].

For lack of EDA tool support and limited knowledge in designing cyclic Boolean logic, most of all netlists designed and fabricated today are acyclic. One of the first attempts to break the state of the art attacks, including SAT attack, was proposed in [40] which suggested using cycles in combinational circuits, and illustrated that use of cycles results in either a SAT solver being trapped, or it generates incorrect key even after timely termination. This obfuscation scheme, however was shortly after broken by CycSAT attack in [41]. In the CycSAT attack, the netlist is first pre-processed based upon which a set of constraining clauses are generated. The CycSAT attack then uses these constraining clauses, in the original SAT attack, allowing the SAT solver to effectively open the cycles without being trapped, or incorrectly terminated. However, the limitation of [40] was addressed in SRCLock [26] to prevent a pre-processor from extracting all needed constraints from a cyclically locked circuit. SRCLock focuses on building an exponential relation between the number of inserted feedbacks and number of generated cycles by means of creating super cycles.

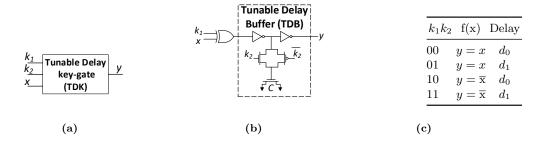

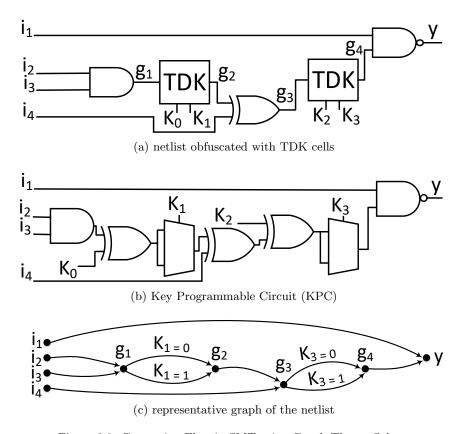

The second obfuscation of interest to this work is the logic and timing obfuscation scheme in [27]. In this obfuscation scheme, the delay properties of a circuit are obfuscated with the ultimate goal of introducing setup and hold violation if the correct key is not applied. In this case, the obfuscation, in addition to the logical behavior of the netlist, attempts to change its behavioral (timing) properties. Considering that timing is not translatable to CNF, the SAT solver remains oblivious to the keys used for timing obfuscation. Hence using a SAT attack to deobfuscated this circuit, result in a discovery of all keys used for

logic obfuscation, but random assignment to all keys used for timing obfuscation and the circuit remains locked.

In this work, we construct an attack based on Satisfiability Modulo Theory solvers, and illustrate that the capability of this attack goes far beyond that of SAT attacks. More precisely, with specific formulation, we illustrate that SMT attack on obfuscated circuits could be significantly faster and more efficient compared to SAT attacks on Boolean logic obfuscation. Additionally, it could be used to attack behavioral logic obfuscation schemes, which is not possible by a pure SAT-based attack. To illustrate the second point, we attack and break the timing-logic obfuscation scheme in [27], based on which we generalize and illustrate how other similar SMT attacks could be formulated.

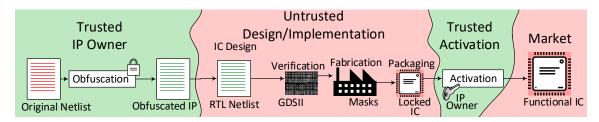

#### 3.3 Attack Model

The SMT attack is an oracle-guided attack. We assume that the attacker has the reverse engineered but obfuscated netlist and a functional IC (oracle) that is unlocked. The attacker can query the oracle with any stimuli i, and observe its output o. The purpose of the attack is to find the key inputs, that make the obfuscated netlist logically equivalent to that of the unlocked netlist.

As it can be seen in Fig. 3.2, IP owner obfuscates the Original Netlist of IP. Assuming that design integration, verification, fabrication, and packaging have been accomplished in untrusted regime, attacker is able to obtain the obfuscated (locked) netlist from (1) the IC design, or by reverse engineering the (2) synthesis/implementation (layout), (3) mask, or (4) a manufactured IC. In addition, the attacker is able to buy the correctly unlocked (activated) IC in the open market. Consequently, the attacker can apply arbitrary input to activated IC and observe its corresponding output.

Figure 3.2: ASIC Design Flow Integrated with Obfuscation/Activation.

#### 3.4 Limitation of SAT Attack