#### MACHINE LEARNING-BASED SOLUTIONS FOR SECURE AND ENERGY-EFFICIENT COMPUTER SYSTEMS

by

Hossein Sayadi A Dissertation Submitted to the Graduate Faculty of

George Mason University In Partial fulfillment of The Requirements for the Degree

of

Doctor of Philosophy Electrical and Computer Engineering

Committee:

|       | Dr. Houman Homayoun, Dissertation Director                   |

|-------|--------------------------------------------------------------|

|       | Dr. Setareh Rafatirad, Co-director                           |

|       | Dr. Jim Jones, Committee Member                              |

|       | Dr. Avesta Sasan, Committee Member                           |

|       | Dr. Monson H. Hayes, Department Chair                        |

|       | Dr. Kenneth S. Ball, Dean, The Volgenau Schoo of Engineering |

| Date: | Summer Semester 2019 George Mason University Fairfax, VA     |

# Machine Learning-Based Solutions for Secure and Energy-Efficient Computer Systems

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

By

Hossein Sayadi Master of Science Sharif University of Technology, 2014 Bachelor of Science K. N. Toosi University of Technology, 2012

Director: Dr. Houman Homayoun, Associate Professor Co-director: Dr. Setareh Rafatirad, Associate Professor Department of Electrical and Computer Engineering

> Summer Semester 2019 George Mason University Fairfax, VA

Copyright © 2019 by Hossein Sayadi All Rights Reserved

# Dedication

This thesis is dedicated to my wife, Tahereh, who has been a constant source of support and encouragement during the challenges of graduate school and life. This work is further dedicated to my parents, who have always loved me unconditionally. I am enormously grateful and indebted to them for their continuous love and support.

# Acknowledgments

First and foremost, I would like to take this opportunity to express my deepest gratitude from my supervisor Dr. Houman Homayoun for all his extensive guidance, advice, and continuous support during my doctoral studies. In particular, I am truly grateful to Houman for providing me valuable and insightful research opportunities, for his patience and understanding throughout the thesis that has set an example of excellence as a professional researcher and mentor for me. In addition, I would like to thank my co-advisor Dr. Setareh Rafatirad for all her support and valuable advice and feedbacks towards the completion of my thesis. I cannot thank Houman and Setareh enough for all influential insights and valuable experiences that I have learnt from them, for their attention to details and in-depth knowledge that has helped me grow as a researcher, and for their encouragement, concern, and interest towards my success.

I would also like to thank my other committee members, Dr. Avesta Sasan and Dr. Jim Jones for their insightful comments and feedbacks which have helped me address the research questions in a much broader aspect. Furthermore, I want to express my gratitude from Dr. Paolo Costa for his time and support giving me valuable advice and insights about my path towards the academic career.

My special gratitude to my family, particularly my Mom and Dad for their unconditional love and constant support. The holidays would have been so lonely without them. I am enormously grateful and indebted to my lovely parents for their kindness, dedication, and the education they offered me, and for having always supported me, believed in me and encouraged me to pursue my life-long dreams and goals.

Last but not least, a heartfelt gratitude and appreciation go out to my lovely wife, Tahereh, for all her love, constant support, understanding, and patience during the challenges of graduate school and life. You have always been my constant source of support and encouragement during all days and nights of research and hard work in my academic education. You were always there caring for me making all the stressful days and nights full of joy and memory. Tahereh, with out your unconditional love, encouragement, and support my academic achievements and completion of this research would not have been possible.

# **Table of Contents**

|     |         |                                                                    | Page |

|-----|---------|--------------------------------------------------------------------|------|

| Lis | st of 7 | Γables                                                             | viii |

| Lis | st of I | Figures                                                            | X    |

| Ab  | strac   | t                                                                  | xiii |

| 1   | Intr    | roduction                                                          | 1    |

|     | 1.1     | Ensemble Learning for Effective Run-Time                           |      |

|     |         | Hardware-Based Malware Detection                                   | 2    |

|     | 1.2     | A Two-Stage Machine Learning-Based Approach for Run-Time Spe-      |      |

|     |         | cialized Malware Detection                                         | 4    |

|     | 1.3     | Stealthy Malware Detection using Microarchitectural Features       | 6    |

|     | 1.4     | Machine Learning-Based Approaches for Energy-Efficiency Prediction |      |

|     |         | in Heterogeneous Architectures                                     | 7    |

| 2   | Bac     | ekground and Related Work                                          | 10   |

|     | 2.1     | Hardware Performance Counter Registers                             | 10   |

|     | 2.2     | Machine Learning Techniques used for Malware Detection             | 11   |

|     |         | 2.2.1 Performance Evaluation Metrics                               | 14   |

|     | 2.3     | Comprehensive Analysis of State-of-the-Art                         | 18   |

|     |         | 2.3.1 Hardware-Based Malware Detection                             | 18   |

|     |         | 2.3.2 Energy-Efficient Heterogeneous Architectures                 | 19   |

| 3   | Ens     | semble Learning for Effective Run-Time Hardware-Based Malware De-  |      |

|     | tecti   | on                                                                 | 23   |

|     | 3.1     | Ensemble Learning                                                  | 27   |

|     |         | 3.1.1 Boosting                                                     | 27   |

|     |         | 3.1.2 Bagging                                                      | 28   |

|     | 3.2     | Proposed Run-Time Malware Detection                                | 29   |

|     |         | 3.2.1 Experimental Setup and Data Collection                       | 29   |

|     |         | 3.2.2 Feature Selection                                            | 31   |

|     |         | 3.2.3 Training and Testing the Malware Detectors                   | 32   |

|   | 3.3  | Exper   | imental Results and Evaluation                                 | 33 |

|---|------|---------|----------------------------------------------------------------|----|

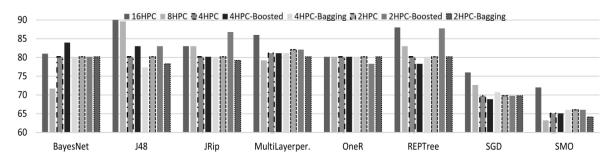

|   |      | 3.3.1   | Detection Accuracy                                             | 34 |

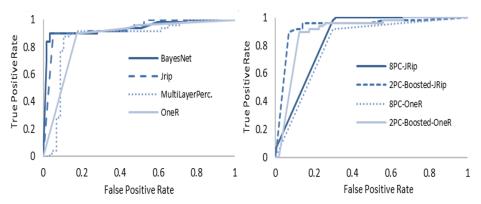

|   |      | 3.3.2   | Classification Robustness                                      | 35 |

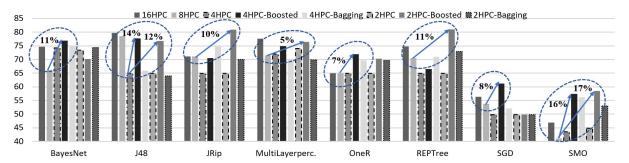

|   |      | 3.3.3   | Performance of Malware Detection                               | 37 |

|   |      | 3.3.4   | Hardware Implementation Results                                | 36 |

| 4 | 2SN  | IaRT N  | Malware Detection Approach                                     | 43 |

|   | 4.1  | Motiv   | ation                                                          | 48 |

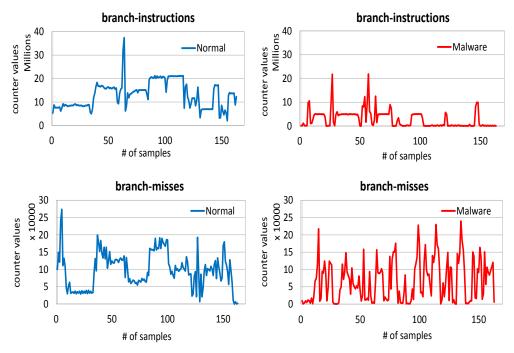

|   |      | 4.1.1   | Malware Detection using HPCs Data                              | 48 |

|   |      | 4.1.2   | The Need for Specialized Malware Detectors and Per-class Anal- |    |

|   |      |         | ysis                                                           | 50 |

|   |      | 4.1.3   | Impact of Number of HPCs on Malware Detection                  | 51 |

|   | 4.2  | Propo   | sed Malware Detection Framework                                | 52 |

|   |      | 4.2.1   | Experimental Setup and Data Collection                         | 52 |

|   |      | 4.2.2   | Feature Reduction                                              | 54 |

|   |      | 4.2.3   | Overview of the Proposed Two-stage HMD                         | 58 |

|   | 4.3  | Exper   | imental Results                                                | 62 |

|   |      | 4.3.1   | Evaluation Metrics                                             | 62 |

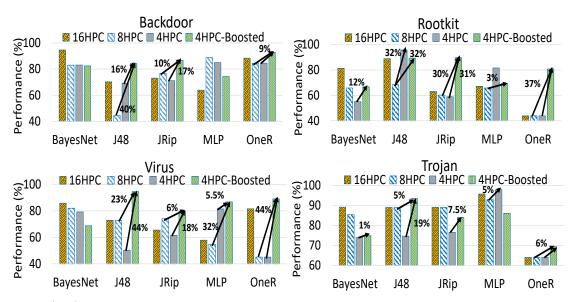

|   |      | 4.3.2   | Evaluation of Per-class Malware Detection                      | 64 |

|   |      | 4.3.3   | Evaluation of Malware Detection with Limited Available HPCs    | 67 |

| 5 | Stea | althy M | Ialware Detection using Low-Level HPC Features                 | 74 |

|   | 5.1  | Backg   | ground on Stealthy Malware Detection                           | 77 |

|   |      | 5.1.1   | Embedded Malware Detection                                     | 77 |

|   |      | 5.1.2   | Time Series Classification                                     | 78 |

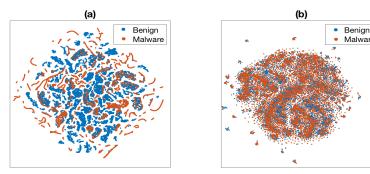

|   | 5.2  | Motiv   | ational Case Studies                                           | 79 |

|   |      | 5.2.1   | Challenge of Detecting Embedded Malware                        | 79 |

|   |      | 5.2.2   | Machine Learning for Hardware-Based Embedded Malware De-       |    |

|   |      |         | tection                                                        | 80 |

|   | 5.3  | Propo   | sed Embedded Malware Detection Approach                        | 81 |

|   |      | 5.3.1   | Data Collection                                                | 82 |

|   |      | 5.3.2   | Feature Representation                                         | 83 |

|   |      | 5.3.3   | Embedded Malware Threat Models                                 | 84 |

|   |      | 5.3.4   | Embedded Malware Data Generation                               | 85 |

|   |      | 5.3.5   | Overview of CHASE                                              | 86 |

|   | 5 4  | Exper   | imental Results and Analysis                                   | 91 |

|     |        | 5.4.1   | Performance Evaluation Criteria                               | 91  |

|-----|--------|---------|---------------------------------------------------------------|-----|

|     |        | 5.4.2   | Evaluation of Proposed Approach                               | 92  |

| 6   | Sch    | eduling | Challenges in Heterogeneous Architectures                     | 98  |

|     | 6.1    | Machi   | ne Learning-based Approaches for Energy-Efficiency Prediction |     |

|     |        | in CC   | As                                                            | 98  |

|     |        | 6.1.1   | Motivation and Overview of our Approach                       | 102 |

|     |        | 6.1.2   | Experimental Setup and Methodology                            | 104 |

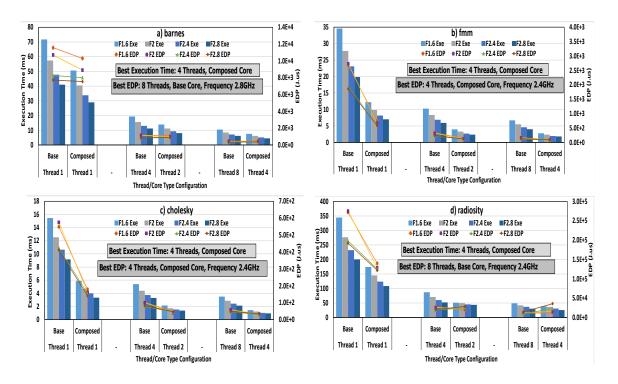

|     |        | 6.1.3   | Characterization Results                                      | 105 |

|     |        | 6.1.4   | Predictive Modeling                                           | 113 |

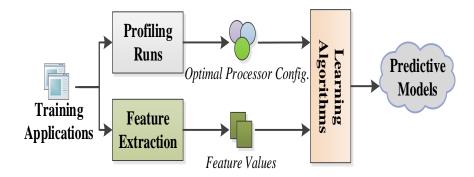

|     |        | 6.1.5   | Training the Predictor                                        | 114 |

|     |        | 6.1.6   | Prediction Phase                                              | 117 |

|     |        | 6.1.7   | Experimental Results                                          | 118 |

|     | 6.2    | Power   | Conversion Efficiency-Aware Mapping of Multithreaded Appli-   |     |

|     |        | cation  | s on HMPs                                                     | 124 |

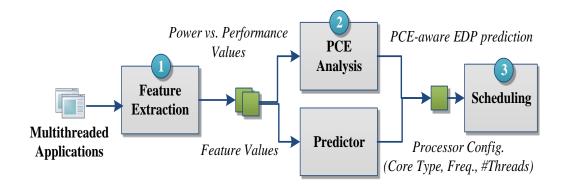

|     |        | 6.2.1   | Overview of PCE-Aware Scheduling                              | 127 |

|     |        | 6.2.2   | Experimental Setup and Methodology                            | 129 |

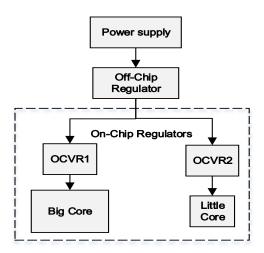

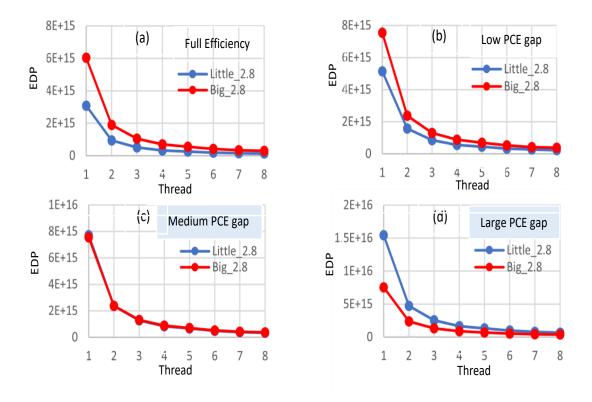

|     |        | 6.2.3   | Power Conversion Efficiency Analysis                          | 130 |

|     |        | 6.2.4   | Proposed Scheduling Framework                                 | 133 |

|     |        | 6.2.5   | Prediction Model for Energy-efficiency                        | 136 |

|     |        | 6.2.6   | Evaluation Results                                            | 142 |

| 7   | Con    | clusion |                                                               | 146 |

| A   | List   | of Pub  | olications                                                    | 148 |

| Bił | oliogr | aphy .  |                                                               | 152 |

# List of Tables

| Table | F                                                                          | Page |

|-------|----------------------------------------------------------------------------|------|

| 2.1   | Evaluation metrics for performance of malware detection techniques .       | 16   |

| 3.1   | Hardware performance counters in order of importance                       | 33   |

| 3.2   | AUC values for all general and ensemble detectors with varying number      |      |

|       | of HPCs                                                                    | 34   |

| 3.3   | Hardware implementation results of various ML-based malware detectors      | s 41 |

| 4.1   | ML solutions with highest detection rate                                   | 51   |

| 4.2   | Prominent top eight HPC features for each class of malware                 | 57   |

| 4.3   | F measure of 2SMaRT detectors with and without ensemble learning           | 65   |

| 4.4   | Hardware implementation results of 2SMaRT                                  | 69   |

| 4.5   | Average performance improvement of 2SMaRT with AdaBoost across             |      |

|       | all four malware classes                                                   | 70   |

| 5.1   | HPC features used for malware detection and their description              | 84   |

| 5.2   | Evaluation results for validation set                                      | 93   |

| 5.3   | AUC of testing set results for detecting various embedded malware .        | 94   |

| 5.4   | Evaluation results for testing set for detection of various embedded       |      |

|       | malware                                                                    | 97   |

| 6.1   | Architectural specification                                                | 105  |

| 6.2   | Optimal configurations with optimization target of EDP for different       |      |

|       | architectures                                                              | 107  |

| 6.3   | Optimal configurations in different parallel regions of radix and cholesky |      |

|       | applications for EDP optimization                                          | 111  |

| 6.4   | Optimal configurations in different parallel regions of fft and lu.cont    |      |

|       | applications for EDP optimization                                          | 112  |

| 6.5   | ML classifiers used for prediction                                         | 114  |

| 6.6   | HPCs data used for training the classifiers                                | 114  |

| 6.7   | Hardware implementation reports of various ML classifiers                  | 122  |

| 6.8  | Architectural specification                                                 | 129 |

|------|-----------------------------------------------------------------------------|-----|

| 6.9  | PCE scenarios for little and big core VRs                                   | 130 |

| 6.10 | .10 Optimal configurations with optimization target EDP for full efficiency |     |

|      | PCE and large gap PCE model                                                 | 135 |

| 6.11 | Average relative error                                                      | 142 |

# List of Figures

| Figure |                                                                        | Page |

|--------|------------------------------------------------------------------------|------|

| 2.1    | Confusion matrix layout for a machine learning classifier              | 17   |

| 3.1    | Ensemble learning block diagrams a) AdaBoost, b) Bagging               | 27   |

| 3.2    | The overview of the proposed run-time hardware-based malware de-       |      |

|        | tection framework                                                      | 30   |

| 3.3    | The functionality of ML-based malware detectors                        | 32   |

| 3.4    | Detection accuracy results (ACC) for various ML classifiers with vary- |      |

|        | ing number of HPCs                                                     | 35   |

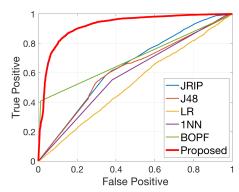

| 3.5    | The ROC curves for ML-based malware detectors                          | 36   |

| 3.6    | Performance results (ACC*AUC) for various ML classifiers with vary-    |      |

|        | ing number of HPCs                                                     | 38   |

| 4.1    | HPC traces of two different features (branch-instructions and branch   |      |

|        | misses) for sample malware and normal programs                         | 49   |

| 4.2    | Case study for impact of #HPCs on HMD                                  | 51   |

| 4.3    | The overview of the proposed hardware-assisted malware detection       |      |

|        | framework                                                              | 53   |

| 4.4    | Reduced HPC features after first level of reduction                    |      |

| 4.5    | 2SMaRT overview, the proposed two-stage run-time hardware-assisted     |      |

|        | malware detection approach                                             |      |

| 4.6    | Malware detection performance of 2SMaRT for various ML classifiers     |      |

|        | across different malware classes                                       |      |

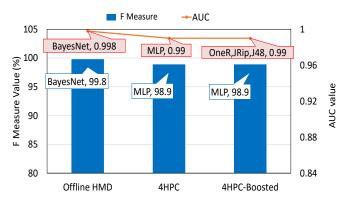

| 4.7    | Optimal F measure and AUC of run-time 2SMaRT compared with             |      |

|        | offline HMD using all 44 HPCs                                          | 72   |

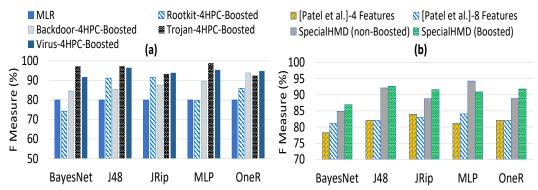

| 4.8    | Comparison of 2-stage 2SMaRT with single-stage HMDs: a) compari-       |      |

|        | son with 1 stage MLR, b) comparison of 2SMaRT using only 4 features    |      |

|        | with a recent HMD work                                                 | 73   |

| 5.1                                                                      | 5.1 Visualizing the complete benign and malware dataset using t-SNE al-       |                      |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------|

|                                                                          | gorithm: a) malware spawned as separate thread b) malware embedded            |                      |

|                                                                          | inside benign applications                                                    | 80                   |

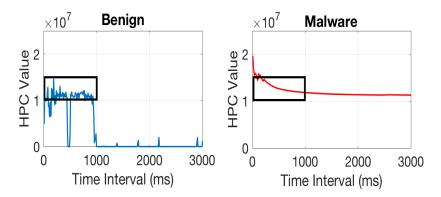

| 5.2                                                                      | HPC traces of benign and malware for branch-inst                              | 81                   |

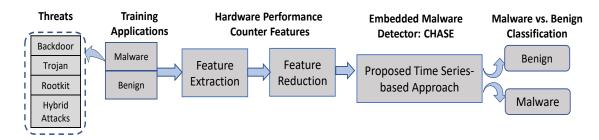

| 5.3                                                                      | An overview of different steps of proposed malware detection framework        | 82                   |

| 5.4                                                                      | Overview of CHASE, the proposed embedded malware detection ap-                |                      |

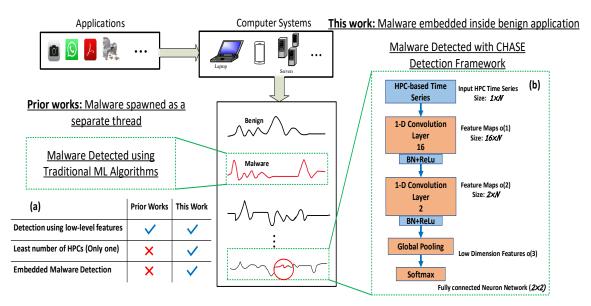

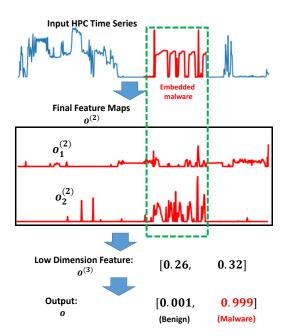

|                                                                          | proach, and its contribution over prior HMD works                             | 87                   |

| 5.5                                                                      | Case study for CHASE in detecting embedded malware                            | 89                   |

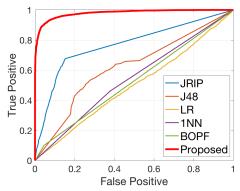

| 5.6                                                                      | ROC Curve for Hybrid Embedded Malware detection                               | 93                   |

| 5.7                                                                      | ROC Curve for Rootkit Embedded Malware detection                              | 94                   |

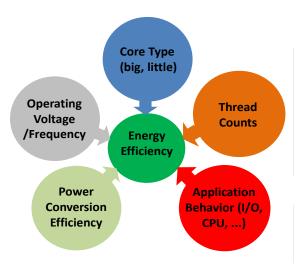

| 6.1                                                                      | Tuning parameters influencing energy-efficiency in heterogeneous mul-         |                      |

|                                                                          | ticore architectures                                                          | 101                  |

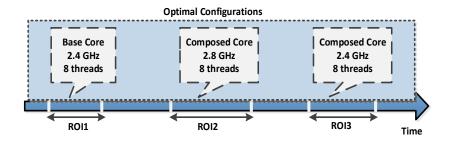

| 6.2                                                                      | Optimal configurations in different parallel regions of an application .      | 102                  |

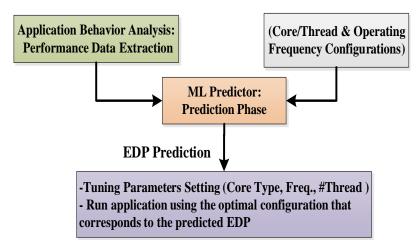

| 6.3                                                                      | An overview of our approach for predicting the optimal configuration          |                      |

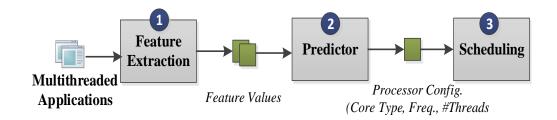

|                                                                          | and scheduling the multithreaded application                                  | 104                  |

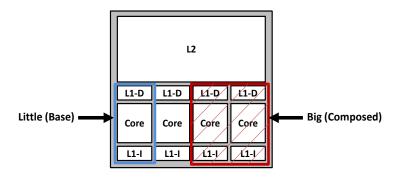

| 6.4                                                                      | Conceptual structure of a four core CCA                                       | 105                  |

| 6.5                                                                      | Execution Time and EDP of a) barnes, b) fmm, c) cholesky, d) radiosity        |                      |

|                                                                          | with various Core Types, Threads, Frequencies                                 | 106                  |

| 6.6                                                                      | Training process for machine learning predictive models                       | 116                  |

| 6.7                                                                      | Energy-efficiency prediction and tuning parameters configuration 11           |                      |

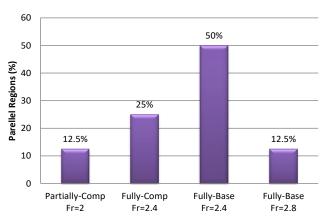

| 6.8                                                                      | The distribution of the optimal configurations for EDP for $8$ Base/4Composed |                      |

|                                                                          | architecture                                                                  | 120                  |

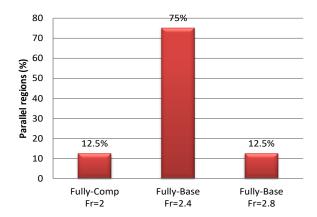

| 6.9 The distribution of the optimal configurations for EDP for 4Base/2Co |                                                                               | $\operatorname{sed}$ |

|                                                                          | architecture                                                                  | 120                  |

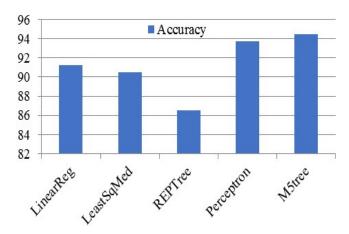

| 6.10                                                                     | Comparison of EDP prediction accuracy of ML classifiers                       | 121                  |

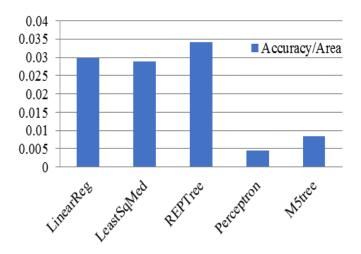

| 6.11                                                                     | Accuracy/Area ratio comparison between ML predictors                          | 122                  |

| 6.12                                                                     | An overview of the PCE-aware learning-based approach                          | 128                  |

| 6.13                                                                     | The power-supply configurations for the experimental HMP $$                   | 131                  |

| 6.14                                                                     | Energy-efficiency (in terms of EDP) of barnes for four different PCE          |                      |

|                                                                          | gaps between little and big cores: a) full efficiency, b) low, c) medium,     |                      |

|                                                                          | d) large                                                                      | 132                  |

| 6.15                                                                     | Optimal core type selection for different power conversion efficiencies       |                      |

| 6.16 | Quantile graphs for predictors: a) L2-Access, b) Branch miss prediction         | 138 |

|------|---------------------------------------------------------------------------------|-----|

| 6.17 | $^7$ Proposed PCE-aware scheduling scheme with energy-efficiency prediction 139 |     |

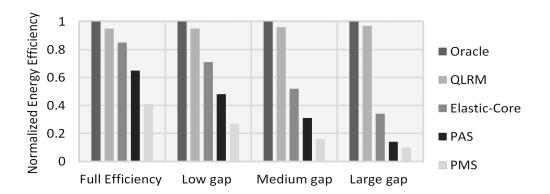

| 6.18 | Normalized energy-efficiency of applications on various scheduling scheme       | S   |

|      | relative to Oracle scheduling                                                   | 143 |

| 6.19 | Average energy-efficiency results of different scheduling schemes with          |     |

|      | respect to various PCE models                                                   | 145 |

**Abstract**

MACHINE LEARNING-BASED SOLUTIONS FOR SECURE AND ENERGY-EFFICIENT

COMPUTER SYSTEMS

Hossein Sayadi, PhD

George Mason University, 2019

Dissertation Director: Dr. Houman Homayoun

Dissertation Co-director: Dr. Setareh Rafatirad

The ever-increasing complexity of modern computing systems results in the growth of security vulnerabilities, making such systems appealing targets for increasingly sophisticated cyber attacks. The recent proliferation of computing devices in embedded systems and Internet-of-Things domains has further exacerbated the impact of cyber attacks calling for effective detection techniques. In this work, we attempt to describe how Machine Learning (ML) techniques and applications run-time information at the hardware-level can be effectively used to address major challenges of detecting emerging attacks. In response to the latency and inefficiencies of software-based malware detection techniques, Hardware-assisted Malware Detection (HMD) has emerged as a promising solution to enhance the security of computing systems. HMD techniques rely on ML classifiers to detect patterns of malicious applications based on low-level microarchitectural features captured by processors Hardware Performance Counters (HPCs) during execution.

In this work, we propose effective machine learning-based approaches using lowlevel HPC information to address the security and energy-efficiency challenges of the modern computer systems. For the purpose of security enhancement, four key challenges to realize an effective run-time hardware-assisted malware detection are identified and addressed. These challenges include: 1) the type of key microarchitectural events to capture at run-time which varies across various malware classes; 2) no unique ML classifier achieves high malware detection rate across various types of malware; 3) the number of available HPC registers that can be monitored simultaneously is very limited in modern microprocessors; and 4) traditional ML-based solutions fail to detect the malware accurately when the attack is embedded in a benign application, as the microarchitectural data is polluted by both malware and benign applications data. Our comprehensive analysis shows that all of these influencing parameters highly depend on the class of malware and change across various malware classes (Virus, Rootkit, Backdoor, and Trojan), i.e. the ML classifier and the type of events to collect at run-time out of many microarchitectural events that deliver the highest detection rate and performance, highly depend on the class of malware. For each of these challenges, effective machine learning-based solutions are proposed to accurately detect malware at run-time. The experimental results for the proposed run-time HMD techniques show that the malware can be detected with 98.9% detection rate at run-time with limited available HPC resources, matching to almost what can be achieved offline having access to all microarchitectural data.

Furthermore, for the last part of this research, in order to address the energy-efficiency challenges, we focus on the suitability of deploying effective machine learning techniques on run-time HPC-based information for addressing the performance vs. power consumption trade-offs and enhancing the energy-efficiency of modern heterogeneous multicore architectures. In overall, this research is primarily focused on developing highly accurate and complexity-aware machine learning-based solutions for

security and energy-efficiency enhancement of modern computer architectures based on the application's microarchitectural events captured at run-time.

As a result, the outcome of this research opens a path for computer architects and embedded systems designers in making appropriate and efficient architectural decisions for implementing future generation of computer systems, to most effectively improve the performance of machine learning algorithms for different optimization goals such as security and energy-efficiency of computer systems for emerging applications.

## **Chapter 1: Introduction**

Electronic system security, trust and reliability has become an increasingly critical area of concern for modern society [1–5]. Secure hardware systems, platforms, as well as supply chains are critical to industry and government sectors such as national defense, healthcare, transportation, and financial [6,7]. Traditionally, authenticity and integrity of data has been protected with various security protocol at the software level with the underlying hardware assumed to be secure, and reliable. This assumption however is no longer true with an increasing number of attacks reported on the hardware. The ever-increasing complexity of modern computing systems has led into the considerable evolution of security vulnerabilities, making such systems appealing targets for sophisticated cyber attacks. With the advent of hardware vulnerabilities and evolution of sophisticated cyber attacks, the attention of computer systems and security researchers have shifted towards working on the *Hardware Cybersecurity* research domain and improving the security of computer systems using the hardware features and characteristics [1,2,8–12].

Methods of Machine Learning (ML), which build predictive models that generalize training data, have proven to be useful for detecting the behavior of applications [1,13,14]. Machine learning techniques are used in a wide variety of applications, such as computer vision, robotics, design space exploration, and performance evaluation of computer systems where it is infeasible to develop an algorithm of specific instructions for performing the task [15,16]. Machine learning is basically closely related to computational statistics, which focuses on making predictions using computers.

In this thesis, we primarily attempt to describe how machine learning techniques and applications run-time information at the microarchitectural and hardware level can be effectively deployed to address major challenges of security and energy-efficiency improvement of modern computer systems. In particular, in this research we make use of various machine learning techniques and applications run-time signatures left on the underlying hardware for the purpose of secure and energy-efficient computer architecture. To this aim, we propose effective machine learning-based solutions which rely on the run-time traces collected from hardware events registers that are built in modern microprocessors. In order to clearly highlight the scope and different categories of research performed in this thesis, in following we briefly describe the general overview of performed researches in this work that all will be presented in the upcoming sections of this thesis.

# 1.1 Ensemble Learning for Effective Run-Time Hardware-Based Malware Detection

Malware is a piece of program developed by cyber-attackers to perform various malicious activities, such as destroying the data, stealing information, running destructive or intrusive programs on devices to perform Denial-of-Service (DoS) attack, and gaining root access without the consent of user [1,2,10,13,17–19]. Malware detection can be simplified as a binary classification problem regardless of what detection method is being used. Traditional malware detection approaches such as signature-based detection and semantics-based anomaly detection are considered as software-based solutions and incur significant computational overheads.

On the other hand, recent studies have demonstrated that malicious software behavior can be differentiated from benign applications by classifying anomalies in the low-level feature spaces such as microarchitectural events collected by Hardware Performance Counter (HPC) registers [1, 2, 10, 13, 20–24]. As a result, malware detection using HPCs microarchitectural events has emerged as a promising alternative to traditional malware detection methods. As learning the underlying patterns of these microarchitectural events can aid in detecting malware, machine learning (ML) techniques are widely deployed for malware detection.

Recently, there has been a number of work on Hardware-based Malware Detection (HMD) using HPCs information. However, these works performed a limited study on malware classification accounting for the availability of a large number (e.g. 16 or 32) and diverse type of HPCs. While, modern processors in the high-performance domain have a small number of HPCs (2 to 8), due to several reasons including the design complexity and cost of concurrent monitoring of microarchitectural events [1, 25, 26]. Due to deep pipelines, complex prefetchers, branch predictors, modern cache design etc., HPCs implementation becomes a great challenge in terms of counting multiple events and maintaining counter accuracy at the same time under speculative execution [26]. Better accuracy requires better and more complex hardware design hence increasing the number of counters with limited accuracy doesn't appear to be a good trade-off.

Therefore, collecting a variety of microarchitectural events, more than the number of available HPCs, to achieve high accuracy using the general ML models presented in prior work, requires running the application multiple times, since the hardware can only count a small subset of events concurrently. This approach is not practical for run-time detection of malware.

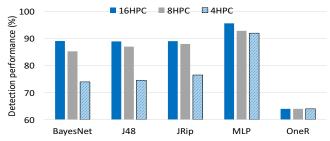

As the performance of malware detection depends on the type of ML classifier applied and the number and type of HPC events used, in this work, we first illustrate the impact of ML classifier type on malware detection accuracy and performance and the effect of number of HPC events for malware detection. To achieve a high accuracy across all studied general ML classifiers, of more than 80%, at least 16 hardware performance counters are required, which as discussed is not available in modern processors, even in the high-performance domain, making run-time detection of malware impractical using these methods. Therefore, a key challenge in making the hardware-based malware detection a practical run-time solution is how to use a limited number of HPCs available in a microprocessor (for instance 2 or 4) and match the accuracy and performance of malware detection with the ones that can be achieved by a larger number of HPC events (for instance 16 or 32).

In this work, we address this challenge by proposing effective ensemble learning techniques to improve the accuracy and performance of the hardware-based malware detectors and break the trade-off between accuracy/performance with respect to the number of HPCs. We explore the effectiveness of ensemble learning models in 1) reducing the number of required performance counters for implementing effective ML classifiers for run-time malware detection and 2) improving the performance of weak but low-cost classifiers in malware detection with a small number of HPCs.

# 1.2 A Two-Stage Machine Learning-Based Approach for Run-Time Specialized Malware Detection

The ever-increasing complexity of modern computing systems results in the growth of security vulnerabilities, making such systems appealing targets for increasingly sophisticated attacks [2, 11, 12, 27]. The attackers take advantage of vulnerabilities to compromise systems and deploy malicious activities. According to a 2018 McAfee threats report [28], nearly 63 million new malware samples have been recorded in the third quarter of 2018, an all-time highest number with an increase of more than 53%

from the second quarter of 2018. The recent proliferation of computing devices in mobile and Internet-of-Things (IoT) domains further exacerbates the malware threats calling for effective malware detection solutions.

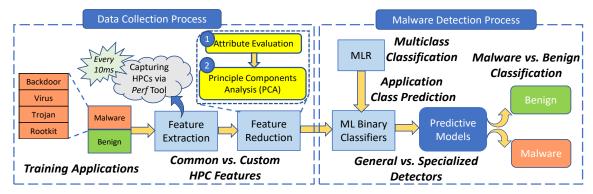

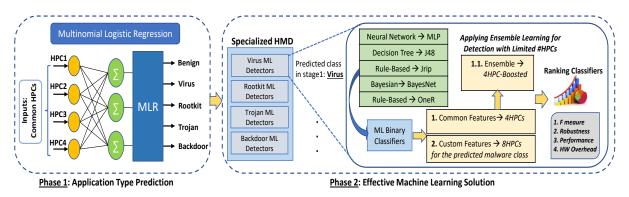

While previous studies on hardware-assisted malware detection focus on one or few general ML classifiers and limited classes of malware [20–23, 29–32], it is not clear which of the ML models deliver the best results across various metrics including the detection rate, performance, hardware design overheads as well as detection delay across various classes of malware. In addition to the drawbacks of existing approaches and non-portability concerns, in this section, we will identify and address major challenges to realize an effective run-time hardware-assisted malware detection including 1) determining the key microarchitectural events for effective malware detection, 2) the right machine learning deployed for HMD, and 3) malware detection with limited available HPC resources. For each of these challenges, effective machine learning-based solutions are proposed to accurately detect malware at run-time.

The objective of this research is to improve the detection rate and performance of malware detection for different malware classes using a limited number of microarchitectural events equal to the available number of HPCs that can be captured at run-time. We propose a two-stage machine learning-based hardware-assisted malware detection approach, referred as 2SMaRT, to not only effectively distinguish the malware from benign applications, but also to identify the class of malware at run-time using proper low-level features and determine right machine learning model for capturing the malware behavior.

# 1.3 Stealthy Malware Detection using Microarchitectural Features

Alongside with the advancement in the hardware-based malware detection techniques, malicious software attacks have continued to evolve in quantity and sophistication during the past decade. Due to increasing complexity of malware attacks and financial motivations of attackers, malware trends are recently shifting towards a more dangerous attacks namely as *stealthy* attacks [33,34]. Stealthy attack is a type of cybersecurity attack in which the malicious code is hidden inside the benign application for performing harmful purposes.

The main purpose of stealthy attacks is to remain undetected for a longer period of time in the computing system. The longer the threat remains undiscovered the more opportunity it has to compromise computers and/or steal information before suitable detection mechanism can be deployed to protect against it. Stolfo et al. discovered a new type of stealthy threat referred as *embedded malware* [33]. Under this threat, the attacker embeds the malicious code or file inside a benign file on the target host such that the benign and malicious applications are executed as a single thread on the target system. It has been shown that traditional signature-based antivirus applications are unable to detect embedded malware even when the exact signature of malware is available in the detector database. Embedded malware is potentially a serious security threat and accurate anomaly detection techniques must be developed to mitigate it.

The existing studies on hardware-based malware detection have primarily assumed that the malware is spawned as a separate thread while executing on the target host. However, in real-world scenarios malicious programs attempt to hide themselves within a benign application to bypass the detection mechanisms. Embedded malware

is a category of stealthy security threats that allows malicious code to be hidden inside a benign application on the target host [35].

In response to the aforementioned challenges, in this research, we propose an effective time series machine learning-based approach, referred as *CHASE*, to accurately detect the embedded malicious patterns inside the benign programs using only one HPC feature (branch instruction). The main objective of this work is to accurately detect the malicious application embedded inside the benign program using least number of microarchitectural events (only one HPCs) in which the traditional ML-based solutions are unable to detect them with even 8/16 features. Using an effective feature reduction technique, we first identify the most prominent low-level feature for embedded malware detection. Next, we propose a lightweight scalable time series-based Fully Convolutional Neural Network (FCN) model that automatically identifies potentially contaminated samples in HPC-based time series to distinguish the stealthy malware at run-time using only branch instructions as the most significant HPC event.

# 1.4 Machine Learning-Based Approaches for EnergyEfficiency Prediction in Heterogeneous Architectures

In this section, we examine the suitability of applying effective machine learning techniques on captured run-time low-level information for addressing the performance vs. power consumption trade-offs and enhancing the energy-efficiency of heterogeneous multicore architectures. In particular, we show that hardware performance counter information can be also effectively used for energy-efficiency prediction and scheduling of multithreaded applications running on multicore heterogeneous architectures.

Heterogeneous Multicore Processors (HMPs) are primarily comprised of multiple core types (small vs. big core architectures) with various performance and power characteristics which offer the flexibility to assign each thread to a core that provides the maximum energy-efficiency. Although this architecture provides more flexibility for the running application to determine the optimal run-time settings that maximize energy-efficiency, due to the interdependence of various tuning parameters such as the type of core, run-time voltage and frequency, and the number of threads, the scheduling becomes more challenging. More importantly, the impact of Power Conversion Efficiency (PCE) of the On-Chip Voltage Regulators (OCVRs) is another important parameter that makes it more challenging to schedule multithreaded applications on HMPs [36–38].

In this research, first we investigate the scheduling challenges of multithreaded applications on dynamic heterogeneous architectures. To this aim, we describe a systematic machine learning-based approach to predict the right configurations for running multithreaded workloads on the composite cores architecture. It achieves this by developing a machine learning-based approach to predict core type, voltage and frequency to maximize the energy-efficiency. Our predictor learns offline from an extensive set of training multithreaded workloads. It is then applied to predict the optimal processor configuration at run-time by considering of the multithreaded applications characteristics and the optimization objective.

For this purpose, five well-known machine learning models are implemented for energy-efficiency optimization and precisely compared in terms of accuracy and hardware overhead to guide the scheduling decisions. The results show that while complex machine learning models such as MultiLayerPerceptron are achieving higher accuracy, after evaluating their implementation overheads, they perform worst in terms of power, accuracy/area and latency as compared to simpler but slightly less accurate

regression-based and tree-based classifiers.

Secondly, the importance of concurrent optimization and fine-tuning of the circuit and architectural parameters for energy-efficient scheduling on HMPs is addressed to harness the power of heterogeneity. In addition, the scheduling challenges for multithreaded applications are investigated for HMP architectures that account for the impact of power conversion efficiency. To this aim, a highly accurate learning-based model is developed for energy-efficiency prediction to guide the scheduling decision. Using the predictive model, we further develop a PCE-aware scheduling scheme for effective mapping of multithreaded applications onto an HMP.

### Chapter 2: Background and Related Work

In this section, we comprehensively explore the background and state-of-the-art works on hardware performance counter and machine learning-based solutions for enhancing the security and energy-efficiency of the modern computer computer systems.

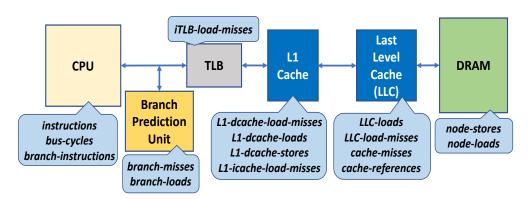

## 2.1 Hardware Performance Counter Registers

Hardware Performance Counters (HPCs) are special purpose registers available in modern microprocessors which keep track of different microarchitectural events [1,2,9]. A variety of todays processor platforms such as Intel, ARM, and AMD include HPC built-in registers on their processors. The main purpose of HPCs is to analyze and tune architectural level performance of running applications [36,37,39–41]. HPC registers are easily programmable across all platforms capable enough to keep track various number of microarchitectural features such as cache memories access misses, TLB hits misses, branch mispredictions, and core stalls of the chip [10,42,43].

The performance counters are often programmed to indicate an interrupt when a counter overflows or even be set to start the counter from the desired value [44, 45]. The software handles these interrupts allowing programmers to analyze the hardware resource utilization by their applications at run-time. While hardware performance counters are finding their ways in various processor platforms from high-performance to embedded, they are limited in the number of microarchitectural events that can be captured simultaneously [1, 2, 13, 22, 29]. This is mainly due to limited number of physical registers on the processor chip which are expensive to implement.

Recently, application areas of HPC are grown from mere performance analysis to detecting firmware modification in Embedded Systems [23, 46], estimating computer system performance, power and energy-efficiency [36–39, 42, 45, 47–51], and even detection of malware [1, 2, 8, 10, 20, 27, 29, 31, 52]. The operating systems can program the HPCs using control registers, called Performance Monitoring Counters (PMCs) found in the Performance Monitoring Unit (PMU). These registers are known as Model Specific Registers (MSRs) on Intel processors. User-space applications can access the HPCs through software interfaces to PMUs and configure the HPCs using the PMCs.

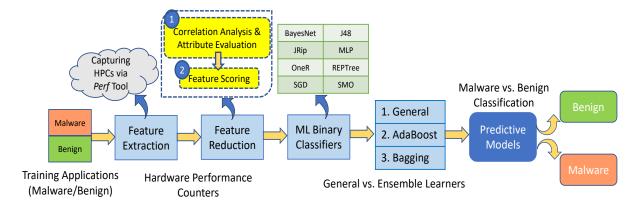

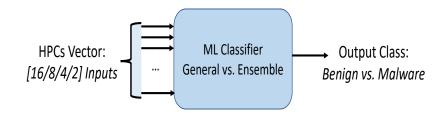

In this research, in order to improve the security of processors, we use HPCs information to construct a vector of microarchitectural events by profiling malware and benign applications and feed the vector into various machine learning classifiers to detect the behavior of application. We utilize the HPC registers to collect execution traces for all available microarchitectural events by executing collected malware and benign applications in an isolated environment. Our goal is to learn malware behavior with collected HPC of various applications (including malware and normal) using supervised machine learning methods. Detailed performance counters collection procedure is discussed in the next sections.

# 2.2 Machine Learning Techniques used for Malware Detection

Methods of machine learning, which build predictive models that generalize training data, have proven to be useful for detecting malware. In this work, we propose effective machine learning-based solutions for improving the security of computer systems in the context of hardware-supported malware detection which rely on the run-time

traces collected from HPCs. Demme et al. [20] showed the offline machine learning effectiveness in classifying malware by learning from hardware performance counter events. They indicated a high detection accuracy result for Android malware by applying complex ML algorithms like Artificial Neural Network (ANN). Although they discussed implementing classifiers on hardware, they did not present any hardware overhead results.

Supervised learning, in the context of machine learning, is a type of system in which both input and desired output data are provided. Input and output data are labeled for classification to provide a learning basis for inferring the data [13]. The majority of practical machine learning uses supervised learning. Supervised learning is basically applications in which the training data comprises examples of the input vectors along with their corresponding target vectors. It is where we have input variables and an output variable and an algorithm is used to learn the mapping function from the input to the output. The goal is to approximate the mapping function appropriately that when we have new input data, the output variables can be estimated promptly for that data.

In this work, we have deployed various supervised machine learning classifiers for malware detection. These machine learning classifiers consist of eight general classifiers including Bayesian Network (BayesNet), an artificial neural network model (MLP: MultiLayerPerceptron), two different rule-based algorithms (JRIP, OneR), a tree-based learning technique namely J48 and REPTree, a Support Vector Machine called SMO, and a Gradient Decent Optimization technique called SGD. We selected these eleven classifiers for two primary reasons. First, they are from different branches of machine learning methods; Bayesian network, neural network, decision tree, and rule-based covering a diverse range of learning algorithms which are inclusive to model both linear and non-linear problems. Second, the prediction model produced by these

learning algorithms is a binary classification model which is compatible with our malware analysis and detection problem. We precisely compared and characterized these ML classifiers in terms of detection performance (accuracy and area under the curve), and hardware overhead. A brief description of each ML classifiers used in this research is presented below:

Bayesian Network (BN): A class of probabilistic and statistic graphical model that that aims to model conditional dependence and causation, by representing a set of variables and conditional dependencies by edges in a directed graph.

Artificial Neural Network (ANN): Consists of units (neurons), arranged in layers, which convert an input vector into some output. Each unit takes an input, applies a (often nonlinear) function to it and then passes the output on to the next layer. The original goal of the ANN approach was to solve problems in the same way that a human brain would [14,48].

Decision Tree (DT): Sequential models, known as "divide and conquer" algorithms, which logically combine a sequence of simple tests where a numerical attribute is compared against a threshold value or against a set of possible values. It is essentially a flow chart like structure where each internal node denotes a test on an attribute with each branch representing an outcome of the test and each leaf holding a class label [14,48].

Rule-Based Classification: Machine learning models that identify, learn, and evolve a set of relational rules that collectively represent the knowledge captured by the system.

Support Vector Machine (SVM): In machine learning domain, a Support Vector Machine (SVM) is a subset of supervised learning models which are discriminative classifiers formally defined by a separating hyperplane that examine the data used for classification and regression analysis. In other words, given labeled training data, the

algorithm outputs an optimal hyperplane which categorizes new examples. In two dimentional space this hyperplane is a line dividing a plane in two parts where in each class lay in either side. SVMs can be efficiently deployed for both linear classification a non-linear classification. In addition, Stochastic Gradient Descent (SGD) is a simple yet very efficient approach to discriminative learning of linear classifiers under convex loss functions such as (linear) Support Vector Machines and Logistic Regression.

Recently, SGD has received a significant consideration by the researchers in the context of large-scale learning. SGD has been successfully applied to large-scale and sparse machine learning problems often encountered in text classification and natural language processing. The advantages of Stochastic Gradient Descent are efficiency and ease of implementation, while it has disadvantages including being sensitive to feature scaling and also requiring a number of hyperparameters such as the regularization parameter and the number of iterations.

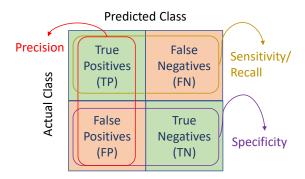

#### 2.2.1 Performance Evaluation Metrics

Evaluating the performance of machine learning classifiers is an important step in implementing effective ML-based optimization solutions for security and energy-efficiency analysis (e.g. malware detection techniques). In the field of machine learning and statistics, there exists variety of measures that can be deployed to evaluate the performance of a ML-based detection method in order to show its detection accuracy. The standard evaluation metrics used for performance analysis of malware detection and classification are summarized in Table 2.1. In this section, we briefly describe each evaluation metric.

In malware detection rate analysis, malicious applications samples are often considered as positive instances. As a result, the True Positive Rate (TPR) metric or

the hit rate, represents sensitivity that stands for the proportion of correctly identified positives. It is basically the rate of malware samples (i.e., positive instances) correctly classified by the classification model. The True Negative Rate (TNR) also represents specificity that measures the proportion of correctly identified negatives. In addition, the False Positive Rate (FPR) is the rate of benign files (i.e., negative instances) wrongly classified (i.e., misclassified as malware samples) [1,2].

The F measure (F score) in machine learning is interpreted as a weighted average of the precision (p) and recall (r). The precision is the proportion of the sum of true positives versus the sum of positive instances and the recall is the proportion of instances that are predicted positive of all the instances that are positive. F measure is a more comprehensive evaluation metric over accuracy (percentage of correctly classified samples) since it takes both the precision and the recall into consideration. More importantly, F measure is also resilient to class imbalance in the dataset which is the case in our experiments. The Detection Accuracy (ACC) measures the rate of the correctly classified positive and negative samples [1, 2, 10, 13].

Precision and recall are not adequate for showing the performance of detection even contradictory to each other, because they do not include all the results and samples in their formula. F-score (i.e., F-measure) is then calculated based on precision and recall in order to compensate this disadvantage. Receiver Operating Characteristic (ROC) is a statistical plot that depicts a binary detection performance while its discrimination threshold setting is changeable. The ROC space is evaluated by considering FPR and TPR as x and y axes, respectively. It primarily assists in determining trade-offs between TP and FP. Since TPR and FPR are equivalent to sensitivity and (1-specificity) respectively, each prediction result represents one point in the ROC space. The point in the upper left corner or coordinate (0, 1) of the ROC curve stands for the best detection result, representing 100% sensitivity and 100%

Table (2.1) Evaluation metrics for performance of malware detection techniques

| Evaluation Metric                        | Description                                                            |

|------------------------------------------|------------------------------------------------------------------------|

| True Positive                            | Correct positive prediction                                            |

| False Positive                           | Incorrect positive prediction                                          |

| True Negative                            | Correct negative prediction                                            |

| False Negative                           | Incorrect negative prediction                                          |

| Specificity: True Negative Rate (TNR) $$ | TNR = TN/(TN + FP)                                                     |

| False Positive Rate (FPR)                | FPR = FP/(FP + TN)                                                     |

| Precision                                | P = TP/(FP + TN)                                                       |

| Recall: True Positive Rate (TPR)         | TPR = TP/(TP + FN)                                                     |

| F measure (F score)                      | $Fmeasure = 2 \times (Precision \times Recall) / (Precision + Recall)$ |

| Detection Accuracy                       | ACC = (TP + TN)/(TP + FP + TN + FN)                                    |

| Error Rate                               | ERR = (FP + FN)/(P + N)                                                |

| Area Under the Curve (AUC)               | $AUC = \int_0^1 TPR(x)dx = \int_0^1 P(A > \tau(x))dx$                  |

specificity. An Area Under the Curve (AUC) is usually between 0.5-1.0, the bigger, the better the detection is [1,13]. Due to the fact that it is difficult to concurrently meet with high precision and recall, we need to make a trade-off to balance both metrics. As a result, F-measure is often used to indicate detection performance [2].

Confusion Matrix for ML Classifiers: In statistical machine learning domain, a confusion matrix, is a specific table that represents the prediction performance of a machine learning classifier. It comprised of two dimensions namely as "actual" and "predicted", and identical sets of "classes" in both dimensions. Each row of the confusion matrix represents the instances in a predicted class while each column represents the instances in an actual class (or vice versa).

As shown in 2.1 a confusion matrix is formed from four outcomes produced as a

result of binary classification. A binary classifier predicts all data instances of a test dataset as either positive or negative. This classification (or prediction) produces four outcomes listed as follows:

Figure (2.1) Confusion matrix layout for a machine learning classifier

- True Positive (TP): Correct positive prediction; e.g. malicious applications that are correctly classified as malware

- False Positive (FP): Incorrect positive prediction; e.g. benign applications that are incorrectly classified as malware

- True Negative (TN): Correct negative prediction; e.g. benign applications that are correctly classified as benign

- False Negative (FN): Incorrect negative prediction; e.g. malicious applications that are incorrectly classified as benign

# 2.3 Comprehensive Analysis of State-of-the-Art

#### 2.3.1 Hardware-Based Malware Detection

In this section, we discuss the latest studies on malware detection techniques using low-level hardware features. The work in [20] was the first study that proposed to use HPC data for malware detection and demonstrated the effectiveness of using machine learning models. Although they have discussed implementing classifiers on hardware, they did not present any hardware overhead analysis results which are important as they decide which ML classifier responds in real-time and performs most cost-efficient. The hardware implementation overhead, particularly area and latency are important as they decide which ML classifier responds in real-time, and performs most cost-efficient. Also, the work has no discussion on main challenges to realize run-time HMD highlighted in this work including limited number of HPCs, and high variance in ML classifiers accuracy and performance across various classes of malware as well as embedded HMD.

The works in [53] and [54] discussed the feasibility of unsupervised learning method on low-level features to detect Return-Oriented Programming (ROP) and buffer over-flow attacks by finding an anomaly in HPCs information. Although unsupervised algorithms can be more effective in detecting new malware and attacker evolution, they are complex in nature requiring more sophisticated analysis, resulting in complex hardware implementations. Also, their software implementation is not an effective solution to detect malware at run-time, due to large latency to compute the complex algorithms.

In [21,55], the authors used sub-semantic features to detect malware. Moreover, they suggested changes in microprocessor pipeline to detect malware in truly real-time nature. They discussed estimated latency and area utilization of Logistic and

ANN algorithm implementation for their architecture. However, our work is different as it does not require any change in the processor pipeline. In [29], a single-stage ML-based hardware-assisted malware detection is proposed, but requires 8 or more HPC features to achieve higher accuracy and performance, which makes it less suitable for online malware detection. The work in [31] collected HPC information to construct support vector machine (SVM) detectors to identify malicious programs. However, they did not discuss the per-class analysis as well as hardware overhead analysis of deployed ML classifiers.

The works in [30] used logistic regression to classify malware into different types and trained a specialized classifier for detecting each type. They further used ensemble learning to improve the accuracy of logistic regression. In their ensemble learning implementation, they limited their experiments on just combining classifiers. In addition, they have ignored to account for the impact of reducing the number of HPCs on the performance of detectors and also have examined limited ML classifiers.

Collectively, prior works on hardware-assisted malware detection mostly focus on a particular machine learning classifier and ignoring per-class analysis of malware. Our work is different, given that for each class of malware, a unique ML classifier gives the best results (across detection rate, performance, delay, and area metrics), we thoroughly examined various general and ensemble learning-based malware detectors using varying number of microarchitectural features in terms of detection rate, robustness, performance, and hardware overheads for effective run-time harwdare-based mawlare detection [1].

#### 2.3.2 Energy-Efficient Heterogeneous Architectures

Heterogeneous Architectures. Heterogeneous multicore architectures refers to computer systems that include more than one type of processors. Such systems gain

performance or energy efficiency not just by adding the same type of processors, but by adding dissimilar coprocessors, usually incorporating specialized processing capabilities to handle particular tasks [56–58]. The static heterogeneous architecture in [59] enables efficient thread-to-core mapping and permits a change in the mapping across phases of execution through thread migration. Prior research has shown that the potential benefit of a static heterogeneous architecture is greater with fine-grained thread migration than with coarse-grain migration [60].

In research [61], an Intel Xeon is integrated with an Atom processor. Code instrumentation is used at the function or loop level to schedule different phases of the application on each processor. However, the separate core and memory subsystems in static heterogeneous architectures incur power and performance overheads for application migration, which makes dynamic mapping ineffective for fine-grained migration.

Unlike static heterogeneous architecture where the number and type of cores are fixed at run-time, dynamic heterogeneous architectures can be configured at run-time [62]. This provides more opportunity to map an application to a core which matches its resource needs more closely. Some of the first efforts to provide this kind of heterogeneity include Core Fusion [63] and TFlex [60]. Composite cores proposed a dynamic heterogeneous architecture where a big core can dynamically be decomposed into a smaller core [64].

The work in [62] and [65] extended the concept of composite cores into 3D stacking which enables fine-grain sharing of resources between cores on a stacked chip multiprocessor architecture. Their proposed architecture permits multiple smaller cores to be composed together making a larger core, given the performance and energy requirements of the running application. Previous work on dynamic heterogeneous architecture and specifically on composite core, has mainly studied mapping of single

threaded applications. However, our work is different as it mainly focuses on multithreaded applications and how they would benefit from such architecture to maximize the energy-efficiency.

Scheduling Challenges in Heterogeneous Architectures. As mentioned before, a main challenge for heterogeneous architectures is the mapping and scheduling decision, which finds the most efficient application-to-core match at run-time. The work in [59] and [66] address the problem of dynamic thread mapping in static heterogeneous many-core systems. Prior research aimed to maximize performance under power constraints [56, 59, 66, 67]. Our work is different as it first targets dynamic heterogeneous architectures where core size can be adapted at run-time, and second it aims to maximize the energy-efficiency by reducing the EDP. It is important to note that the power and performance of an application on different cores at various frequencies must be known for proper mapping. Traditional designs suggest selecting the best core based on a small sampling of applications on each core [68]. Other techniques [56,64,67,69], estimate core performance and adapt the resources without running applications on a particular core type using learning models.

The work in [70] and [64] provide a model for performance estimation on two core types (i.e., big and little cores). The complexity of application mapping on a heterogeneous architecture increases exponentially by increasing number of core types and applications. While previous studies have mainly examined the advantages of using single threaded applications, there is limited study on effectively mapping multithreaded applications onto heterogeneous composite cores architecture. There have been several studies on mapping multithreaded applications on homogeneous architectures.

The work in [71] suggested a framework called Thread Reinforcer to determine the appropriate number of threads for a multithreaded application on a homogeneous architecture. It examines the mapping between number of threads and number of cores to find the optimal or near optimal number of threads to minimize the execution time.

The research in [70] proposed a scheduling method to predict application to core mappings that enhances performance. Using profiling parameters, it estimates performance and examines whether the workload needs to run on different core type. The work in [59] proposed a mapping strategy for multithreaded applications on static heterogeneous multicore architecture by initializing a maximum throughput mapping and iteratively performing a thread swap on adjacent types of cores until the power constraint is met.

The work in [56] took a closer look at joint optimization of voltage and frequency as well as the microarchitecture. It proposed a platform, which is capable of scaling resources, i.e., bandwidth, capacity, voltage, and frequency, based on single-threaded application performance requirements at run-time while reducing EDP.

# Chapter 3: Ensemble Learning for Effective Run-Time Hardware-Based Malware Detection

Malware (Malicious Software) is a piece of code designed to perform various malicious activities, such as destroying the data, stealing information, running destructive or intrusive programs on devices to perform Denial-of-Service (DoS) attack, and gaining root access without the consent of user [1,2,8,17]. Malware detection can be simplified as a binary classification problem regardless of what detection method is being used [1,13]. It is basically envisioned as distinguishing whether the running application has malicious intent or not.

Traditional malware detection approaches such as signature-based detection and semantics-based anomaly detection are considered as software-based solutions and incur significant computational overheads [1,2,13,29]. In particular, these software-based malware detection methods such as AV software primarily pose several draw-backs. First, they rely on static signature-based detection in order to detect malicious pattern of infected application. Such detection mechanism search for suspicious byte patterns in the program, whereas an attacker can deceive AV software by programming and crafting malware in such a way that its signature appears as a benign software. Second, AV software are prone to exploits like any other software which can ultimately compromise protection if exploited. Third, AV software tools are slow and resource hungry. Conditions become even worse for metamorphic viruses, as defective detection of such attacks is an NP-complete problem [72].

Recent studies on malware detection approaches have demonstrated that malware behavior can be differentiated from benign applications by classifying anomalies in the low-level microarchitectural features spaces such as microarchitectural events collected by Hardware Performance Counter (HPC) registers[1, 2, 9, 13]. HPCs are CPU hardware registers that count hardware events such as instructions executed, cache-misses suffered, or branches mispredicted.

Performance counters data have been extensively used to predict the power, performance, and energy-efficiency of computing systems [10,36–39], and recently drew attentions to be used for detecting the malicious pattern of running applications to improve the security of systems. Thus, malware detection using HPCs microarchitectural events has emerged as a promising alternative to traditional malware detection methods. As learning the underlying patterns of these microarchitectural events can aid in detecting malware, machine learning techniques are widely deployed for malware detection. The HPC microarchitectural features are used to train ML-based classifiers. In addition, such ML-based malware detection methods can be implemented in microprocessor hardware with significantly low overhead as compared to the software-based methods, as detection of anomaly inside the hardware is very fast (few clock cycles) [1,13].

Recently, there has been a number of work on hardware-based malware detection using HPCs information [20–23,30,31,46,55]. However, these works performed a limited study on malware classification accounting for the availability of a large number (e.g. 16 or 32) and diverse type of HPCs. While, modern processors in the high-performance domain have a small number of HPCs (2 to 8), due to several reasons including the design complexity and cost of concurrent monitoring of microarchitectural events [1,25,26].

Due to deep pipelines, complex prefetchers, branch predictors, modern cache design etc., HPCs implementation becomes a great challenge in terms of counting multiple events and maintaining counter accuracy at the same time under speculative execution [1, 25, 26]. Better accuracy requires better and more complex hardware design hence increasing the number of counters with limited accuracy doesn't appear to be a good trade-off. Even modern Intel Xeon architectures houses only 4-6 performance counters, compare to 2 in Pentium 4 and server class Intel Atom processor, for the very same reason. For embedded mobile and IoT domains, the number of HPCs that can be accessed simultaneously is even smaller.

Therefore, collecting a variety of microarchitectural events, more than the number of available HPCs, to achieve high accuracy using the general ML models presented in prior work, requires running the application multiple times, since the hardware can only count a small subset of events concurrently. This approach is not practical for run-time detection of malware. In addition, previous studies, mostly focus on specific learning classifiers and limited types of malware. A quantitative comparison of these studies indicates that there is no unique classifier that delivers the best results across various metrics including performance (accuracy and robustness) and area overhead as well as detection delay and various classes of malware.

As the performance of malware detection depends on the type of ML classifier applied and the number and type of HPC events used, in this work, we first illustrate the impact of ML classifier type on malware detection accuracy and performance and the effect of number of HPC events for malware detection [1]. To achieve a high accuracy across all studied general ML classifiers, of more than 80%, at least 16 hardware performance counters are required, which as discussed is not available in modern processors, even in the high-performance domain, making run-time detection of malware impractical using these methods. Therefore, a key challenge in making the hardware-based malware detection a practical run-time solution is how to use a limited number of HPCs available in a microprocessor (for instance 2 or 4) and match the accuracy and performance of malware detection with the ones that can be

achieved by a larger number of HPC events (for instance 16 or 32).

In this work, we address this challenge by proposing ensemble learning techniques to improve the accuracy and performance of the hardware-based malware detectors and break the trade-off between accuracy/performance with respect to the number of HPCs. We explore the effectiveness of ensemble learning models in 1) reducing the number of required performance counters for implementing effective ML classifiers for run-time malware detection and 2) improving the performance of weak but low-cost classifiers in malware detection with a small number of HPCs.

This work proposes a machine learning-based solution to break this trade-off to realize effective run-time detection of malware. We propose ensemble learning techniques to improve the performance of the hardware-based malware detectors despite using a very small number of microarchitectural events that are captured at run-time by existing HPCs, eliminating the need to run an application several times. For this purpose, eight robust machine learning models and two well-known ensemble learning classifiers applied on all studied ML models (sixteen in total) are implemented for malware detection and precisely compared and characterized in terms of detection accuracy, robustness, performance (accuracyrobustness), and hardware overheads. The experimental results show that the proposed ensemble learning-based malware detection with just 2 HPCs using ensemble technique outperforms standard classifiers with 8 HPCs by up to 17%. In addition, it can match the robustness and performance of standard ML-based detectors with 16 HPCs while using only 4 HPCs allowing effective run-time detection of malware.

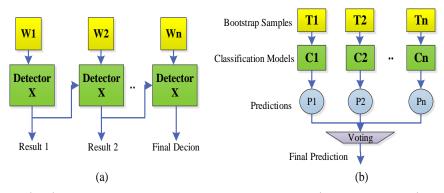

# 3.1 Ensemble Learning

Ensemble learning is a branch of machine learning which is used to improve the accuracy and performance of general ML classifiers by generating a set of base learners and combining their outputs for final decision [1, 2, 13, 73]. It fully exploits complementary information of different classifiers to improve the decision accuracy and performance. The ensemble learning and joint decision procedure are widely used to devise learning methods to achieve more accurate predictions and stronger generalization performance. In this work, we deploy and analyze the effectiveness of two ensemble learning methods for efficient malware detection even with less number of HPCs. These ensemble methods are briefly described in below:

Figure (3.1) Ensemble learning block diagrams a) AdaBoost, b) Bagging

## 3.1.1 Boosting

Boosting is one of the most commonly used ensemble learning methods for enhancing the performance of ML algorithms. Adaptive Boosting, or in short AdaBoost [74], is the first proposed implementation of this type of ensemble learners. Figure 3.1-a illustrates the AdaBoost methodology. As shown, each base classifier is trained on a

weighted form of the training dataset in which the weights depend on the performance of the previous base ML classifier.

Once all the base classifiers are trained, they will be combined to produce the final classifier. Each training instance in the dataset is weighted and the weights are updated based on the overall accuracy of the model and whether an instance was classified correctly or not. Subsequent models are trained and added until a minimum accuracy is achieved or no further improvement is possible. In this work, we applied AdaBoost as a boosting learning technique on all studied general ML classifiers to analyze its impact on the accuracy and performance improvement of hardware-based malware detection [1,13].

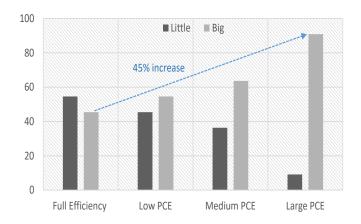

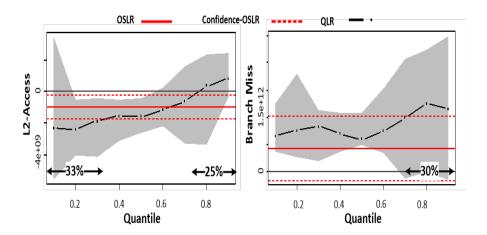

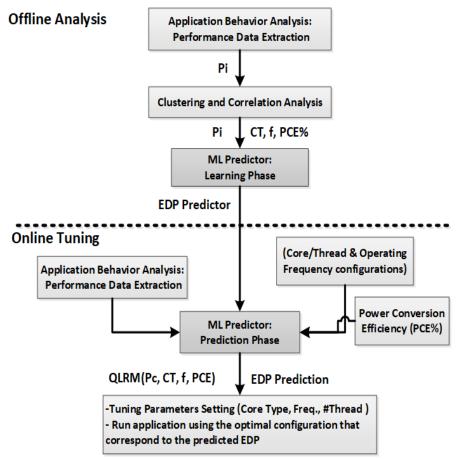

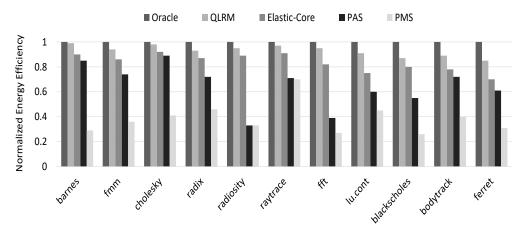

### 3.1.2 Bagging