# $\frac{\text{HARDWARE/SOFTWARE CODESIGN APPROACHES TO PUBLIC KEY}}{\text{CRYPTOSYSTEMS}}$

by

Malik Umar Sharif

A Dissertation

Submitted to the

Graduate Faculty

of

George Mason University

in Partial Fulfillment of

The Requirements for the Degree

of

Doctor of Philosophy Electrical and Computer Engineering

| Committee: |                                                           |

|------------|-----------------------------------------------------------|

|            | Dr. Kris Gaj, Dissertation Director                       |

|            | Dr. Jens Peter Kaps, Committee Member                     |

|            | Dr. Houman Homayoun, Committee Membe                      |

|            | Dr. Robert Simon, Committee Member                        |

|            | Dr. Monson H. Hayes, Department Chair                     |

|            | Dr. Kenneth S. Ball, Dean, Volgenau School of Engineering |

| Date:      | Summer Semester 2017 George Mason University Fairfax VA   |

# Hardware/Software Codesign Approaches to Public Key Cryptosystems

A Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

by

Malik Umar Sharif

Master of Science

George Washington University, 2010

Bachelor of Science

National University of Sciences and Technology, 2001

Director: Kris Gaj, Associate Professor Department of Electrical and Computer Engineering

> Summer Semester 2017 George Mason University Fairfax, VA

Copyright 2017 Malik Umar Sharif All Rights Reserved

# **DEDICATION**

I dedicate this dissertation to my lovely wife, Rabia. It would not have been possible without her consistent support as a partner all these years. To my mother, who has always been there for me whenever I needed guidance and her prayers have always kept me going. I would also like to dedicate this to my father for always believing in me and lastly to my son, Shaheer. He has always brightened my day with his smile and has been the reason for my motivation specially in the past couple of years.

#### **ACKNOWLEDGEMENTS**

I would specially like to acknowledge and express my sincere gratitude towards my advisor Dr. Kris Gaj for his consistent guidance, knowledge and mentorship during my Ph.D study and research. It has always been a pleasure working under his supervision. His attention to detail and thorough knowledge has helped me immensely to accomplish the research work I have worked on.

I would also like to thank Dr. Kaps for always giving great feedback whenever I asked for any guidance. He has always been open to new ideas and insight related to any challenges I faced during my Ph.D.

I would also like to thank my other committee members, Dr. Houman Homayoun and Dr. Simon for their valuable comments regarding my thesis study.

I would also extend my gratitude to all fellow present and former Cryptographic Engineering Research Group (CERG) members for all the discussions, meetings and valuable feedback they offered throughout these years.

And in the end, a special thanks to all my family members, my parents, my sister, and my wife Rabia for always being there for me whenever I needed them the most.

# TABLE OF CONTENTS

| LIST OF TA | ABLES                                                            | Page |

|------------|------------------------------------------------------------------|------|

|            |                                                                  |      |

|            | GURES                                                            |      |

| ABSTRAC    | Γ                                                                | xi   |

| 1 INTRO    | DUCTION                                                          | 1    |

| 1.1 Tı     | aditional and Post-Quantum Public Key Cryptography               | 1    |

| 1.2 M      | otivation and Research Goals                                     | 6    |

| 1.2.1      | Post-Quantum Cryptosystems (PQC)                                 | 7    |

| 1.2.2      | Hardware/ Software Codesign                                      | 8    |

| 1.2.3      | Zynq All Programmable System on Chip                             | 8    |

| 1.2.4      | Research Questions & Challenges                                  | 10   |

| 2 BACK     | GROUND                                                           | 11   |

| 2.1 C      | yptographic Algorithms                                           | 11   |

| 2.1.1      | RSA                                                              | 11   |

| 2.1.2      | Lattice-Based Cryptosystems                                      | 15   |

| 2.1.3      | NTRUEncrypt Cryptosystem                                         | 18   |

| 2.2 Te     | echnology                                                        | 20   |

| 2.2.1      | Hardware/Software Codesign Platforms                             | 20   |

| 2.2.2      | Hardware/Software Codesign with Xilinx Zynq SoC                  | 23   |

| 2.2.3      | Type of AXI Interfaces in Zynq SoC                               | 29   |

| 2.2.4      | AXI DMA                                                          | 32   |

| 2.2.5      | Embedded FPGA Resources                                          | 32   |

| 3 SURV     | EY OF PREVIOUS WORK                                              | 36   |

| 3.1 H      | W/ SW Codesign Implementations of RSA                            | 36   |

| 3.2 Pr     | evious HW/ SW Codesign Implementations on Traditional Public-Key |      |

|            | phy                                                              |      |

| 3.3 Pr     | evious Implementations of Lattice Based Cryptosystems            |      |

| 3.3.1      | Previous Implementations of NTRU Cryptosystem                    | 43   |

| 3.3.2      | Previous Implementations on Modular Multiplier Designs           | 45   |

| 4 HARD     | WARE/SOFTWARE CODESIGN OF RSA                                    | 47   |

| 4.1 So     | oftware Development                                              |      |

| 4.1.1      | Developing and Extending Software APIs in RELIC Library          | 47   |

| 4.1.2      | Hardware/Software Partitioning                                   | 48   |

|   | 4.2   | Operation of the Processing System                                      | 49     |

|---|-------|-------------------------------------------------------------------------|--------|

|   | 4.3   | Choice of Communication Interface                                       | 53     |

|   | 4.4   | Implementing Programmable Logic (PL) – Our Hardware Accelerator         | 54     |

|   | 4.5   | Results and Comparison                                                  | 58     |

|   | 4.6   | Conclusion                                                              | 63     |

| 5 | CUS   | STOM HARDWARE IMPLEMENTATION OF NTRUEncrypt                             | 64     |

|   | 5.1   | Preliminaries                                                           | 64     |

|   | 5.2   | NTRUEncrypt SVES                                                        | 65     |

|   | 5.3   | Hardware Design                                                         | 69     |

|   | 5.3.  | 1 Hardware API & Interface of NTRU core                                 | 71     |

|   | 5.3.2 | 2 Top-Level Block Diagram                                               | 72     |

|   | 5.3.  | 3 Diagrams of Selected Lower-Level Components                           | 76     |

|   | 5.4   | Results                                                                 | 79     |

|   | 5.5   | Conclusions                                                             | 85     |

| 6 | Hard  | dware/ Software Codesign of NTRUEncrypt                                 | 87     |

|   | 6.1   | Methodology                                                             | 87     |

|   | 6.2   | Software Profiling                                                      | 88     |

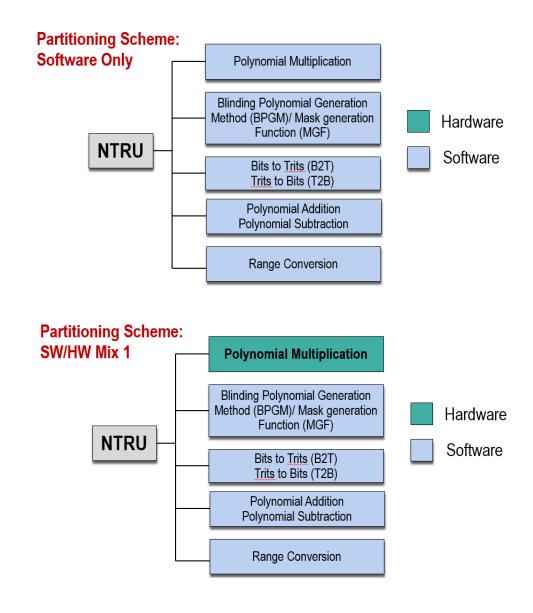

|   | 6.3   | Proposed Partitioning Schemes:                                          | 88     |

|   | 6.4   | Four popssible partitioning schemes NTRUEncrypt bewteen software and ha | rdware |

|   | 6.5   | Optimizing the Polynomial Multiplier                                    | 91     |

|   | 6.6   | Conclusion                                                              | 100    |

|   | 6.7   | Future Work                                                             | 100    |

| 7 | COl   | NCLUSIONS & FUTURE WORK                                                 | 101    |

|   | 7.1   | Possibilities for Future Work                                           | 103    |

| A | . PUE | BLICATIONS                                                              | 105    |

# LIST OF TABLES

| Table                                                                                       | Page    |

|---------------------------------------------------------------------------------------------|---------|

| Table 1. Short History of Quantum Computing                                                 | 3       |

| Table 2. Comparison with Alternative Solutions (Source: Xilinx Video Tut                    |         |

| Table 3 The Underlying Security Problem and the Best Known Algorithms                       | for     |

| Solving this Problem                                                                        |         |

| Table 4 Major Algorithms of Lattice-based cryptosystems and their Publica  Dates            |         |

| Table 5. Public Key Sizes for Lattice-based algorithms for selected Security                |         |

| LevelsLevels                                                                                | _       |

| Table 6. Communication Interface Options in Zync SoC                                        |         |

| Table 7. HW/ SW Codesign Implementations of RSA                                             |         |

| Table 8. HW/ SW Codesign Implementations of ECC for 80-bit security                         |         |

| Table 9. Selected Hardware Implementations of NTRU                                          |         |

| Table 10. Implemented hardware functions                                                    |         |

| Table 11. Comparison of our HW/SW Implementation with software                              | 50      |

| implementation based on RELIC for four operand sizes and three                              |         |

| exponentiation schemes. Note: CC <sub>pre</sub> – Clock cucles for preprocessing            | r       |

| CC <sub>post</sub> – Clock cycles for postprocessing, CC <sub>proc</sub> – Clock cycles for | • •     |

| processing, $CC_{sw}$ – Clock cycles for software, $CC_{hw/sw}$ – Clock cycles              | for     |

| HW/SW codesign                                                                              |         |

| Table 12. Comparison of our work with existing designs of modular                           |         |

| exponentiation ME from literature. Note: * - the execution time was                         |         |

| determined for the ME scheme and operand size marked by this symbol                         | ol.     |

| SLID – Sliding Window Method, MPL – Montgomer Powering Ladde                                |         |

| BFL – Blinded Fault Resistant Exponentiation                                                |         |

| Table 13. Basic operations of Encryption and Decryption                                     |         |

| Table 14. Inputs, Outputs, and Intermediate Variables                                       |         |

| Table 15. Parameters of the algorithm, architecture, and input affecting the                |         |

| execution time, for two parameter sets ees1499ep1 and ees1087ep1                            |         |

| Table 16. Auxiliary components used in the top-level block diagram and th                   |         |

| diagrams of lower-level components.                                                         |         |

| Table 17. Resource utilization and performance metrics of major component                   | nt      |

| units. Latencies correspond to the ees1499ep1 parameter set                                 | 80      |

| Table 18. Timing analysis of our hardware implementation. Latencies in clo                  | ock     |

| cycles correspond to the maximum sizes of messages allowed by a give                        | en en   |

| parameter set.                                                                              | 81      |

| Table 19. Results of profiling of the software implementation of NTRUEnc                    | rypt    |

| SVES from [9], using the Cortex A9 ARM Core of Zynq 7020, for the                           | •       |

| ees1499ep1parameter set                                                                     | 82      |

| Table 20. Speed up of Hardware (This Work) vs. Software (source code [54]                   | 41) .83 |

| Table 21. Previous Hardware Implementations of NTRU. Notation: E –           |

|------------------------------------------------------------------------------|

| encryption, D – decryption, E/D: Encryption & Decryption84                   |

| Table 22. Comparison of the results for the hardware implementation of Poly  |

| Mult by Liu et al. using Altera Cyclone IV, and this work using Xilinx       |

| Kintex-7                                                                     |

| Table 23. Comparison of Results with and without Pipelining at different     |

| Pipeline Levels96                                                            |

| Table 24. Results of profiling of the software implementation of NTRUEncrypt |

| SVES, using the Cortex A9 ARM Core of Zynq 7020, for the ees401ep1           |

| parameter set97                                                              |

| Table 25. Results of profiling of the HW/SW codesign implementation of       |

| NTRUEncrypt SVES, using the Cortex A9 ARM Core of Zynq 7020, for             |

| the ees401ep1 parameter set98                                                |

| Table 26. Results of profiling of the hardware implementation of NTRUEncrypt |

| SVES, using the Cortex A9 ARM Core of Zynq 7020, for the ees401ep1           |

| parameter set99                                                              |

| Table 27. Timing analysis of our HW/SW codesign implementation. Latencies    |

| in clock cycles correspond to the maximum sizes of messages allowed by a     |

| given parameter set                                                          |

|                                                                              |

# LIST OF FIGURES

| Figure                                                                          | Page |

|---------------------------------------------------------------------------------|------|

| Figure 1. Scope of Research                                                     | 2    |

| Figure 2. Discrete FPGA-Processor Combination                                   | 21   |

| Figure 3. Zync SoC Z7020 platform with interface between PS and PL              | 25   |

| Figure 4. SIPO in Input interface of Coprocessor                                | 26   |

| Figure 5. PISO in Output interface of Coprocessor                               | 26   |

| Figure 6. Processor Ports for Communication between PS and PL                   | 28   |

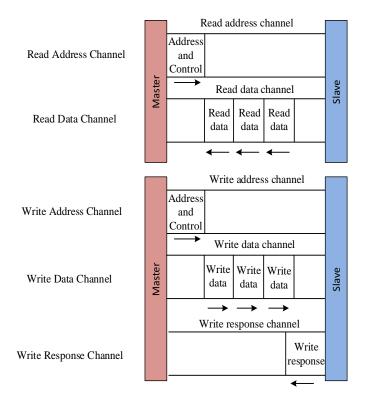

| Figure 7. AXI Interfaces                                                        | 29   |

| Figure 8. AXI-Lite Interface                                                    | 30   |

| Figure 9. AXI Full Interface                                                    | 31   |

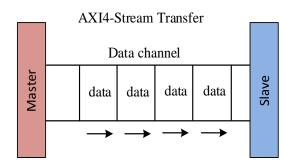

| Figure 10. AXI Stream Interface                                                 | 31   |

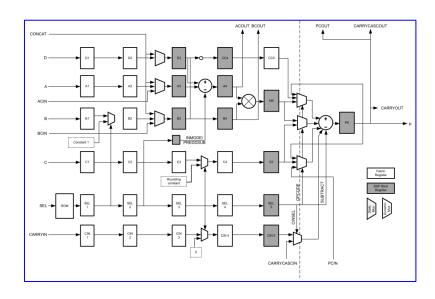

| Figure 11. DSP48 inside Zync SoC Z7020 and Latency selection to operate at 40   | )0   |

| MHz                                                                             | 33   |

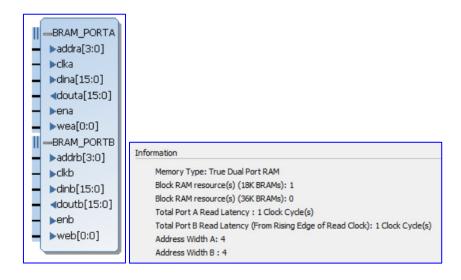

| Figure 12. True Dual Port BRAM to store input data                              | 34   |

| Figure 13. Hierarchy of Operations and Tentative Partitioning Schemes in RSA.   | 48   |

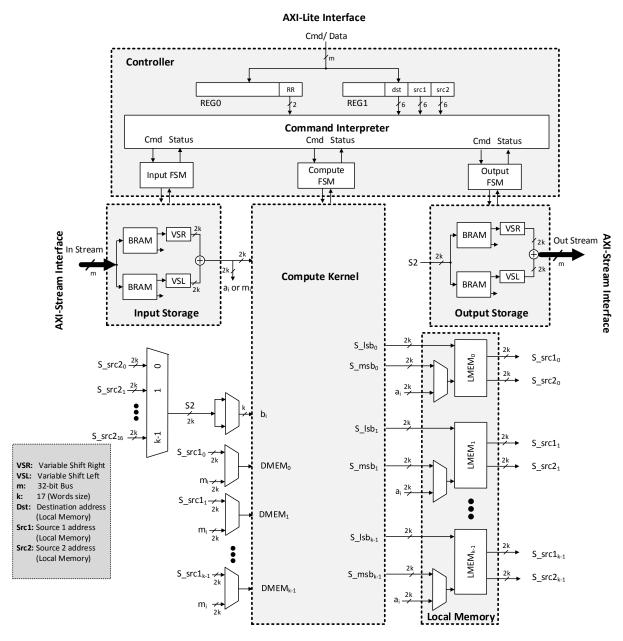

| Figure 14. Detailed Hardware Coprocessor Design                                 | 56   |

| Figure 15. Flow diagram of SVES Encryption (top) and Decryption (bottom)        | 66   |

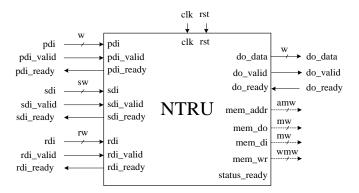

| Figure 16. NTRU Interface compatible with the PQC Hardware API interface [8     | ]71  |

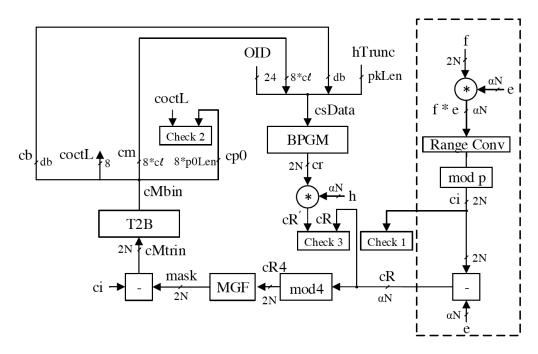

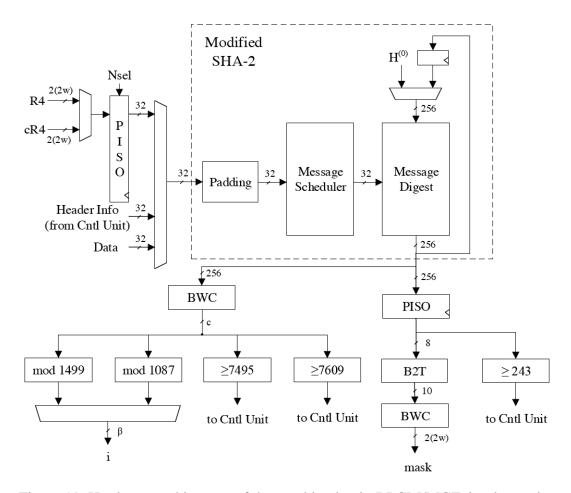

| Figure 17. Top-level block diagram of the developed hardware architecture of S' | VES. |

| N represents max(1499, 1087)=1499                                               | 74   |

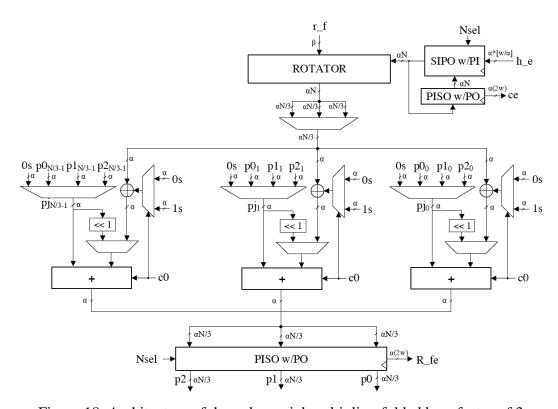

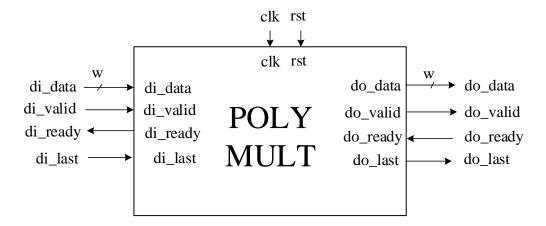

| Figure 18. Architecture of the polynomial multiplier, folded by a factor of 3   | 78   |

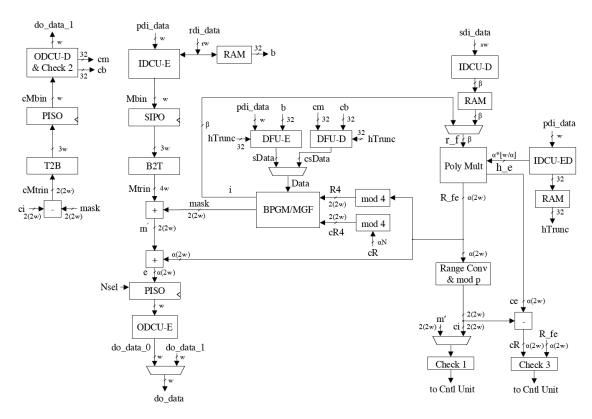

| Figure 19. Hardware architecture of the combined unit, BPGM/MGF, implement      | ting |

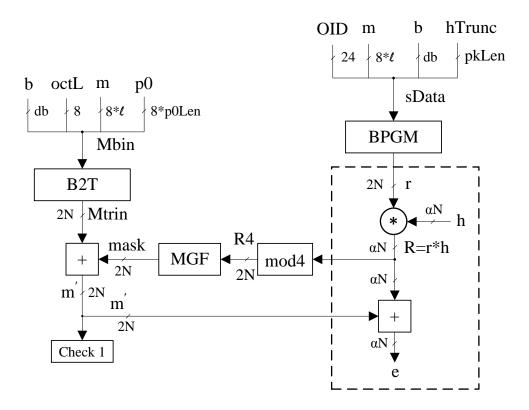

| the Blinding Polynomial Generation Method and Mask Generation Function          | n79  |

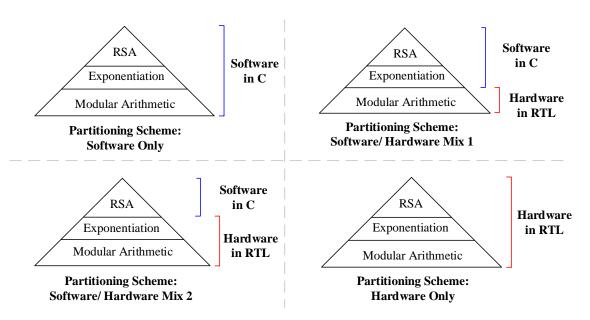

| Figure 20. Partitioning Schemes for HW/SW Codesign of NTRU                      | 89   |

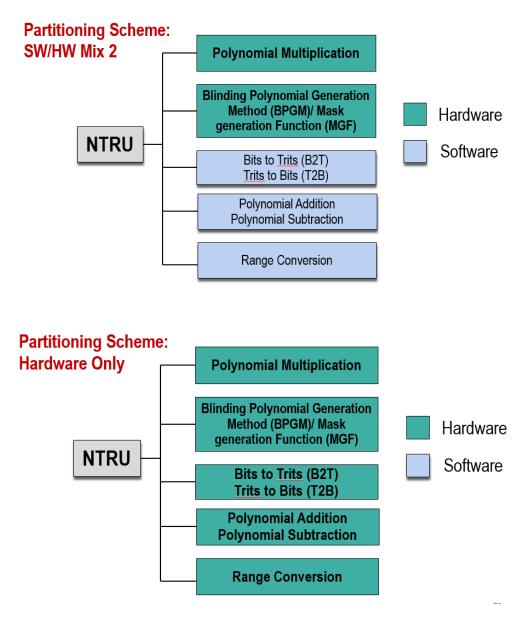

| Figure 21. Interface for Polynomial Multiplier                                  | 90   |

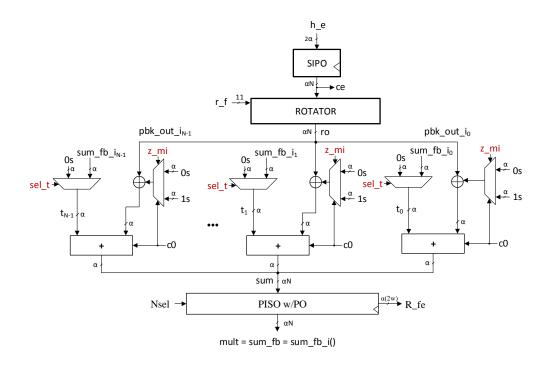

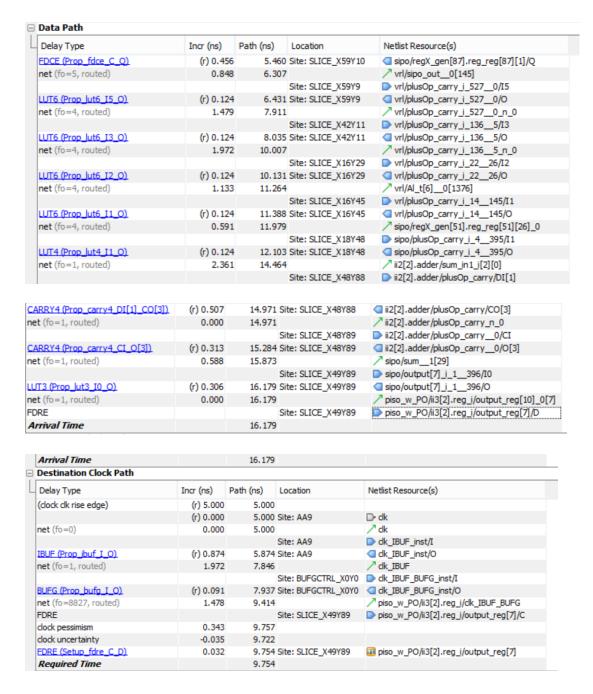

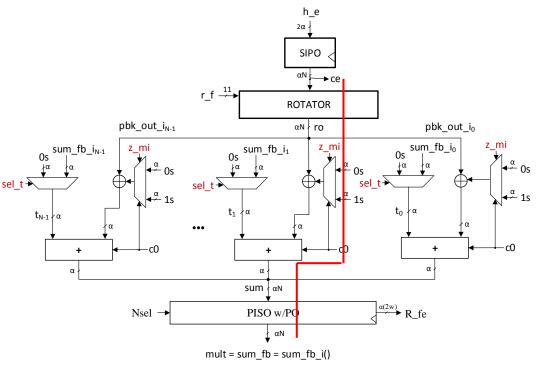

| Figure 22. Polynomial Multiplier – Full Version                                 | 92   |

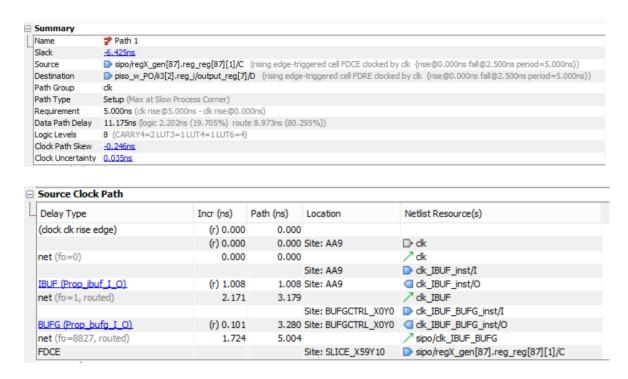

| Figure 23. Critical Path Analysis for Polynomial Multiplier                     | 93   |

| Figure 24. Full version of the multiplier (Critical Path shown in Red)          | 94   |

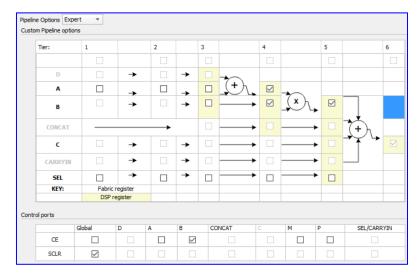

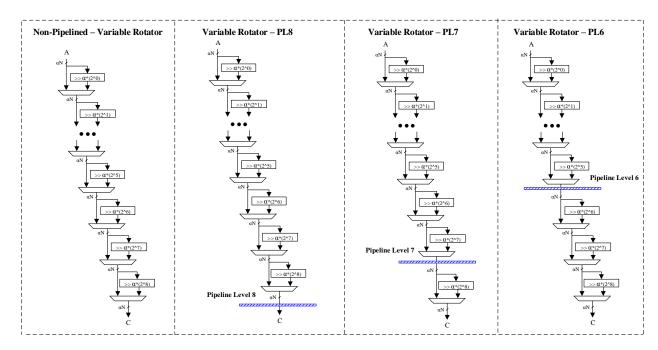

| Figure 25. Diagram for Pipelining at different Pipeline Levels                  | 94   |

| Figure 26. Polynomial Multiplier – Folded Architecture                          | 95   |

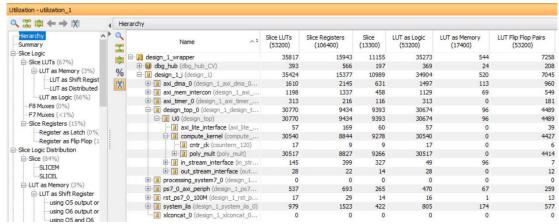

| Figure 27. Reconfigurable Resource Utilization of Zynq SoC for HW/SW Codes      | sign |

| Implementation                                                                  | 97   |

**ABSTRACT**

HARDWARE/SOFTWRE CODESIGN APPROACHES TO PUBLIC KEY

**CRYPTOSYSTEMS**

Malik Umar Sharif, Ph.D.

George Mason University, 2017

Thesis Director: Dr. Kris Gaj

If a quantum computer with a sufficient number of qubits was ever built, it would easily

break all current American federal standards in the area of public-key cryptography,

including algorithms protecting the majority of the Internet traffic, such as RSA,

Elliptic Curve Cryptography (ECC), Digital Signature Algorithm (DSA), and Diffie-

Hellman. As a result, a new set of algorithms, resistant against any known attacks

involving quantum computers, must be developed. These algorithms are collectively

referred to as Post-Quantum Cryptography (PQC). The standardization effort for these

algorithms is likely to last years and result in the entire portfolio of algorithms capable

of replacing current public-key cryptography schemes. As a part of this standardization

process, fair and efficient benchmarking of PQC algorithms in hardware and software

becomes a necessity. Traditionally, software implementations of public-key algorithms

provided the highest flexibility but lacked performance. On the other hand, custom

hardware implementations provided the highest performance but lacked flexibility and

adaptability to changing algorithms, parameters, and key sizes. Therefore, in this work,

we investigate the suitability of the hardware/software codesign for implementing and

evaluating traditional and post-quantum public-key cryptosystems from the point of view of their implementation efficiency.

As our case studies, we considered one traditional public key cryptosystem, RSA, and one post-quantum public key cryptosystem, NTRUEncrypt. We implemented both of them using custom hardware, as well as software/hardware codesign. The Xilinx Zynq-7000 System on Chip platform, which integrates a dual-core ARM Cortex A9 processing system along with Xilinx programmable logic, was used for our experiments. The performance vs. flexibility trade-off has been investigated, and the speed-up of our software/hardware codesign implementations vs. the purely software implementations on the same platform is reported and analyzed. Similarly, the speedup of the custom hardware vs. hardware-software codesign is investigated as well. Additionally, we have determined and analyzed different percentage contributions of the execution times for equivalent component operations executed using the aforementioned three different implementation approaches (custom hardware, software/hardware codesign, software). We demonstrate and pure hardware/software codesign can reliably assist in early evaluation and comparison of various public-key cryptography schemes. Our project is intended to pave the way for the future comprehensive, fair, and efficient benchmarking of the most promising encryption, signature, and key agreement schemes from each of several major postquantum public-key cryptosystem families.

#### 1 INTRODUCTION

In this chapter, we describe the existing traditional and post-quantum public key cryptosystems that are used in the field of cryptography and reported in the literature. We also provide the motivation behind working on post-quantum public key cryptosystems and the reason why cryptographic community should focus its attention on preparing for the next generation of quantum resistant algorithms. We also emphasize on the importance of choosing the hardware/software codesign platform in an effort to evaluate and benchmark these algorithms and reasons to choose Xilinx system on chip solution to implement the designs and analyze the results.

# 1.1 Traditional and Post-Quantum Public Key Cryptography

The idea of Public-Key Cryptography (PKC) was proposed by Diffie and Hellman in 1976 [1]. Later during the next year Ron Rivest, Adi Shamir and Leonard Addleman [2] proposed another public-key cryptosystem known as RSA which enabled encryption of a message using public key of the receiver. Only the receiver could decrypt the message with its private key which is kept as a secret.

Public-key cryptosystems simplified the issue of key management. As they require intense mathematical calculations based on integer factorization and discrete logarithms, the implementations were much slower than symmetric key algorithms for encryption. As a result, secret-key cryptography kept on being in use for bulk encryption, while public-key cryptosystems were used for key management. With the advancements in the computing power of modern computers and due to efficient algorithms for integer factorization, the increasing size of RSA modulus caused the implementations to become slower due to large key sizes.

Another branch of traditional public-key cryptography (PKC) is Curve-based cryptography (e.g. ECC). It provides the same level of security as RSA with considerably shorter operands. In many cases, ECC has performance advantages (fewer computations) and bandwidth advantages (shorter signatures and keys) over RSA. However, ECC is still considered as a computational intensive application due to the complexity of scalar or point multiplications. A steady progress has been made since mid-1980s, when the concept of quantum computing was born. From the point of view of cryptography, the most important discovery was made in 1994, when Peter Shor developed his famous quantum algorithm for factoring [3].

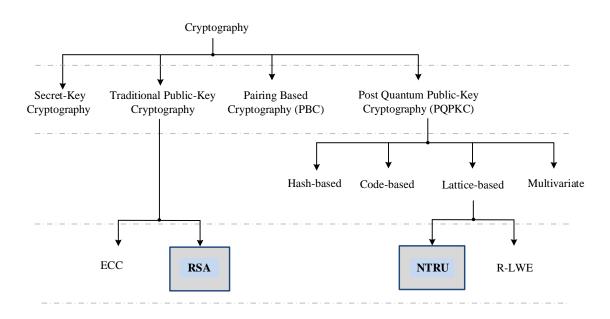

Figure 1. Scope of Research

After some generalizations, this algorithm has been shown to solve the remaining two mathematical problems underlying modern public key cryptography: the discrete logarithm problem, elliptic curve discrete logarithm problem and factorization problem,

Shor's algorithm can be executed only on a specialized machine known as a quantum computer. As seen from Table 1, no quantum computer capable of handling numbers anywhere close to those used in cryptography has been reported to be built so far. Nevertheless, the danger is real, and the rate of progress in quantum computing research is hard to predict. A short history of quantum computing is summarized in Table 1.

Table 1. Short History of Quantum Computing

| Date | Event                                                                       |  |  |  |

|------|-----------------------------------------------------------------------------|--|--|--|

| 1985 | David Deutsch came up with the idea of quantum logic gates.                 |  |  |  |

| 1994 | Peter Shor designed a quantum algorithm for factoring integers [3].         |  |  |  |

| 1996 | Lov Grover formulated a quantum algorithm capable of reducing the time      |  |  |  |

|      | necessary to break a secret-key cipher from 2n to 2n/2 operations.          |  |  |  |

| 1998 | First quantum computer built using 2 qubits                                 |  |  |  |

| 2000 | A 7-qubit quantum computer developed by Los Alamos National Laboratory.     |  |  |  |

| 2001 | IBM demonstrated Shor's Algorithm by factoring 15 using a Nuclear Magnetic  |  |  |  |

|      | Resonance quantum computer with 7 qubits.                                   |  |  |  |

| 2005 | The first qubyte was created by the Institute of Quantum Optics and Quantum |  |  |  |

|      | Information of the University of Innsbruck based on ion traps.              |  |  |  |

| 2006 | Scientists in Massachusetts established methods for controlling a 12-qubit  |  |  |  |

|      | system.                                                                     |  |  |  |

| 2007 | A Canadian startup, D-Wave, successfully demonstrated a 16-qubit quantum    |  |  |  |

|      | computer which could solve a Sudoku puzzle.                                 |  |  |  |

| 2011 | D-Wave Systems claimed developing a 128-qubit processor chipset.            |  |  |  |

| 2011 | Proof that a quantum computer can be made with a Von Neumann architecture   |  |  |  |

|      | (separation of RAM).                                                        |  |  |  |

| 2011 | Physicists at the University of Science and Technology of China in Hefei,   |  |  |  |

|      | factored 143 into prime factors 11 and 13 using just 4 qubits.              |  |  |  |

| 2013 | Google announced launching a "Quantum Artificial Intelligence Lab," holding |  |  |  |

|      | a 512-qubit quantum computer developed by D-Wave Systems.                   |  |  |  |

| 2013 | An international team of researchers led by Mike Thewalt of Simon Fraser       |

|------|--------------------------------------------------------------------------------|

|      | University in Canada were able to maintain the superposition states of qubits  |

|      | for an entire 39 minutes, thus breaking all previous records by a wide margin. |

|      | [8]                                                                            |

Arithmetic operations involved in traditional and post quantum PKC are computationally intensive and for hardware implementations, programmable logic inside FPGA is considered a natural candidate to speed up the computations using pipelining and parallelizing techniques. A lot of research has been done to build FPGA based coprocessors for traditional PKC [4], [5], [6], [7].

These designs mostly focus on improving the performance of the hardware but they are less flexible. Since 2000, there is a growing trend to use HW/SW codesign techniques to build cryptographic applications. These designs offer the flexibility of the software but also provide the performance of the hardware. Initially, these implementations were plagued with communication overhead problems between the software and hardware. With technological advancements, vendors now provided development environments where dedicated paths are provided between processor and reconfigurable logic to minimize latency during data communication and maximize performance. Specialized embedded resources allow configurable arithmetic units inside programmable logic to implement cryptographic operations effectively. There are relatively few HW/SW codesigns for RSA because RSA requires large operand sizes to provide acceptable security. Arithmetic operations involved in RSA are complex and time consuming. It requires high speed interfaces to overcome the communication overheads associated with working operations on large operands. However, the algorithm does not involve

technical jargon as other public-key cryptosystems. Key generation phase and different exponentiation schemes can be implemented in software, while the actual algorithm that involves modular multiplication can be sped up in hardware. Modular multiplications of large numbers in RSA are more suited for a hardware and fast implementations in hardware can be realized through pipelining the design. On the other hand, there are a lot of HW/SW codesign implementations for ECC [9], [4], [10], [5], [6], [7] because ECC requires smaller key sizes to provide equivalent security as RSA. The scope of this research is to use one of most promising HW/SW platforms that provides exceptional performance in all categories i.e. software, communication interfaces and hardware. We try to improve the overall system-level performance of RSA. This includes minimizing the communication overhead, equivalent performance to a hardware coprocessor while retaining the flexibility of the software. We will provide a generic model of a HW/SW codesign that will be applicable to traditional PKC but our focus is to apply all the techniques to one of the promising branches of post-quantum PKC i.e. Lattice based cryptography. The primitive cryptographic operations involved in one of the selected lattice based algorithms (NTRU) are multiplications and modular reductions. The basic operations involved in modular exponentiation of RSA are also modular multiplications and reductions. Therefore, the design methods and techniques that we deployed for HW/SW codesign implementations of RSA are also beneficial in the implementation of NTRU.

#### 1.2 Motivation and Research Goals

There is a strong need to analyze and implement post-quantum public key schemes in a generic way (i.e., supporting different key sizes) using at least the following platforms:

- 1. Microprocessors (software)

- 2. Microcontrollers (software)

- 3. FPGAs (Xilinx, Altera, and Microsemi families) (hardware)

- 4. ASICs (hardware)

- 5. Systems on chip (e.g., Xilinx ZYNQ) (software/hardware codesign).

In this section, we discuss our major research goals and how they would help in benchmarking this emerging class of post-quantum public-key cryptosystems.

The scope of our research is to contribute in the area of efficient and comprehensive benchmarking of post-quantum public-key schemes. We focus on developing a generalizable framework for hardware and HW/ SW codesign based approaches that can be applied to post quantum cryptosystems. For HW/SW codesign, RSA is considered as a test case and complete system integration is done using RSA to analyze the feasibility of HW/ SW codesign on Zynq SoC Platform. RSA is still one of the most widely used cryptosystems in real applications. As it is quite computationally intensive, using it for HW/SW codesign could also serve to optimize the overall performance of RSA while still retaining the flexibility offered by software. We believe that our HW/SW codesign techniques are generic enough to be applied to traditional and post quantum PKC.

For hardware benchmarking of post-quantum public-key algorithms, we use the same PQC Hardware Application Programming Interface (API) to contribute in the direction of standardization of these algorithms for future developers.

#### 1.2.1 Post-Quantum Cryptosystems (PQC)

If a quantum computer with a sufficient number of qubits was ever built, it would easily break all current NIST standards in the area of public-key cryptography, including algorithms protecting majority of the Internet traffic, such as RSA, ECC, DSA, and Diffie-Hellman. All traditional methods of dealing with growing computational capabilities of potential attackers, such as increasing key sizes, would be futile. This is because the execution time of the Shor's algorithm [3] increases only as a cube, k<sup>3</sup>, of the key size, k (i.e., the Shor's algorithm runs in the polynomial time on a quantum computer).

In order to protect cryptography and secure communications as we know it, and prevent it from the complete collapse, when the first sufficiently large quantum computer is developed, a decisive and well-coordinated action is required right now.

Since no clear and reliable replacement for current public key standards is in site, a substantial amount of time is needed in order to

- Study, improve, and optimize the most promising families of cryptographic algorithms resistant to quantum attacks

- Build confidence among members of the cryptographic community and end users

- Improve the usability, and

Develop efficient implementations in multiple domains, resistant to sidechannel attacks.

#### 1.2.2 Hardware/ Software Codesign

We have selected HW/ SW codesign as one of the chosen design strategies to implement post quantum cryptosystems. With the advent of quantum computers in a not-too-distant future when the cryptography protecting virtually all e-mails, medical and financial records, and online transactions will be rendered obsolete by quantum computing, it is imperative to be prepared as soon as possible. HW/SW codesigns offer a balance between performance and efficiency with a substantial reduction in overall development time. This will greatly help in early investigation, selection and benchmarking of PQC without the delays of fine-tuned pure hardware implementations.

# 1.2.3 Zynq All Programmable System on Chip

Xilinx, Altera and Microsemi hold more than 90% of the FPGA market share. All big players in market are now incorporating processors along with reconfigurable logic in their System on Chip (SoC) solutions. ARM, being the biggest player in processor market is deployed in most of the SoC designs. Xilinx and Altera have spent a lot of time and investment into these SoC based development environment. It includes developing programming/ debugging tools for both processor and programmable logic, and ARM bus standard compatible IPs to work on for the next decade.

Xilinx offered Zynq SoC platform that is specifically designed to optimize overall system-level performance. It includes high performance dual-core processors to speed up the software portion. High performance interfaces between PS and PL allow access to L1/L2 caches of the processor, thus providing high data bandwidth and reduced

latency. PL consists of reconfigurable logic based on Artix-7 that has support for highspeed arithmetic.

Zynq is particularly an ideal platform for research on Post Quantum Cryptosystems (PQC). As Industry is realizing that advent of quantum computers will soon represent a practical threat. It will take decades to deploy post quantum resistant algorithm and schemes. These schemes require proven cryptanalysis and performance evaluation across multiple platforms. This situation highlights the importance of development time of algorithms under investigation. Zynq SoC platform provides drastic improvements in development time. It allows us to implement software, hardware or HW/ SW codesigns using the same platform. Thus, covering all three aspects i.e. software, hardware and HW/SW for PQC.

Zynq SoC platform provides the best overall solution when compared to ASIC, ASSP and 2 chip solutions. It allows high performance due to industry standard ARM processor, latest Artix-7 based programmable logic and high-performance interfaces between PS and PL. It has a low power consumption due to the fact that both PS and PL are mapped onto the same chip. It provides flexibility in terms of scalability, portability, re-programmability and ease of partitioning. It has a very low risk and reduced time to market due to HLS based solution. On the other hand, ASIC based solutions provide excellent performance, reduced power consumption and unit cost but lack flexibility and scalability. They have huge risk of failure and time to market is quite substantial. ASSP based solutions lack flexibility and 2 chip solutions have higher power consumption, unit cost and communication overhead.

Table 2. Comparison with Alternative Solutions (Source: Xilinx Video Tutorials)

|                                 | ASIC | ASSP | 2 Chip<br>Solution | Zynq |

|---------------------------------|------|------|--------------------|------|

| Performance                     | +    | +    |                    | +    |

| Power                           | +    | +    | -                  | +    |

| Unit Cost                       | +    | +    | -                  |      |

| Total Cost of<br>Ownership      |      | +    | +                  | •    |

| Risk                            | -    | +    | +                  | +    |

| Time to Market                  | _    | +    | +                  | +    |

| Flexibility                     | -    | -    | +                  | +    |

| Scalability                     | _    |      | +                  | +    |

| positive, — negative, ■ neutral |      |      |                    |      |

# 1.2.4 Research Questions & Challenges

Some challenges in the overall evaluation of these algorithms were

- How to partition the design effectively between software and hardware? Where

is the best sweet spot for optimal results in terms of performance and flexibility

trade-off? What criteria to take into account to determine the point of partition?

Although, transferring complete logic to hardware will result in faster

implementation, how large is the price in terms of flexibility and development

time.

- Can we develop a framework to assist in reliable ranking of candidates from post quantum cryptosystems using these approaches? Ranking new candidates to a new standard based on RTL implementations would be too time consuming. There are multiple parameters, algorithms and key sizes so it would be faster and efficient to use codesign approach to assist in the comprehensive analysis. At the same time, fine-tuned hardware implementation provides more detailed insight about the techniques that can be used to optimize their performance on these platforms.

#### 2 BACKGROUND

In this chapter, we cover the necessary background to guide the reader towards understanding the core details of RSA and HW/SW codesign based topics. We start from the concepts behind RSA-based cryptosystems and the arithmetic involved in implementing RSA.

# 2.1 Cryptographic Algorithms

#### 2.1.1 RSA

The RSA cryptosystem, named after its inventors Ron Rivest, Adi Shamir, and Len Adleman [2] was the first public key cryptosystem and is still one of the most important ones. RSA is a public and private key based cryptosystem. Public key of the receiver is used to encrypt messages. The receiver then uses the private key to decrypt the ciphertext generated by the sender. The phases involved in RSA can be divided into three categories.

# **Key Generation**

Let P and Q be two distinct large prime numbers. The product of these two primes is called the modulus N. The security of RSA lies in the difficulty of factoring the modulus N. The Euler's function is given by

$$\varphi(N) = (P-1)(Q-1)$$

An integer e also called the public key exponent is typically selected to be relatively small. e.g.,  $e=2^{16}+1$ . From the efficiency point of view, it also helps, if e has a small

number of 1's in its binary representation. The public key consists of the modulus N and the public key exponent e. Later during decryption, a private key exponent d is required which is computed as

$$d = e^{-1} \pmod{\varphi(N)}$$

The public key exponent along with the modulus N are published. The private key exponent d and both prime numbers P and Q are kept secret. The encryption and decryption described below are performed using large k-bit integers typically larger than 1024 bits to ensure security.

#### **Encryption**

The ciphertext is obtained by encrypting the message with the public key as follows

$$c \equiv m^e \pmod{N}$$

# **Decryption**

The message can be decrypted using the ciphertext and the private key as follows

$$m \equiv c^d \pmod{N}$$

Decryption involves an exponent d and is usually slower than encryption in RSA. Once the modulus N, e and d are generated, RSA encryption/decryption is based on modular exponentiation, which can be performed using successive modular multiplications. To improve overall performance of encryption and decryption, the key lies in efficiency of the underlying modular multiplications.

## **2.1.1.1 Montgomery Modular Multiplication (MMM)**

Montgomery multiplication [22] is commonly used when large number of multiplications are to be performed with the same modulus M, i.e., in modular exponentiation. To keep the products from growing after each multiplication, reduction

modulo M has to be performed at each step, which slows down the whole process. Montgomery multiplication allows us to compute products without reduction modulo M as it replaces division by M with division by a power of 2, which can be accomplished by a shift operation.

```

Algorithm 1 Montgomery Modular Multiplication without final subtraction

```

```

1: Setting: A = (a_l \cdots a_1 a_0)_2 where a_i \in [0, 2M - 1], B = (b_l \cdots b_1 b_0)_2 where b_i \in [0, 2M - 1], M = (m_{l-1} \cdots m_1 m_0)_2 where \gcd(M, 2) = 1

2: Input: A, B, M

3: Output: MP(A, B, M) = S = ABR^{-1} \pmod{M},

4: S \leftarrow 0

5: for i \leftarrow 0, l + 1 do

6: q_i \leftarrow S_0 \oplus a_i \cdot b_0,

7: S \leftarrow (S + a_i \cdot B + q_i \cdot M)/2

8: end for

9: return S where S = (s_{l+1} \cdots s_1 s_0)

```

The Montgomery product MP computed because of Montgomery multiplication is in the form of  $S = ABR^{-1} \pmod{M}$ , where A and B are the multiplication arguments, M is the modulus, S is the final result, and  $R = 2^n$ , where n is equal to the number of bits of M.

The additional overhead involved in MMM is the conversion of operands to Montgomery domain as shown below. The conversion can be performed by computing a Montgomery product (MP) given below:

$$X' = MP(X, 2^{2n} \pmod{M}, M)$$

$$= X \cdot 2^{2n} \cdot 2^{-n} \pmod{M}$$

$$= X \cdot 2^{n} \pmod{M}$$

Once the final result is computed, a conversion back from the Montgomery domain is performed as follows:

$$S = MP(S', 1, M)$$

$$= (S \cdot 2^{n}) \cdot 1 \cdot 2^{-n} \pmod{M}$$

$$= S \pmod{M}$$

# Montgomery Multiplication based on Orup's Algorithm (OMP)

In 1995, Orup proposed a quotient pipelining technique shown in algorithm 2, for implementing Montgomery multiplication [23]. His algorithm, shown below, produces the final result of multiplication in the form of  $S = ABR^{-1} \mod M$ , where A and B are the multiplication arguments, M is the modulus, S is the final result, and  $R = 2^n$ , where n is equal to the number of bits in M.

The modulus M, used in Montgomery multiplication for the reduction part, is replaced by  $\widetilde{M}$  (called *Mwave* in all subsequent sections) and is given by

$$\widetilde{M} = (M' \mod 2^{k(d+1)}) M$$

# Algorithm 2 Modular Multiplication with Quotient Pipelining

- 1: **Setting**: radix :  $2^k$ ; delay parameter : d = 1; no. of blocks: n; multiplicand : A; multiplier : B; modulus: M, M > 2, gcd(M, 2) $=1, (-MM' \mod 2^{k(d+1)}) = 1, \tilde{M} = (M' \mod 2^{k(d+1)})M,$  $4M < 2^{kn} = R, \ M'' = (\tilde{M}+1)/2^{k(d+1)}, \ 0 \le A, \ B \le 2\tilde{M}, \ B = \sum_{i=0}^{n+d} (2^k)^i b_i, \ b_i \in 0, 1, ..., 2^k - 1, \ \text{and} \ b_i = 0 \ \text{for} \ i \ge n.$  2: **Input**: A, B, M''

- 3: Output: OMP(A, B, M)= $S_{n+d+2} = ABR^{-1} \mod M$ , where  $0 \le S_{n+d+2} \le 2\tilde{M}$

- 4:  $S_0 \leftarrow 0; q_{-d} \leftarrow 0; ...; q_{-1} \leftarrow 0$

- 5: for  $i \leftarrow 0, n+d$  do

- $q_i \leftarrow S_i \mod 2^k$

- $S_{i+1} \leftarrow S_i/2^k + q_{i-d}M'' + b_iA$

- 8: end for

- 9:  $S_{n+d+2} \leftarrow 2^{kd} S_{n+d+1} + \sum_{j=0}^{d-1} q_{n+j+1} 2^{kj}$

- return S<sub>n+d+2</sub>.

#### 2.1.2 Lattice-Based Cryptosystems

There are three major families of post-quantum cryptosystems [11]:

- 1. Code-based cryptosystems, such as the McEliece and Niederreiter schemes

- 2. Lattice-based cryptosystems, such as Ring-LWE (Ring-Learning with Errors) and NTRU, and

- 3. Multivariate cryptosystems, such as Rainbow and HFE.

Their underlying mathematical problems, which at least partially determine the security of these schemes, and the best algorithms for solving these problems are summarized in Table 3.

Lattices were first introduced and studied by famous mathematicians Joseph Louis Lagrange and Carl Friedrich Gauss in the 18<sup>th</sup> and 19<sup>th</sup> century. The capability to create a public key cryptosystem based on these mathematical structures was discovered by Ajtai in 1997 [12].

Some lattice problems have been proven to be average-case hard, which is a property beneficial for cryptography. There are, however, methods for lattice reduction, which aim to convert an average basis for the algorithm to a good basis. A popular such algorithm is the LLL (Lenstra—Lenstra—Lovász) algorithm, which is an efficient scheme for giving an output of an almost reduced lattice basis in polynomial time. The LLL algorithm thus led many to believe that the lattice-problem could actually become an easy problem in practice.

Table 3 The Underlying Security Problem and the Best Known Algorithms for Solving this Problem

|                                                     | Code-based                                                                                                                                                                               | Lattice-based                                                                                                               | Multivariate                                                                                                                                                                      |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Publication year of the first algorithm             | 1978                                                                                                                                                                                     | 1997                                                                                                                        | 1988                                                                                                                                                                              |

| Name of the first<br>proposed algorithm             | McEliece<br>public key<br>encryption                                                                                                                                                     | Ajtai Dwork<br>public key<br>encryption                                                                                     | Matsumoto-Imai (C*) public key encryption and signature schemes                                                                                                                   |

| Underlying<br>mathematical<br>problems              | Hardness of decoding in a random linear code. Exponential indistinguishability of Goppa codes. Code equivalence problem.                                                                 | Lattice problems: Shortest Vector Problem (SVP). Closest Vector Problem (CVP). Shortest Independent Vectors Problem (SIVP). | MQ (Multivariate Quadratic) problem = solving a set of quadratic equations over a finite field                                                                                    |

| Best algorithms for solving the underlying problems | CSD (Computational Syndrome Decoding). CF (Codeword Finding). Complete Decoding. Goppa Bounded Decoding. Information Set Decoding. Structural attacks (e.g., recognizing code structure) | LLL (Lenstra,<br>Lenstra, Lovasz,<br>1982), with<br>extensions by<br>Schnorr 1987                                           | Linearization Equations. LazardFaugère System Solvers (including Gröbner Bases, XL, F4, F5). Differential Attacks. Rank Attacks (including MinRank). Distilling Oil from Vineger. |

Today, despite the LLL algorithm, the lattice problem still seems intractable for sufficiently large lattices. No significant improvements in the algorithms solving the general cases of the lattice problems were reported since 1980s. The major advantages of the entire family are strong security proofs based on worst-case hardness, efficient implementations, and simplicity.

Table 4 Major Algorithms of Lattice-based cryptosystems and their Publication Dates

| Cryptographic Scheme         | Algorithms                                                                                                                                     |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Encryption                   | Ring-LWE (Ring-Learning with Errors, 2005-2008),<br>NTRUEncrypt (1998),<br>GGH: Goldreich, Goldwasser, Halevi (1997)*,<br>Ajtai-Dwork (1997)†, |

| Signature                    | NTRUSign with perturbation (2005), Lyubashevsky-Micciano (2008), GPV: Gentry, Peikert, Vaikuntanathan (2008) NTRUSign (2003)*, GGH (1997)*,    |

| Identification schemes       | Micciancio-Vadhan (2003),<br>Lyubashevsky (2008)                                                                                               |

| Identity Based<br>Encryption | GPV: Gentry, Peikert, Vaikuntanathan (2008)                                                                                                    |

| Oblivious Transfer           | PVW: Peikert, Vaikuntanathan, Waters (2008)                                                                                                    |

Implementing majority of cryptosystems from this family does not involve multiprecision arithmetic. Only additions and multiplications mod q are used, where q can be a power of 2. High level of parallelization can be also used to speed up the implementations on multiple platforms. Public key size can be reduced by using restricted classes of lattices, such as cyclic lattices.

A practical scheme, without a supporting security proof, called NTRU, is likely to be the only representative of this family currently used in practice. In particular, this scheme been already standardized by IEEE and ANSI. For other schemes, still more research and confidence is required.

One of the small weaknesses of the entire family is a non-zero probability of decryption errors. This probability can be made very small with an appropriate choice of

parameters (e.g. 1%). Any encryption scheme can be also combined with error correction codes to reduce error probability to undetectable levels.

Table 5. Public Key Sizes for Lattice-based algorithms for selected Security Levels.

| 112-bit             | 128-bit             | 192-bit             | 256-bit             |

|---------------------|---------------------|---------------------|---------------------|

| NTRU: 552 B         | NTRU: 604 B         | NTRU: 815 B         | NTRU: 1022 B        |

| $(N=401, q=2^{11})$ | $(N=439, q=2^{11})$ | $(N=593, q=2^{11})$ | $(N=743, q=2^{11})$ |

| [EBACS]             | [EBACS];            | [EBACS]             | [EBACS]             |

|                     | LWE: 140 KB         |                     |                     |

<sup>\* 1</sup> KB = 1024 bytes

## 2.1.3 NTRUEncrypt Cryptosystem

NTRUEncrypt is a polynomial ring-based public-key encryption scheme that was first introduced at Crypto'96. The first formal paper describing this scheme was published at ANTS III [13]. In 2008, an extended version of this algorithm was published as the IEEE 1363.1 Standard Specification for Public Key Cryptographic Techniques Based on Hard Problems over Lattices [14]. Within the standard, the described algorithm is called Short Vector Encryption Scheme – SVES. Since the core of this algorithm is known in the academic literature as NTRUEncrypt, we will refer to the full cryptosystem as NTRUEncrypt SVES. Further standardization efforts included the Financial Services Industry Standard ANSI X9.98-2010 [15] and the Consortium for Efficient Embedded Security standard, EESS #1 [16]. Additionally, an Internet Draft proposing the use of NTRUEncrypt in the handshake for the Transport Layer Security (TLS) v1.3 has been developed in 2016 [17].

<sup>†</sup> NTRU: public key size = N·log<sub>2</sub> q

The recent renewed interest in NTRU is at least partially driven by its presumed resistance to any efficient attacks using quantum computers. In Feb. 2016, NIST has published a draft report [18] and announced its plans of starting the standardization effort in the area of post-quantum cryptography [19]. This effort is likely to last years and result in an entire portfolio of algorithms capable of replacing current public-key cryptography schemes. This initial announcement was followed by the official Call for Proposals and Request for Nominations for Public-Key Post-Quantum Cryptographic Algorithms, issued in Dec. 2016 [20]. As a part of this standardization process, fair and efficient benchmarking of PQC algorithms in hardware and software becomes a necessity.

NTRUEncrypt has three major parameters (N, p, q) such that

- a) N is prime,

- b) p and q are relatively prime, gcd(p,q)=1, and

- c) q is much larger than p

For the purpose of efficiency p is typically chosen to be 3, and q as a power of two. The scheme is based on polynomial additions and multiplications in the ring  $R=Z[X]/X^N-1$ . We use the "\*" to denote a polynomial multiplication in R, which is the cyclic convolution of the coefficients of two polynomials. After completion of a polynomial multiplication or addition, the coefficients of the resulting polynomial need to be reduced either modulo q or p. The key creation process also requires two polynomial inversions, which can be computed using the Extended Euclidean Algorithm. During the key generation, the user chooses two random secret polynomials  $F \in R$  and  $g \in R$ , with so called "small" coefficients, i.e., coefficients reduced modulo p (typically

chosen to be in the integer range from -1 to +1, and thus limited to -1, 0, and 1. The private key f is computed as f=1+pF. The public key h is calculated as

$$h = f^{-1} * g \cdot p \text{ in } (Z/qZ)[X]/(X^N - 1)$$

The message m is assumed to be a polynomial with "small" coefficients. The ciphertext is computed as

$$e = r * h + m \pmod{q}$$

where  $r \in R$  is a randomly chosen polynomial with "small" coefficients.

The decryption procedure requires the following three steps:

- 1) calculate  $f * e \pmod{q}$

- 2) shift coefficients of the obtained polynomial to the range [-q/2, q/2),

- 3) reduce the obtained coefficients mod p.

# 2.2 Technology

#### 2.2.1 Hardware/Software Codesign Platforms

In this section, we will provide information on alternative HW/ SW codesign platforms other than Zynq SoC.

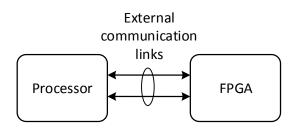

1. Discrete FPGA-Processor Combination: In this scenario, processor and FPGA exist as physical separate components. The major disadvantage of this platform is the huge overhead of inter-chip communication.

Figure 2. Discrete FPGA-Processor Combination

2. Processors inside FPGA: This category is one of the most efficient ways to implement a HW/ SW codesign system. The processors inside the FPGA are divided into two categories i.e. soft-core and hard-core processors.

#### a) Soft-core Processors

- a. PicoBlaze: PicoBlaze is the designation of a series of three free soft processor cores from Xilinx for use in their FPGA and CPLD products. It is based on an 8-bit RISC architecture and can reach speeds up to 100 MIPS on the Virtex-4 FPGA family.

- b. MicroBlaze: The MicroBlaze is a soft microprocessor core designed for Xilinx FPGAs from Xilinx. As a soft-core processor, MicroBlaze is implemented entirely in the general-purpose memory and logic fabric of Xilinx FPGAs.

- c. NIOS-II: Nios is a soft-core embedded processor from Altera that includes a CPU optimized for SoC integration. This configurable, general-purpose RISC processor can be combined with user-defined logic and programmed into Altera FPLDs. Nios supports both 16-and 32-bit variants with 16-bit instruction set.

- d. OpenSparc: OpenSPARC is an open-source hardware project started in December 2005. The initial contribution to the project was Sun Microsystems' register-transfer level (RTL) Verilog code for a full 64-bit, 32-thread microprocessor, the UltraSPARC T1 processor.

- e. **LEON3**: The LEON3 is a synthesizable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture. The full source code is available under the GNU GPL license, allowing free and unlimited use for research and education.

- f. **Dalton 8051**: The Intel 8051 is an 8-bit micro-controller. This micro-controller is capable of addressing 64K of program and 64K of data memory. The implementation is written in Synthesizable VHDL and models the actual Intel implementation rather closely, e.g., it is 100% instruction compatible.

- g. ARM Cortex-M1: The ARM Cortex-M1 processor is the first ARM processor designed specifically for implementation in FPGAs. The Cortex-M1 processor targets all major FPGA devices. The Cortex-M1 processor enables cost savings through rationalization of software and tools investments across multiple projects spanning FPGA, ASIC and ASSP, plus greater independence through use of an industry-standard processor.

- **b) Hard-core Processors**: These processors are permanently embedded at fixed location inside FPGA but have an advantage that they can run at a much higher frequency and provide performance benefits.

- a. IBM PowerPC: The single hard processor to be discussed is the IBM PowerPC, which was included as a hard processor in the Virtex-II Pro and subsequently in a subset of Virtex-4 and Virtex-5 FPGAs. Each of these FPGAs includes either one or two PowerPC (PPC) units.

- b. **ARM Cortex M3**: This processor is available as a hardcore inside Microsemi SmartFusion2 SoC: The ARM Cortex<sup>TM</sup>-M3 32-bit processor has been specifically developed to provide a high-performance, low-cost platform for a broad range of applications, including microcontrollers, automotive body systems, industrial control systems and wireless networking. With a balance between size and speed, Microsemi's free Cortex-M3 processor is included as a hard resource in Microsemi's SmartFusion2 and SmartFusion SoC FPGA families.

- c. ARM Cortex A9: This dual core processor is available in Altera Cyclone V, Arria V, Arria 10 and Cyclone V FPGAs and provides the equivalent performance as Zynq SoC 7020 EPP platform.

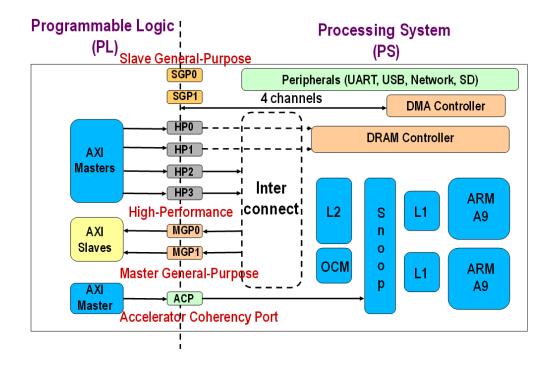

## 2.2.2 Hardware/Software Codesign with Xilinx Zynq SoC

In this section, we will discuss all building blocks required to construct HW/ SW codesign using Zynq SoC platform. It is critical to rationally decide about the components of the codesign effort because later on, they have a huge impact on the performance and area utilization of your overall design.

#### **Platform**

Typically, implementations are classified into software and hardware implementations. There are very few high-speed implementations done using HW/SW codesign approach. These available implementations largely suffer from low-performance processors and communication overhead between the processor and hardware accelerator. Having a processing system (PS) and programmable logic (PL) on a single chip greatly reduces the delays between both parts. For an efficient system, it is imperative to perform well in all areas, i.e., software, communication interface and hardware side. Our design platform uses Xilinx Zynq SoC 7020 Extensible Processing Platform (EPP). This chip is specifically designed for HW/SW cosdesign applications in mind and optimizes the design in all three domains of a codesign system.

#### **Processing System (PS)**

Zynq SoC platform provides dual core ARM Cortex-A9 microprocessor core with CPU frequency up to 1 GHz. Zynq has 32 KB of L1 data and instructions caches, 512 KB of L2 cache and 512 MB DDR3 memory. This ensures high speed implementation of the software side of the design.

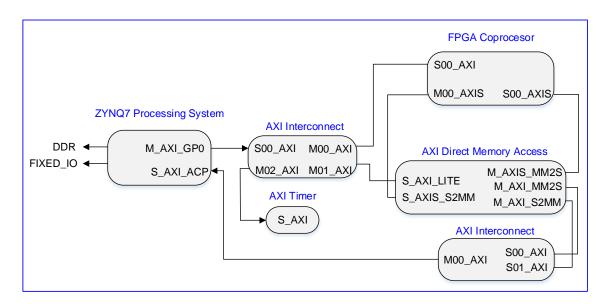

Figure 3. Zync SoC Z7020 platform with interface between PS and PL

# Programmable System (PL)

Zynq SOC platform provides a reconfigurable logic equivalent to Artix-7 FPGA. It consists of 85K Logic cells (Slices). Additionally, it offers embedded resources i.e. 140 BRAMs (36kbit each) and 220 DSP blocks.

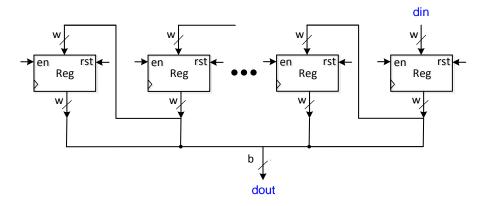

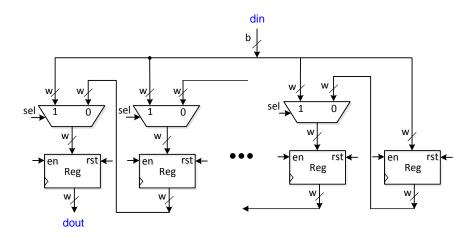

## Serial in Parallel out (SIPO) and Parallel in Serial out (PISO) Components:

SIPO and PISO components are a part of input and output interface. SIPO takes in "n" w-bit wide data words serially and convert them into one b-bit wide output word that is n\*w-bit wide. On the other hand, PISO takes in parallel input (b = n\*w-bit wide) and converts it w-bit words that is serially transmitted out.

Figure 4. SIPO in Input interface of Coprocessor

Figure 5. PISO in Output interface of Coprocessor

# **Choice of Processor (PS) Ports for Communications**

There are three major types of PS ports available for communication with PL using AXI interface.

# General Purpose (GP) port

In GP interface, coprocessor acts as a slave. It attaches the coprocessor to a general purpose coprocessor port on the PS. Here, coprocessor is considered as a register interface with a memory mapped address. This is the simplest way of attaching the

coprocessor. This approach is particularly beneficial for application that does not require high bandwidth or large amount of data transfer.

## **High Performance Port (HP)**

The second method of attaching the coprocessor is via a high performance port. HPP provides high bandwidth port b/w PL based accelerator and either the DDR memory or the OCM memory associated with PS. The coprocessor requires the DMA engine to move the data between its local buffer and PS DRR or OCM memory. The on-chip memory (OCM) has an equivalent latency as that of L2 cache and is much lower latency than DDR memory. Thus, for latency reasons, if the data set fits in the OCM memory, then it is best to use the OCM rather than the DDR memory.

# **Accelerator Coherency Port (ACP)**

ACP port interface allows direct memory transfer between PL and L1 cache of PS. This method provides the fixed low latency path and high data bandwidth for short bursts. However, it provides best results when the data can be accommodated in caches.

There are four high performance ports that provide high bandwidth communication but have a higher latency than ACP port interface. We implemented our RSA design based on both ACP and HP0 interfaces and reported results based on ACP port interface because they are slightly better than HP0 interface. Our design connects the PS to the hardware accelerator through DMA engine to stream data in burst mode.

Figure 6. Processor Ports for Communication between PS and PL

## **Choice of Communication Interface**

There are many competing Bus standards used the industry. Most popular standards are AMBA V3, V4 from ARM Ltd, Coreconnect from IBM, Wishbone from SiliCore Corp. and Avalon from Altera. Our design utilizes AMBA Advanced Bus Interfaces Extensible Interface 4 (AXI4), targeted at high performance, high clock frequency systems.

Table 6. Communication Interface Options in Zync SoC

| Bus configurations for existing bus standards |                   |                       |                       |  |  |  |  |

|-----------------------------------------------|-------------------|-----------------------|-----------------------|--|--|--|--|

| High-performance Bus shared bus               |                   | Peripheral shared bus | Point-to-point<br>bus |  |  |  |  |

|                                               |                   |                       |                       |  |  |  |  |

| AMBA v3                                       | AAHB              | APB                   |                       |  |  |  |  |

| AMBA v4                                       | AXI4              | AXI4-Lite             | AXI-Stream            |  |  |  |  |

| Coreconnect                                   | PLB               | OPB                   |                       |  |  |  |  |

|                                               |                   |                       | Point to point        |  |  |  |  |

| Wishbone                                      | Crossbar topology | Shared topology       | topology              |  |  |  |  |

| Avalon                                        | Avalon-MM         | Avalon-MM             | Avalon-ST             |  |  |  |  |

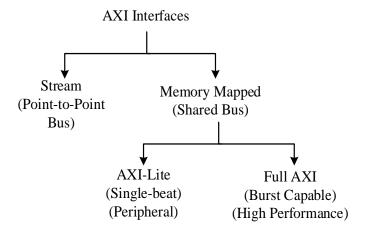

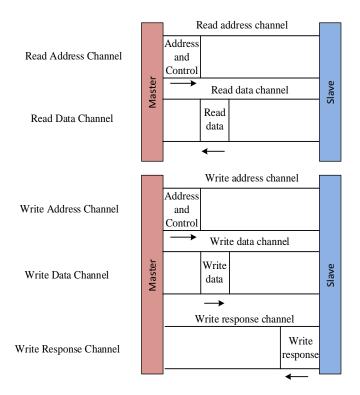

# 2.2.3 Type of AXI Interfaces in Zynq SoC

AXI is a part of ARM's AMBA bus. Zynq SoC platform provides either a memory mapped or stream interface to connect PS to PL.

Figure 7. AXI Interfaces

## 2.2.3.1 AXI4-Lite Interface

AXI4-Lite interface is a part of memory mapped interface with no burst capability. This interface is generally used to connect peripheral that have low performance requirement.

## 2.2.3.2 AXI Full Interface

AXI Full is the memory mapped interface that allows you to have the burst capability and is typically used for high performance peripherals.

Figure 8. AXI-Lite Interface

Figure 9. AXI Full Interface

# 2.2.3.3 AXI-Stream Interface

AXI-Stream interface is not a shared bus interface and is generally between one master and slave. Therefore, it is called a point to point bus interface.

Figure 10. AXI Stream Interface

#### 2.2.4 **AXI DMA**

The coprocessor requires DMA transfer to move the data between its local buffer and the L1/L2 data caches. Once the data is ready for processing, A9 processor signals the coprocessor via the slave port that it may begin processing the data. The communication includes the address of the data. The coprocessor initiates a DMA transfer from the memory, in this case, the L1/L2 cache to its local buffer. The coprocessor processes the data and returns the results in the 2nd buffer. The coprocessor initiates a DMA transfer from the buffer to the memory, L1/L2 cache. Finally the coprocessor signals the A9 processor that the data processing has been complete. The processor may then use the data passed to it.

## 2.2.5 Embedded FPGA Resources

Practically all FPGA vendors incorporate in modern FPGAs, apart from basic reconfigurable logic resources, also embedded resources, such as large memory blocks, DSP units, microprocessors, etc. Improved hardware performance and good balance in terms of the overall FPGA utilization can be achieved with the use of these embedded elements for multiple applications, such communications, digital signal processing, and scientific computing.

#### **2.2.5.1 DSP Units**

Xilinx Virtex 5 FPGAs include DSP48E units. Each unit has a two-input multiplier followed by multiplexers and a three-input adder/subtractor/accumulator. The unit can be configured as a 25x18 multiplier and/or 48-bit adder with up to three inputs. The third input of an adder can be used only when multiple DSP units are cascaded and an adder output of one DSP unit is connected to an adder input of an adjacent DSP unit.

The DSP unit of the Stratix III FPGAs consists of four subunits units (called DSP\_18s) and a total of eight 18x18-bit multipliers. Two neighboring 18x18 multipliers share a 37-bit adder. The outputs of two 37-bit adders are fed to second stage Adder/Accumulator. Xilinx Spartan 3 and Altera Cyclone II contain only embedded multipliers. Spartan 3 devices support 18x18 signed multiplication. Cyclone II devices support 9x9 and 18x18 multiplication for signed and unsigned numbers.

Figure 11. DSP48 inside Zync SoC Z7020 and Latency selection to operate at 400 MHz

## 2.2.5.2 Block Memory

The Block Memory (BRAM) in Spartan 3 FPGAs has a size of 18 kbits, including parity bits. Word size is configurable in the range from 1 to 36 bits. The maximum word size is used in the configuration 512 x 36 bits. The block memory (BRAM) in Virtex 5 FPGAs can store up to 36 kbits of data. It supports two independent 18 kbit blocks (with the word size up to 18 bits), or a single 36 kbit memory block (with the word size up to 36 bits).

Altera devices have different capacity of basic embedded memory blocks. The low-cost Cyclone II family is based on 4 kbit blocks. The high-performance Stratix III family is less homogenous. It consists of two types of memory blocks i.e., 9 kbits and 144 kbits. All block memories have single-port and dual-port modes.

Figure 12. True Dual Port BRAM to store input data

Cryptographic algorithms have been demonstrated in the past to take advantage of these resources as well. For example, the fastest to date FPGA implementation of the Montgomery multiplication, a major building block of public key cryptographic algorithms, such as RSA, have been demonstrated using DSP units in Virtex 5 FPGAs [21].

#### 3 SURVEY OF PREVIOUS WORK

The gap between performance and flexibility can be narrowed down through an efficient HW/SW codesign system. To develop such an environment, all aspects of software, hardware and interface between the software and hardware for communication should be taken care of. HW/SW co-design allows the designer to partition the design into hardware and software to aim for the best of both worlds. The flexibility and short development time of software is combined with performance and low-power/low energy consumption of hardware.

This chapter covers the previous work on HW/SW implementations of RSA, currently available implementations of Lattice based cryptosystems, existing coprocessor designs on RSA/ECC and HW/SW codesign platforms that are already used by researchers.

# 3.1 HW/ SW Codesign Implementations of RSA

Public-key cryptosystems such as RSA have been widely used to secure digital data in many commercial systems. Modular arithmetic on large operands used during modular exponentiation makes RSA computationally challenging. We highlight some of the attempts made to optimize RSA cryptosystem through HW/SW codesign.

Two variants of hardware/software co-design were presented by Simka et al. in [24] where they utilize one Montgomery multiplier (MM) coprocessor and two pipelined MM coprocessors respectively. The later implementation was aimed towards minimizing the average execution time during decryption in RSA. They used Altera's Nios RISC processor as their building block. Their data path is organized as a cascade chain of processing elements implemented using two approaches for

MMM operations to target scalability, i.e., carry save adder based and carry propagate adder based MMM units. The word length, number of words, and number of stages can be changed according to the required area of the implemented coprocessor and the required timings for MM computations or the security level for flexibility of the coprocessor.

Hani et al. in [25], proposed a private and public key cryptoprocessor. For RSA, the entire ME is performed in hardware. However they do not employ any techniques to make the design scalable by allowing different operand sizes or flexible by modular exponentiation algorithms and multiple security levels.

Isaad et al. in [26] proposed two implementations for HW/SW co-design based on right-to-left (R2L) algorithm for modular exponentiation. They propose a relatively flexible architecture for modular exponentiation (ME) using three implementation approaches, i.e SW only, with one MMM unit working sequentially, and two MMM units used in parallel to perform a ME. The second variant utilizes only one modular multiplier within a custom hardware. The execution time is further improved by parallel implementation of two multipliers based on Montgomery algorithm as their custom IP. The control of ME was done through MicroBlaze. Some data transfers are also handled by local memories to reduce data transfer overhead. The highest level of operation in all three schemes was MMM. However, in their proposed designs, the scalability of modular multiplier is achieved by allowing different operand sizes, modular exponentiation algorithms, or multiple security levels.

The implementations with the highest level operation being MMM offer higher flexibility but lower performance as compared to the other approach, i.e., to implement ME in hardware. To explore the best tradeoff between performance and flexibility, we intend to focus on multiple aspects. One of them is to allow support of multiple exponentiation algorithms i.e., R2L, L2R, sliding window. For highr flexibilility, handling of multiple operand sizes in the MMM unit, the capability to control the choice of ME algorithm form the software will be exploited.

The table below lists all noteworthy contributions on HW/SW codesign of RSA. The security level in all reported implementations is equivalent to 80-bit security. Except [26], all reported implementations use Left-to-Right algorithm for exponentiation.

Table 7. HW/ SW Codesign Implementations of RSA

Note: In the Flexibility/Scalability column, the parameters marked with \* are used for the

reported results

| Source                          | Flexibility/                                                                                                | Platf                                    | orm        | Area[LUTs/<br>LEs/Kgates, | Clk<br>Freq | Time<br>[ms] |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------|------------|---------------------------|-------------|--------------|

| Source                          | Scalability                                                                                                 | Device                                   | Processor  | RAMs,<br>DSP48]           | MHz         |              |

| Isaad,<br>2014 [26]             | 1 MM unit in HW, 2<br>MM units in<br>hardware*, ME<br>scheme: R2L/ Fixed<br>operand size: 1024-bit          | Xilinx<br>Virtex-5                       | MicroBlaze | 1848, 11, 22              | 62.5        | 22.25        |

| Uhsadel, 2012 <sup>3</sup> [27] | Multiple ME schemes:<br>L2R*, R2L, MPL <sup>1</sup> ,<br>BFR <sup>2</sup> / Fixed operand<br>size: 1024-bit | Xilinx<br>Virtex-4,<br>XC4VFX101         | 8051       | 27467, 0, 1               | 111         | 29.37        |

| Sakiyama,<br>2007 [6]           | ME scheme: only<br>binary-method/ Fixed<br>operand size:1024-bit                                            | Virtex-II<br>PRO,<br>XC2VP30             | 8051       | 49.5 Kgates,<br>6, 0      | 12          | 129.8        |

| Hani,<br>2006 [25]              | No Flexibility/ Fixed operand size: 1024-bit                                                                | EPLS40                                   | NIOS       | 12881 LEs,<br>0,0         | 66          | 31.9         |

| Simka,<br>2003 [24]             | 1 MM unit in HW, 2<br>MM units in<br>hardware*/ Operand<br>size: 1024*, 2048                                | Altera<br>APEX,<br>EP20K200E<br>FC484-2X | NIOS       | 2837 LEs,<br>N/A, 0       | 50          | 39           |

<sup>1</sup> Montgomery Powering Ladder, 2 Blinded Fault Resistant Exponentiation, 3 Highest level of operation implemented in hardware is ME

# 3.2 Previous HW/ SW Codesign Implementations on Traditional Public-Key Cryptography

The scope of this research is to develop a HW/SW codesign that offers the advantages of flexibility in software but also offers the performance comparable to hardware. An optimal HW/SW codesign is possible only if the designer looks at overall system-level integration. In this section, we will look at the existing coprocessor implementations in the field of public key cryptosystems that try to solve the underlying challenges of HW/SW codesign approach.